全球最多人使用的設計輸入方案

Cadence® OrCAD™ X Capture 線路圖輸入系統具有快捷、通用的設計輸入能力,為全球最廣受歡迎的設計輸入工具。它針對設計一個新的電子電路、修改現有的一個 PCB 的線路圖或者繪製一個 VHDL 模組的方框圖都提供了所需要的全部功能,並能迅速地驗證您的設計。

Cadence OrCAD X Capture 作為設計輸入工具,運行在 PC 平臺,用於 FPGA 、 PCB 和 Cadence® OrCAD™ PSpice® 設計應用中,是業界第一個真正基於 Windows 環境的線路圖輸入程式,易於使用的功能及特點已使其成為線路圖輸入的工業標準。

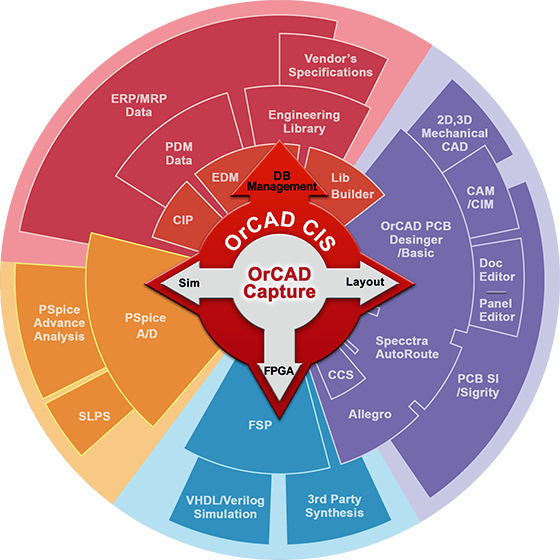

OrCAD 產品關係圖

1. 單一化的設計窗口

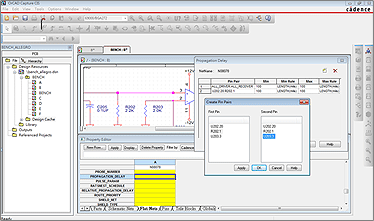

OrCAD™ X Capture 的電路設計可支持從最簡單到最複雜的平面或分層設計,並且可經由網路表連結Cadence® OrCAD™ PCB Editor、Cadence® Allegro® 或其它的 Layout 軟體來完成 PCB 設計;也整合了 PSpice 與 VHDL(NC Verilog) 的環境---提供您做類比與數位 (FPGA Design Flow) 前端設計平台。另外也可以配合 OrCAD PCB SI 與 Cadence® Allegro® SI 來解決高頻問題。

2. 利用 Windows 操作介面可以更方便的編輯與分享彼此的構想

OrCAD X Capture 利用 Windows 簡易操作的觀念,可用剪下、複製、貼上等等的特色來操作;也可以利用 Windows 的多重編輯方式來編輯兩個以上的電路圖或是由另外的檔案複製資料過來使用。

3. 支援廣大的 PCB 應用

OrCAD X Capture 可以支援 30 種以上 PCB Layout 軟體的網路表格式,包含 OrCAD PCB Editor、Allegro、Pads、PCAD 200X、Protel、Mentor Graphics BoardStation…等等。

4. 整合了 Cadence 其他系統程式來處理不同的需求

OrCAD X Capture 是 OrCAD PSpice、OrCAD PCB SI、OrCAD PCB Editor、Allegro 與 Allegro SI 的設計前台。透過網路表的連結,可利用它同時標示出彼此的關聯處 (cross-highlighting),也可直接作為測試的訊號源 (cross-probing)。而利用 Back Annotate 的功能,可將 Layout 序號或 Constraint Manager 的變化回饋到 Capture 的電路圖中。

5. 提供多重的 PLD 設計元件與方式

OrCAD X Capture 提供六種 PLD 使用電路圖的元件,包含 Xilinx、Altera、Actel、Lattice、Lucent 與 Atmel 六種 Vendor 的元件,這些元件允許您利用 OrCAD X Capture 來做為設計 PLD 的前台。

6. 可以利用 OrCAD X Capture 來完成不同的模擬並提供廣大的 PCB 網路表格式

可以利用 OrCAD X Capture 整合的環境,來完成 FPGA Design Flow 的設計-模擬、合成、佈局的功能。並繪製完整的電路圖來連結 PCB Layout 軟體,以完成一個專案設計。

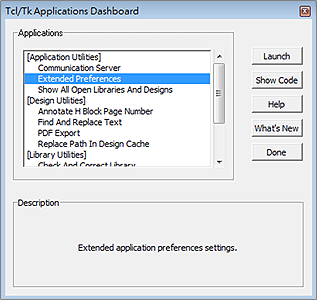

7. 可以利用 OrCAD X Capture Tcl/Tk 程式介面開發新的操作功能

可以利用 OrCAD X Capture Tcl/Tk 程式,來開發或者外掛新的軟體操作或檢查功能讓 OrCAD X Capture 更易於使用。

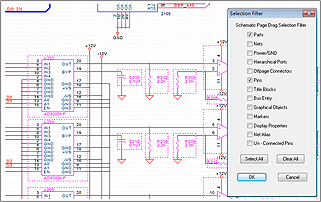

物件選擇功能,可篩選物件類型

在選擇物件時,可利用滑鼠右鍵的「Selection Filter」設定可選擇的物件類型,例如您只想框選電路圖中的零件與 Pin,就可以先全部清除只留 Parts 和 Pins 再用游標框選後,就只會選取範圍中的 Parts 和 Pins,而不會選取到其他物件如 Nets 或 其他物件資料。

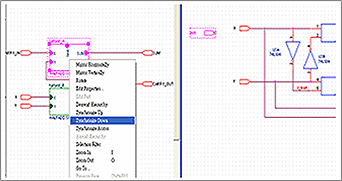

階層式電路,同步產生 / 刪除所對應的連接符號

在繪製階層式電路時,如果上階的代表圖塊有接點的更動或是下階的細部線路有任何外接接點的增減。在以往您需設定好相對應的名稱才會有其接續性,現在 Cadence® OrCAD™ 會自動依接點的增減自動設定好階層式電路上下階之間的對應關係,方便階層式電路的實際應用。

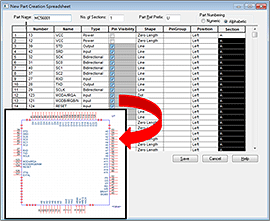

從空白表格中直接 建立零件

在建立零件時最大的困難可能是要敲入數百個 PIN 的接點腳號及名稱,現在可以從收到的規格表中擷取所要的接點腳號及名稱,貼入 OrCAD 中再定義其他的相關訊息,如接點所在的位置等等,可快速自動建立出此顆零件。

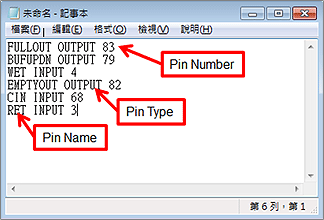

依照電路圖頁面指定零件序號編排

如果可由 IC 廠商,如 Xilinx 得到 零件的接點資料檔,可稍做整理後理出具有接點名稱、接點種類、接點腳號的文字檔,Generate Part 載入此檔案後自動建立出 OrCAD 的零件,不必再用傳統方法逐一宣告大量縮短建立零件的時間。

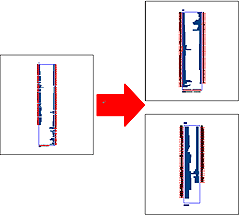

切割大顆零件

使用表格方法或 Pin File 的方式自動建立零件,要是輸入的接點數太多可能會建出一顆超大的零件,因為大過圖框而不適合放到圖面上,如果想把大顆零件切割成幾顆小的非同類零件,可用 Split Part 定義出切割後的小零件數量及各接點所在的位置後自動生成各個非同類零件。

Cadence OrCAD 與 Cadence Allegro 整合

除了可以在 OrCAD 線路圖可上直接定義 Cadence® Allegro® 零件相關屬性,如 ROOM 、 Fixed 、 BOM ignore 、 …..,也可定義 Allegro 訊號屬性,如 MIN_LINE_WIDTH 、 MAX_VIA_COUNT 、 …… ,現在甚至要定義 PIN PAIR 所指定的 U1.17 到 U2.5 的 PROPOGATION_DELAY 的線長,都可在 OrCAD 線路圖中輕易實現。

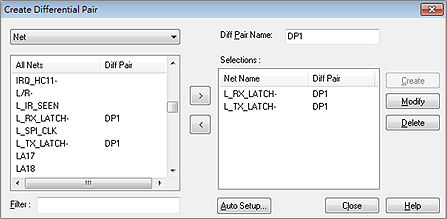

定義差動訊號

在繪圖時也可直接定義差動訊號名稱及其組成的線對成員,甚或用 Auto Setup 定義訊號名稱規則(如尾碼是+和 - )即可由程式自動辨識定義出各個差動訊號對。

能將 OrCAD 線路圖上對 Allegro 的零件或訊號宣告的 properties 以 PCB Editor方式或用傳統 OrCAD 轉 Allegro 的方法以附帶 properties 的方式轉到 Allegro 中

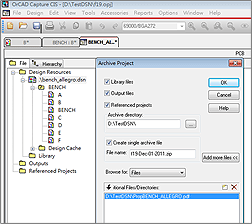

專案壓縮

在繪圖完成後,可利用 Archive Project 選擇要壓縮的相關檔案類型及其檔名和路徑,也可把外部的檔案,如零件規格、相關程式碼等等一起壓縮成 .ZIP 檔,在專案的管理和備份上更加便利。

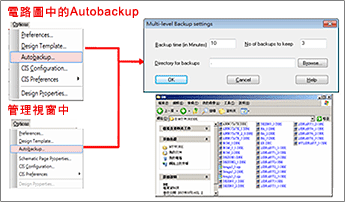

可以設定自動備份的路徑、時間間隔及數量,程式會自動存成各個 .DBK 的備份檔

電路圖設定備份檔案自動存檔,可協助工程師快速地回復前一段時間所修改的資料。

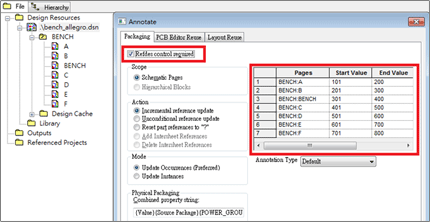

OrCAD 可依照電路圖的頁碼設定每頁起始的零件序號及最大的零件序號

電路圖零件序號可依照電路圖的頁面順序設定起始值及最大值,當零件序號要重新排列,將以設定好的範圍做零件序號的編排!

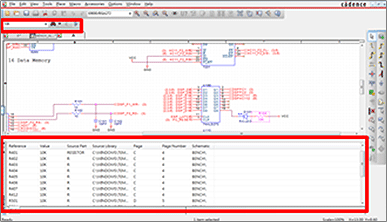

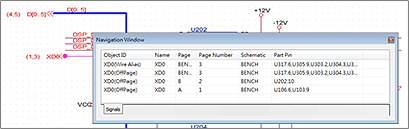

物件搜尋

更加方便的物件搜尋功能,當物件搜尋後,將在畫面下方有 Find window,使用者可透過搜尋結果點選物件,電路圖將直接切換並且 Highlight 所指定物件。

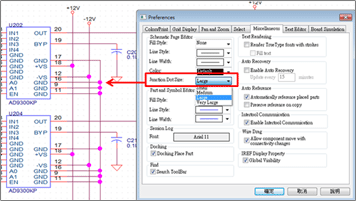

線路圖 Junction (節點)大小改變 -可透過 Junction Dot Size change 的功能更改線路圖節點的大小

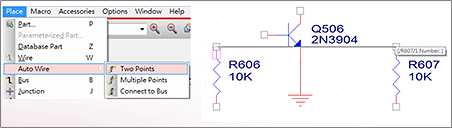

Auto wire 自動連線功能

線路圖 Net 自動連接功能,可讓使用這快速的做單點對單點 Net 的連接,或單點對多點同時連接,或是針對 BUS 線路的連接!

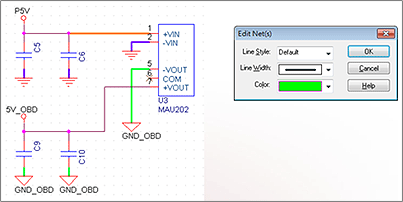

線路圖 Net 查找功能,可針對電路圖中所有與點選的 Net 相同的的線段全部列出,並透或點選的方可以航行到相對應的頁面中

電路圖線段顏色及寬度的改變,可針對線路圖重要的 Net 線改變其顏色期限段寬度或顯示型態

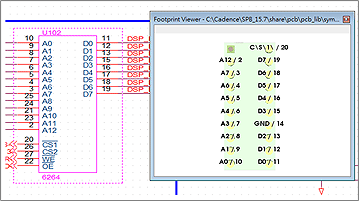

Footprint Viewer 可在線路圖或零件庫編輯畫面中,顯示所對應的 Allegro Footprint 形狀及 Pin number and Ping Name 位置

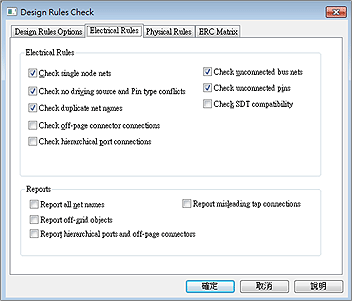

Design Rules Check 檢查的更新

線路圖 Design Rule Check 檢查的更新,現在分成含有電氣屬性的檢查及不含電氣屬性檢查兩大部分,並且在檢查項目中增加了重複 Net name、Footprint missing、未擺放的複合式零件 Package 等重點檢查或報告項目。

Tcl/Tk 程式支援

OrCAD X Capture/CIS 開始 Tcl/Tk 程式的支援,可以自行開發程式或是到原廠 Markeplace 網站下載 OrCAD X Capture/CIS Utility 掛載到程式中使用!

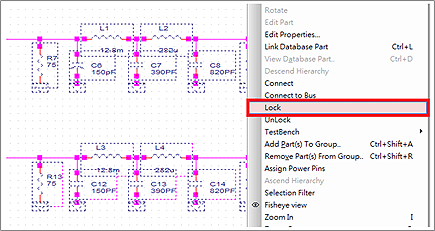

電路圖物件鎖定功能,電路圖可將部分區塊或整頁電路圖物件 Lock,未來所住的物件將不可移動或刪除