完整性高的 FPGA-PCB 系統化協同設計工具

在較新的 FPGA 設計中幾乎有超過千個可程式的 IO pin,若再包含多顆的 FPGA 時,工程師就會遇到初期規劃 IO pin 並配合後期 layout placement 時該如何最佳化的瓶頸及困難,Cadence OrCAD 及 Allegro FPGA System Planners 便可滿足較複雜的設計及在設計初期產生最佳的 IO pin 規劃,並可在透過 FSP 做系統設計時同步整合 logic、schematic、pcb,實現單顆或多顆 FPGA pin 及 layout Placement 的最佳化,藉由整合式的界面以減少重覆在 design 及 pcb layout 的測試及修正的過程及溝通時間,甚至透過最佳化的 pin mapping、placement 後可節省更多的走線空間或疊構, FSP 不僅能使產品加快上市時間,還能夠節省設計成本。

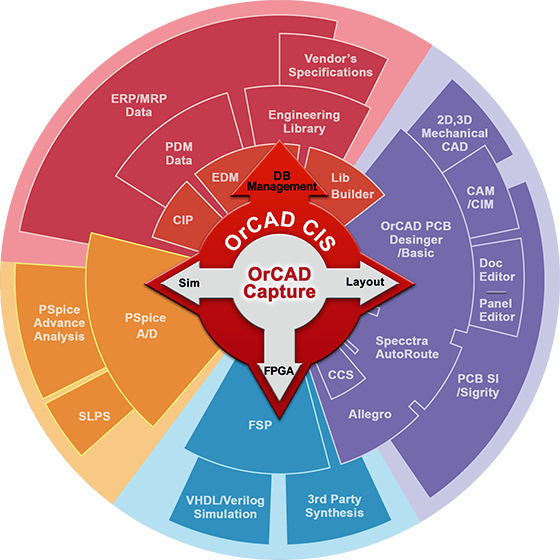

OrCAD 產品關係圖

Specifying Design Intent

在 FSP 整合工具內可直接由零件庫選取要擺放的零件,而這些零件可直接使用 PCB 內的包裝,預先讓我們同步規劃 FPGA 設計及在 PCB 的 placement。

在設計方面,客戶可直接定義 FPGA 及其他零件的連線關係,節省在其他工具設計再轉入 Schematic、PCB 的時間,以目前常應用的 DDR2、DDR3、PCI Express 設計,皆可透過 FSP 產生 FPGA 和 memory DIMM 或多顆 FPGA 間的連線關係。

FPGA Device Rules

在 FSP 的 library 內包含 FPGA models,明定了 FPGA vendor 提供的 pin 腳位的位置及電氣特性。

而這些 FPGA models 可確保設計時會依照 FPGA vendor 所定義的 I/O bank 來使用,有了這些定義可更方便地在此系統物中將群組和群組或功能相同的 pin 做最佳化。

Tight Integration With CADENCE Design Creation

FSP 可自動產生相對應的 DE-CIS、DE-HDL 線路圖及零件,客戶也可自訂或依據 FPGA 的 bank 自動切割 symbol 的大小。

Integration with FPGA Vendor Tools

FSP 可緊密地與 FPGA design tools 溝通,可同步化 FPGA 每個 pin 的功能,不但可產生 constraint 檔案到 FPGA Vendor 工具,也可讀取 FPGA vendor 工具產生的 constraint 檔案。

Scalability

FSP 可完整套用於 Cadence PCB 各系列產品,如 Cadence OrCAD X Capture、Cadence OrCAD PCB Designer、Cadence Allegro Design Entry HDL 及 Allegro PCB design,而使用者也可依需求選用不同的等級,FSP 其詳細規格如下:

| OrCAD FPGA System Planner | Allegro 2 FPGA System Planner Option | Allegro 4 FPGA System Planner Option | Allegro ASIC Prototyping Option | |

|---|---|---|---|---|

| Concurrent Device Optimization | 1 FPGA or Multiple FPGAs totaling 1,000 max pins | 2 FPGA or Multiple FPGAs totaling 2,000 max pins | 4 FPGA or Multiple FPGAs totaling 4,000 max pins | Unlimited FPGAs |

| Placement-aware Synthesis | Yes | Yes | Yes | Yes |

| Reuse Symbols and Footprints | Yes | Yes | Yes | Yes |

| Symbols and Schematic Generation | OrCAD X Capture | Allegro Design Entry CIS / Allegro Design Entry HDL | Allegro Design Entry CIS / Allegro Design Entry HDL | Allegro Design Entry CIS / Allegro Design Entry HDL |

| Post-placement Optimization | No | Yes | Yes | Yes |

| Schematic Power Connections | No | Yes | Yes | Yes |