支援多語言模擬並以涵蓋範圍為驅動的驗證法

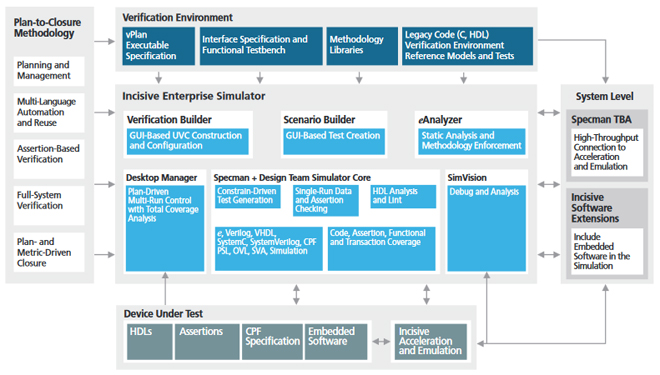

Cadence® Incisive® Enterprise Simulator (企業模擬器)主要利用系統級至 Gate-level 的涵蓋率來驅動功能驗證和除錯分析進一步促進的驗證的效率及可預測性。Cadence Xcelium Logic Simulator 提供 testbench 製作、共用和分析能力,可從系統級至 RTL 再到 Gate-level 驗證其設計,利用此環境從計畫至完成皆可支援涵蓋範圍驅動的運算法,而其原位編譯的模組可在傳統同步模擬加速並同時模擬關於 behavior、transaction(TLM) 、RTL 和 Gate-level 模型,以達到有效改善同步模擬的不良性能。它也支援工業標準的驗證語言並且與開放驗證運算法相容 (OVM/UVM),因此工程師能迅速簡單地整合 Cadence Xcelium Logic Simulator 以建立所需要的驗證流程。

特色

供 HDL 與 Testbench 分析 |

|

提供 Coverage 分析包括 Code 與 Functional |

|

提供進階 Low power 與 UVM 分析能力 |

|

可以與硬體模擬器搭配加快模擬速度 |

|

利用 Plan-to-Closure 方法來驅動並且引導進階驗證流程 |

|

給予 Simvision 工具為使用者提供良好的 Debug 環境 |

|

廣泛支援 IEEE 語言 (SystemC、SystemVerilog、Verilog、VHDL、PSL、SVA、CPF 和 e language) |

自動化驗證流程

管理驗證上的風險

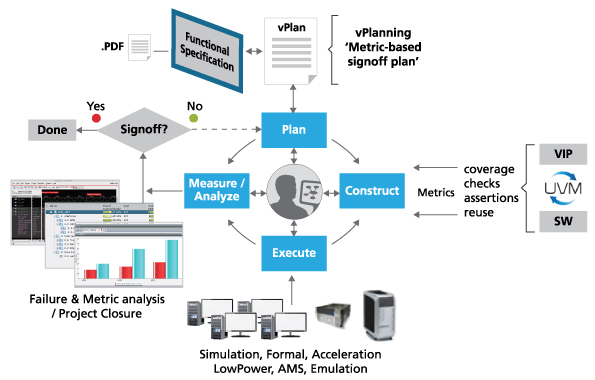

減少驗證風險的第一步就是將流程自動化,Cadence 提供的驗證流程自動化從一開始就訂定想要的結果,然後再依循計畫來管理整個驗證流程直到完成驗證,這種倒置計劃過程是必要的,因為其提供了有效的方法來預估資源需求,可指定任務給每位工程師和定義被測量的涵蓋率標和哪些流程必須要被測量。如何共用也是另一個提升生產力的主要流程,Incisive 平臺為了讓設計變得更容易,盡可能重複利用驗證的 IP,例如元件、環境以及專案跟專案間的計畫。

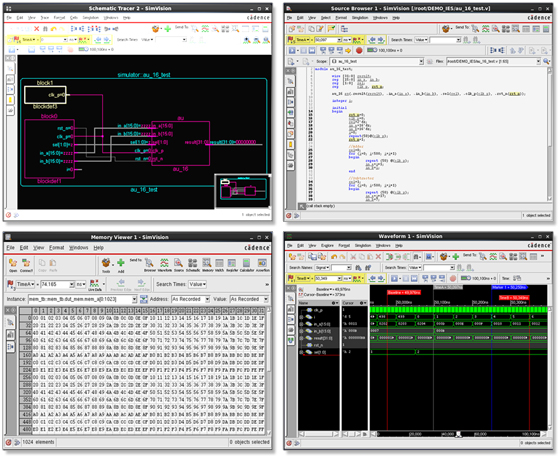

SIMVISION 整合除錯環境

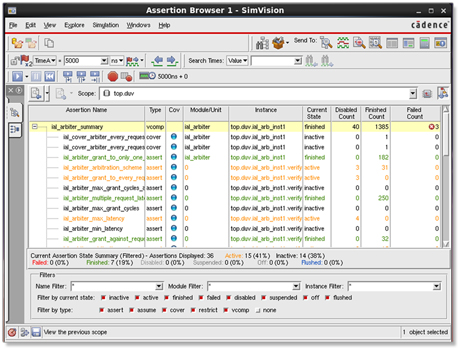

SimVision 提供一個完整的模擬跟除錯環境,讓 Enterprise 模擬器來管理多項的模擬,因此變得更簡單,甚至可以在任何點來分析驗證流程中的設計與 testbench,不需要一次跑完或寫完,而在整個設計與驗證的流程中,Simvision 提供硬體分析檢查、來源檔瀏覽、transaction 跟波形圖觀測、涵蓋分析,應用程式的介面以業界標準來建構,容許所有層級的使用者定義檢查與分析,所以工程師只需學一種除錯環境。

資料與 assertion 檢查

強大的暫存建構功能允許工程師為檢查 Assertion 抓取複雜的協定,即時的數據檢查和生成提供上下文具體期待值,企業模擬器也支援灰、黑或者白盒子檢查的所有組合。

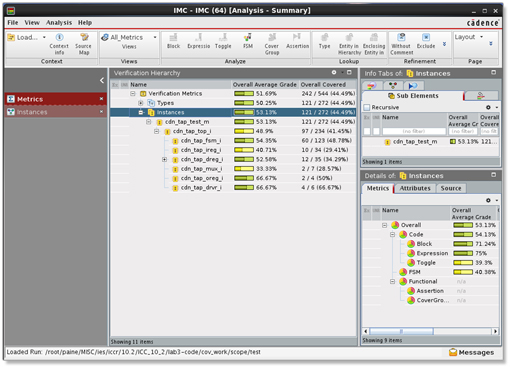

全面涵蓋率分析

企業模擬器支援「全面涵蓋率分析」,可在功能上、DL 碼和涵蓋率的 assertion 上共同使用一個 GUI 來觀看所有可利用的涵蓋率組合,便可確認所有功能充分地被測試,讓設計者能簡單的一次到位。另外,也特別支援功能涵蓋率,例如一個可執行的功能測試計劃 (vPlan),在測試涵蓋率測量驗證流程和功能分析時可簡單自動地辨認出涵蓋率的漏洞,因為功能涵蓋率是在驗證的完整性中是一個有意義且直接的量測,這分析增加了驗證時程的可預測性。

錯誤分析

企業模擬器更進一步簡化整體除錯難度並且用分離設計錯誤與模擬錯誤來縮短模擬錯誤的除錯時間、排序,並將這些錯誤編組變得容易許多,所以便可利用這成本最小的模擬來重覆除錯,進而找出設計的優缺點。

低功率分析

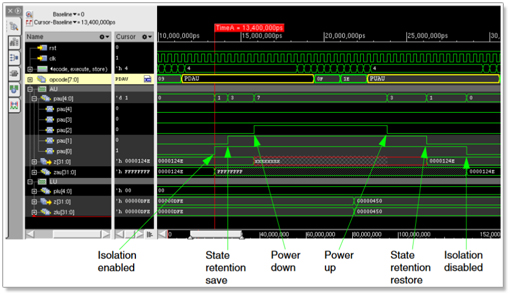

因為產業一直朝著更小的幾何製程、低功率設計和驗證技術的自動化變的越來越重要,企業模擬器發現這需求因而開發對 CPF (Common Power Format) 的本地支援,這是一個開放規格語言,可以帶入特殊功率設計、限制和功能的要求,例如多方供應電壓 (Multi Vth) 和切斷電源 (Power shut-off) 的設計放在一個單一元件中,SimVision 能讓企業模擬器內部核心、整合顯示以及功率行為除錯來啟動自動化降低功率的方法,並且可與其他 IC 流程的配合來設計低功率 IC。

結果: 設計工程師可在設計週期的前期就能確定 DUT 的功率特性,能比光靠利用運算法更節省功率的損耗。

HDL 與 TESTBENCH 分析

HDL 分析可在設計周期中抓出早期設計以及編碼的錯誤,它可測出多達五百多個檢查標的來標出語法、語意以及功能上的錯誤,當一個流程包含 HDL 分析時,模擬便會檢查編碼是否會有競爭的情況(在非同步時序電路中產生的一種不良現象,在狀態轉換時,有兩個或兩個以上狀態變量同時變化,其結果無法預料,因為它完全依賴於哪個輸入是先進行的,因此在設計時應儘量避免產生競爭的條件 ) ,在檢查計時器域的同步是否有問題、語意是否有衝突,而且是否可以完整合成,同樣地在企業模擬器 eAnalyzer 元件上的靜態分析 e 語言的 testbench,讓工程師易發現共用以及設阜的問題,所以可以廣泛設定除錯以及整合 testbench 環境來加速模擬,HDL 與 Testbench 分析伴隨著檢查的承諾規範與共用 plan to closure 運算法,並且也可以製成標準的作業手冊,這些強而有力的規範定義圖形介面和圖形分析工具,幫助設計者寫編碼並且讓它有效減少錯誤產生的機會。

專案複雜度風險

語言與運算法風險

驗證的風險與矛盾

電子產品設計過程中充滿許多不確定的驗證風險與矛盾。設計是否能運作?軟體是否能運作?設備是否能達成效率目標?在這些未知數下,要準確預估何時完成設計幾乎不太可能。而且一個沒檢查到的小 bug 就可能造成產品回收的問題,而當我們把驗證作為風險控管工具時,現今的驗證能力很快會被設計的複雜程度所擊饋,因此設計團隊必須重新思考新的技術、新的語言和新的方法。然而,對一個現有的驗證環境所做的變動可能會產生更多不確定的變數,而且每個設計團隊都必須面對如何避免當設法減少風險的時候又增加不必要風險的矛盾。 Cadence Incisive 功能驗證平台透過自動化的驗證過程和整合的驗証環境來去除風險,基於驗證技術利用最廣的涵蓋率以及語言和運算法的低風險應用,能幫助您的產品在沒有錯誤下符合所需規格,並能準時 tape out。

目標導向的自動化驗證流程 (VPA) |

|

獲得認可的全面性技術 |

|

有專門支援的語言及運算法來降低風險 |

設計過程中之風險

當設計專案變得越來越複雜,常規的技術與運算方法開始不敷使用,進而造成生產力的下降,在這個時間就是金錢的市場裡,具有競爭力的公司當然無法遷就過時的設計以及驗證方法,促使設計團隊必須時常改善其環境設定以達到效率。

在邏輯複雜度快速增長的情況下,不僅愈難判斷設計能否順利運作,連預測設計是否能成功也變得更加困難。事實上,驗證團隊從來無法明確知道何時能完成驗證,這便是將產品的品質暴露在高風險上,因多數的設計團隊使用少量 metrics 或者缺乏一個全面驗證計劃措施,這樣的流程便缺乏清楚的流程枝幹,屏除基本的生產力和品質問題不談,設計團隊面對的是從未改善且沒有能見度的驗證過程,當然易導致時程表延宕。因此審慎地處理和運用珍貴的人才、計算資源,並且需要提高製程的能見度極為重要。

另外,設計團隊提出的計畫不僅需保證產品的品質,而且要能設立里程碑來追蹤進度,metrics 不僅要能簡單顯示何時能完成驗證,而且能確認漏洞的存在,要做什麼驗證是否有效,以及再做什麼步驟可以更快的讓驗證流程完成。