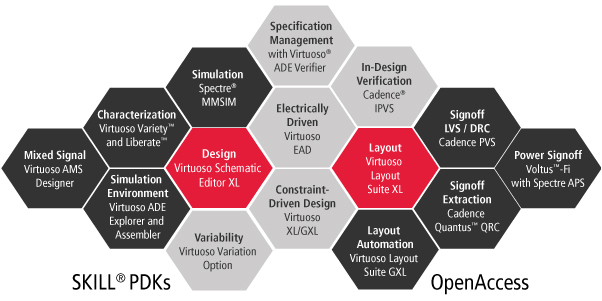

Custom Design Platform

個人消費電子和無線產品已經成為當今世界電子市場的主導力量。這些設備對於新功能 (new features) 和特性 (functionality) 的要求,促進了 RF、類比和混合信號應用設備的前所未有的發展。為創造滿足該需求的新產品,企業採用 Custom Design 的技術,將可使 IC 設計工程師更能掌握精確的類比數值,如電壓、電流、電荷,以及電阻與電容等參數值的持續比率。

為簡化設計 Custom IC 的流程,並將其整合到終端產品中,半導體和系統公司需要精密的軟體和設計流程方法,以達成迅速上市和迅速量產的目標。Cadence® Virtuoso® Custom Design Platform 提供了極其迅速而保證晶片精確的方式,進行定制類比、RF 和混合信號 IC 的設計。

Cadence® Virtuoso® Custom Design Platform L 是入門級的客製 IC 專業平台,不論您的 IC 是應用在類比或是混模訊號的設計,Virtuoso 平台都能提供您一個從前端到後段的整合流程,以及各種不同程度的解決方案以符合各種客製 IC 不同的設計需求。

VIRTUOSO SCHEMATIC EDITOR L

快速精確的線路輸入 Virtuoso

Schematic Editor L 的強大功能提供您快速易用的設計輸入環境,利用其完備的的零件庫使得 gate 和 transistor levels 的設計更加快速,再加上便利的接線功能,使我們面對更大更複雜的設計時能更加順手。除此之外,階層式編輯器能方便地管理其階層的關係,當您的設計是規劃成階層式的結構時,也能確保整體設計中所有接線的正確性。

業界標準的設計語言

利用業界的兩種先進的硬體描述語言 VHDL 和 Verilog HDL,Virtuoso Schematic Editor L 可方便地套用到 mixed-level 混合設計中,另外也支援了 Verilog-AMS 及 VHDL-AMS,藉此我們可以不論設計類型,以同樣的方式來設計 mixed-signal 混合訊號,還能由輸入描述語言自動建立所代表的線路區塊,以供 system-level 系統階的 IC 設計需求。此外由於現今 IC 設計不單單只考量到晶片內部的效應,對於 PCB 載板上的 RDL 走線與元件,都需要同時考量,因此現在我們也同樣支援 PSPICE 的描述語言,使得產品設計能夠通泛考量的更加全面與完整。

擴展的設計檢查功能

為了要確認設計的精確性,我們可以自訂對圖面和電性規則的檢查條件,例如零件重疊、短斷路、未接的 inputs outputs、物件的一致性或不合的名稱等,讓設計者以單一指令完成對單 / 多張圖面或是整體階層設計的 pin name 對應和接線的完整性及訊號編名的檢查功能。

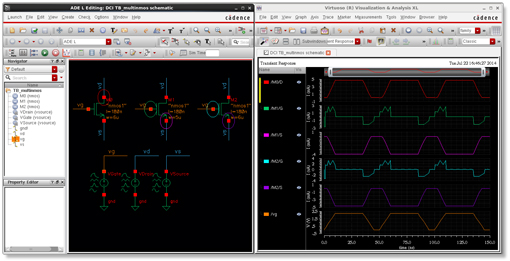

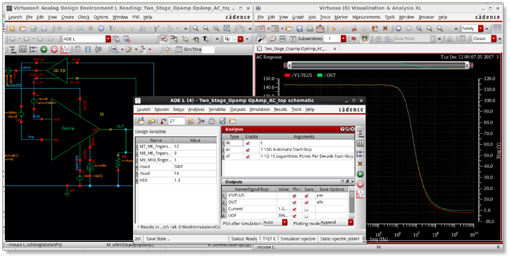

VIRTUOSO ANALOG DESIGN ENVIRONMENT L

易用互動的設計和模擬環境

Analog Design Environment L 的互動式環境可讓我們設定、執行 Multi-Mode Sim 和分析其結果,利用其各種顯示及分析功能讓您對類比、射頻及混和訊號的掌握更加便利,期望讓您能更快速找到設計中的關鍵點,並能求得最佳化的結果。另外,其多樣的環境除了搭配之外,再配合其他模擬程式時,不需要重新設定所有參數。

內建波形顯示及訊號分析

波形顯示內建了可擴展的波形計算器,提供了完整的 post-sim 分析環境,其波形顯示視窗可顯示各種類比和混和訊號資料,如 noise、corner、射頻波形,另外還可調整顯示的效果,如水平 / 垂直軸、波形顏色、標註等,建立出最好的圖面及報表。波形標籤及計算器可精確量測出在 Transient、AC 與 RF 等不同模式下的訊號,並可依輸入 / 出電壓值或電流值再搭配代數運算以求出其他的量測結果。

跨越線路和實體設計的鴻溝

Virtuoso Analog Design Environment L 所提供的模擬環境可比對 pre-sim 及 post-sim 的不同條件,使得我們可以跨越線路設計和實體佈局的障礙,實現由前端到後段完整的 IC 設計流程。

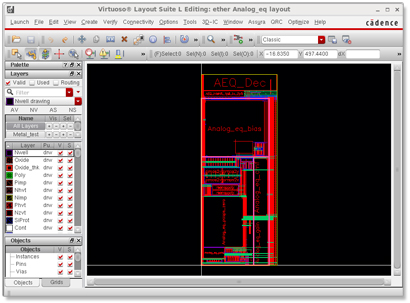

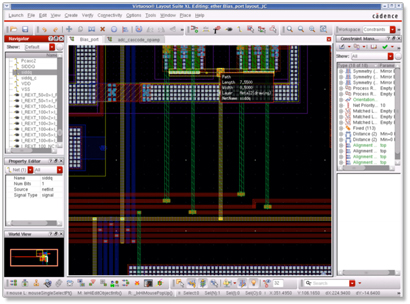

VIRTUOSO LAYOUT SUITE L

全階層式、多窗式的設計環境

Virtuoso Layout Suite L 可在一個編輯環境中同時開啟多個 cells 或 blocks 甚或是階層均可在同一視窗打開,幫助設計者在複雜的設計中確認其資料的完整性,其整合的 World Viewer 全視窗可以很直覺地查看整個設計中相應區塊的位置,並可執行選取、顯示範圍調整、重繪等常用指令,以提升佈線效率。

多樣的參數式 Cells 加速設計時效減少設計錯誤

Parameterized cells (Pcells) 提供設計自動化的效能以減少繁瑣及重複的佈圖工作,Pcells 可在不更動最原始 cell 的情況下更改每個 cell 的尺寸、SHAPE 及所含物件,依參數設定所建立、編輯和管理的 shapes 和 devices 可更加簡化,以加速佈圖效率並減少設計錯誤。

QuickCell 選單自動建立 Device

QuickCell (QCells) 參數選單功能可快速建立及編輯 Pcells devices,可在無 Pcells SKILL 的環境下實現建立及編輯 devices 的環境, 由於 QCells 是「C」為基礎的環境,所以可程式的 Pcells SKILL 也可套用及相容於 QCells 的環境下。

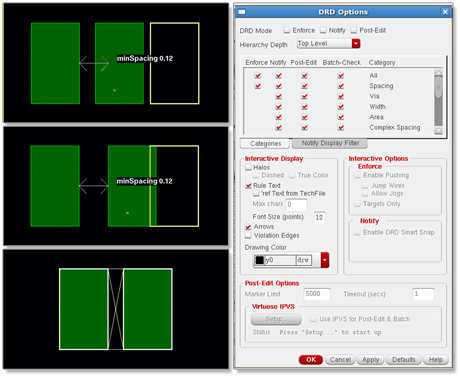

設計規範管控以增加效率

Virtuoso Layout Suite 提供「設計規範管控」的功能,可以即時監控違反規範的錯誤,以增加佈圖效率減少錯誤點及偵錯的時間,也支援 90 奈米(或更小)的各種複雜製程規範的 technology file。

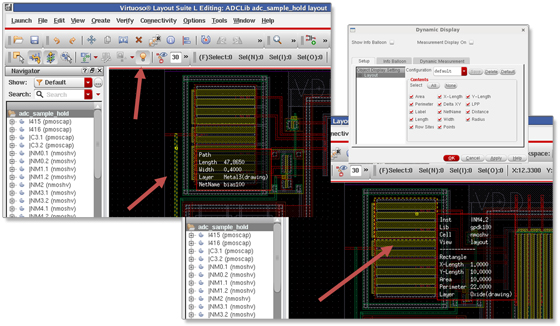

自動簡化及優化的佈線效果

Virtuoso Layout Suite 能夠自動簡化及優化 block 來達到以「設計規範管控」的功能和流程,「動態量測」省掉許多手動量測的麻煩,「對齊功能」也能加快對齊圖型、接點和物件的效率,「訊號標示」讓您在多階的設計中達成對訊號查詢,明亮顯示及檢查接續性目的。

Multi useful Assistants window

View all geometry dynamically during editing commands

Design Rule Driven - Real time aware DRC violations

Cadence® Virtuoso® Custom Design Platform XL 系列是客製 IC 的進階平台,提供您在設計更高階產品的更好環境,包括的產品有Virtuoso Schematic Editor XL、Virtuoso Analog Design Environment XL、Virtuoso Layout Suite XL。

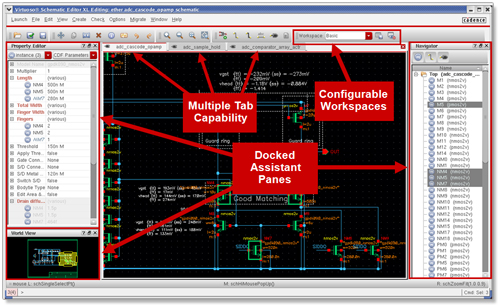

Virtuoso Schematic Editor XL

提供進階功能能使得其效能達原 Virtuoso platform L 的五倍之多,使用者可利用其 design constraints 設計規範來串連整個設計,這些規範可讓使用者從線路圖端即宣告佈圖的重點和注意事項,如匹配性及對稱性等等。

作為 Virtuoso 的前端平台,Virtuoso Schematic Editor XL 提供了客製 IC 設計輸入端的各種擴展功能,從業界標準語言 (如VerilogR 、VHDL 和 C) 所做的架構定義 architectural definition 到 transistor level 的最終結構定義,都能幫助工程師執行設計中的每個階段,利用 XL 階所介紹的「design constraints」概念,讓我們可以將設計的「意念」儲存在設計之中,若下一次設計有使用,可直接套用,減少其間的落差。

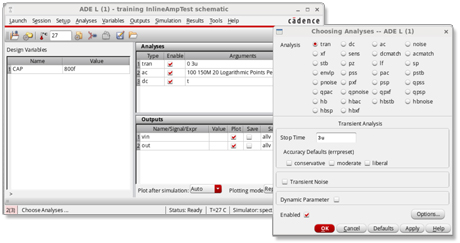

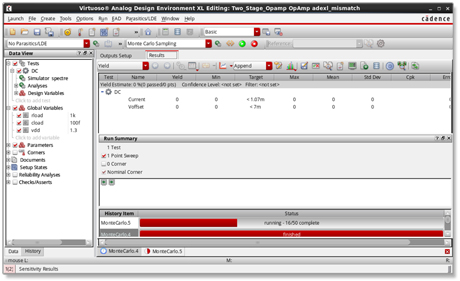

Virtuoso Analog Design Environment XL

Virtuoso 平台上最先進的設計和模擬環境,經由跨設計的物件指定及選取效果,可幫您建立一個快速且精確的設計驗證環境。

Virtuoso Analog Design Environment XL 可以在一個易用的工具中同時管理及驗證多個 design,並且在設計和驗證的流程中,所有線路可以對應到相應物件成功/失敗的狀態。另外,所有的 sweeps、corners、Monte Carlo 及量測都能被管理及儲存在一個位置中,以求快速準確的設計驗證。

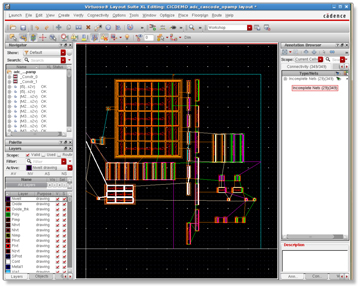

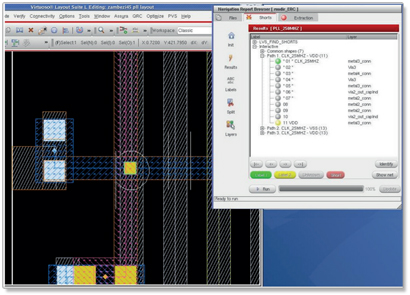

Virtuoso Layout Suite XL

Virtuoso 平台上最先進的客製佈局環境,提供了 constraint-driven 規範-管控及線路圖-管控的兩種實體佈局環境,讓您在設計數位、混和訊號及類比產品時的 device、cell 和 block 階都能有最好的規範可依循。

作為 Virtuoso 的高階佈圖平台,Virtuoso Layout Suite XL 除了 L 階的基本 polygon 佈圖編輯功能之外,更針對 device、cell 及 block 來提供客制數位、混和訊號和類比設計等支援,也使得規範管控及設計管控的功能能夠與其他自動化的進階功能相結合,以加速客製零件編寫的速度,別忘了還有 parameterized cell (Pcell) 和 SKILL 可讓您在 device 的建立和編輯時更能得心應手。

軟 體 特 點

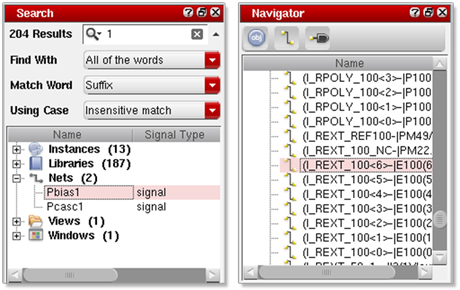

快速且精確的設計輸入環境

Virtuoso Schematic Editor XL 提供了 L 階中的搜尋、屬性編輯查看和設計階層環境等各項功能外,也可將電路設計輸出至網頁瀏覽器中查閱,另可使用 Design Constraints 設計規範來串連整個設計,這些規範可讓使用者從線路圖端即宣告佈圖的重點和注意事項,如匹配性及對稱性等等…快速且易用的設計輸入功能。

規格式的設計

通常規格需要多項測試,並經由結合測試規範與具體測量來加以確認,為了要加速設計的驗證,Virtuoso Analog Design Environment XL 將設計管理及規格輸入結合在同一個環境中,讓您可輕易地建立多種情況下的不同測試條件以驗證您的設計。

而在 project 內,可選取所有的測試 sweeps、corners 和相關文件作驗證比對之用,並可查看專案的所有測試結果,如所有的波形、量測值和模擬檔的狀態都可以呈現出來。

Virtuoso Analog Design Environment XL 可執行單一或多個測試亦或是多個測試中的 sweeps、corners 及 Monte Carlo 分析,可使用並行處理的選項讓整個模擬管理上更加有效率。

Virtuoso Analog Design Environment XL 支援將所有測試分析結果自動儲存作規格確認之用,亦可整合 Virtuoso Multi-Mode Simulation 實現類比、射頻、混合訊號的模擬驗證。

連線管控式的功能加速設計的完成時效

Virtuoso Layout Suite XL 設立了工業標準,改變傳統的客製設計流程,設計者可經由 Virtuoso Schematic Editor XL 所定的連線關係,或是由外部,如 CDL 或 SPICE 所載入的連線檔來執行即時的 LVS,用以檢驗其佈圖,也因此實現了「correct-by-construction」的佈圖環境,提高生產力並減少驗證的時程。另外,也使得繁瑣的 DEVICE 建立、擺放和佈圖可以自動化,線路圖也可以跟實際佈圖之間的 instances 和 devices 互相查詢、highlight,並可快速找到未接的訊號等其他功能。

規範管控及設計管控以提高生產力

Virtuoso Layout Suite XL 提供規範定義及管理環境,另外,設計規則的定義還可自動且即時地標示違反設計規則點,讓我們可以同時達到依規範管控佈圖及提高生產力,並減少佈圖錯誤點和驗證的時間,不論是傳統類比的 .25u 到最先進的 45 奈米製程的條件,所有 Device 建立、擺放、或自動 / 手動佈線,都會遵照規範內的 technology file 的規則定義。

與其他 VIRTUOSO 平台工具的密切整合

上述的功能都整合在 Virtuoso 客制設計平台上,可以利用單一環境整合平台上的所有功能來建立分析及實現不同面向,如 ASICs、可程式 IC、MCM、數位 IC、類比 IC 及混和訊號 IC 的設計需求,VIRTUOSO 平台支援業界標準的 OpenAccess (OA) 資料庫及 Cadence SKILL 可程式語言,讓您可以自訂工作環境建立最佳的自有環境及流程。

設計流程

線路設計 Circuit design (Front End)

Cadence 的線路設計 circuit design 方案可讓您快速且精確的繪製出您的設計概念並有 效管理設計的方向,尤其是在客制 IC的設計流程中利用對非重要訊號的自動化步驟使 得工程師可以專注在極精細的設計中,利用其 Analog Design Environment 可以從線路圖直接對應到類比 analog、射頻 RF 或混合訊號 mixed-signal 的不同設計所引發的線路特性上的不同效應。

其工具有 :

Virtuoso Schematic Editor |

|

Virtuoso Analog Design Environment (ADE) |

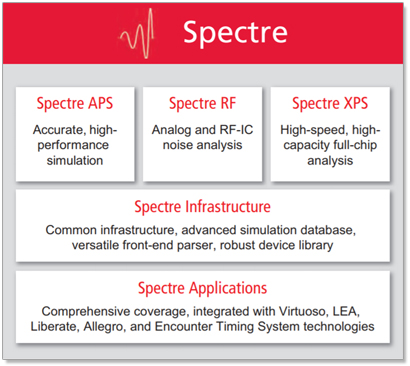

模擬 Simulation

分別有 Block-level、Chip-level 和 Mixed-signal 的不同模擬效果和工具:

Block-level |

小功能區塊的模擬,主要著重在單一區塊從架構到功能的實現 |

|---|---|

Chip-level |

整合所有區塊的全晶片模擬,著重在其效益和準確性,由其是 system-on-chip 時因整合類比及數位區塊所衍生出其間的互應及影響 |

Mixed-signal |

綜合 block-level 和 full-chip 的類比模擬器和先進的數位分析模 擬器,使得我們可以把多種語言的數位設計可以跟類比或 RF 輕易的整合在一起 |

其工具有 :

Virtuoso Multi-Mode Simulation (MMSim) |

|

Spectre Circuit Simulator (Spectre) |

|

Spectre Accelerated Parallel Simulator (APS) |

|

Spectre Extensive Partitioned Simulator (XPS) |

|

Virtuoso UltraSim Simulator (UltraSim) |

|

AMS Designer Simulator (AMS) |

佈局設計及佈線 Physical layout & Router (Back End)

佈局設計主要是將前端電路圖轉換為實際的晶片佈線,最終將佈局圖轉換為光罩檔,以供晶圓廠生產。客製化的佈局需考量許多的佈局條件,往往需要人工來完成,Cadence的佈局工具提供方便的功能,可讓工程師加快佈局的速度。

其工具有 :

Virtuoso Layout Suite |

|

Virtuoso Chip Assembly Router (CAR) |

|

設計驗證 Verification

佈局圖完成後,需檢查是否符合製造的設計規範,以防止如晶片線路短路或斷路…等等的影響。另外亦需比對佈局圖與電路圖是否一致。

其工具有 :

Cadence Physical Verification System (PVS) |

|

Assura Physical Verification (ASSURA) |

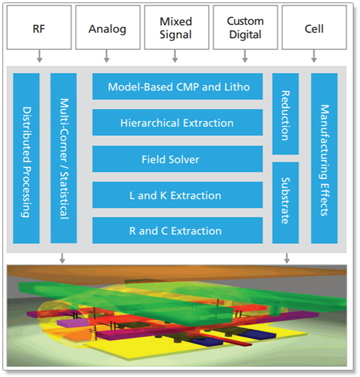

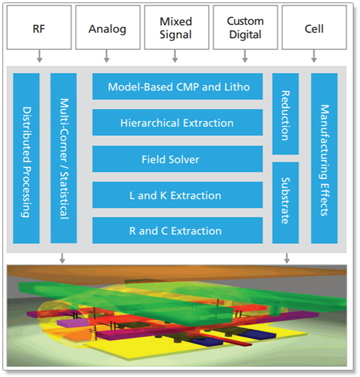

萃取寄生效應 Parasitic Extraction

寄生效應會造成我們設計的問題,透過 Cadence QRC Extraction 萃取寄生效應,並藉由 Virtuoso Solution 將萃取出寄生資料的回應到設計上,讓我們對整個設計有最全面跟巨觀的考量跟最即時的分析,以判定出真正問題之所在。

其工具有 :

加速客製化 IC 佈局工具 SKILLCAD

SKILLCAD 是一家專精於發展加速客製化 IC 佈局工具的軟體公司;SKILLCAD 的系列產品整合了 8 種主要的工具,這些工具可支援先進奈米製程的製程設計規則;SKILLCAD 軟體公司是 Cadence 優秀的策略夥伴,其產品主要是建構在 Cadence Virtuoso 的平台上,增廣 Virtuoso 在不同產業的應用範圍,並有效縮短晶片佈局的時間。

| Virtuoso Post-Layout Simulation Methodology |

| IC-FPGA 混和設計與模擬(上篇) - 整合 PSpice 到 Incisive/Virtuoso 設計流程 |

| IC-FPGA 混和設計與模擬(下篇) - 加入 IBIS Model 提升混和模擬準確度 |

| 全新的類比設計環境-Cadence Virtuoso ADE Product Suite |

| Cadence Virtuoso L (DM) |

| Cadence Virtuoso XL (DM) |

| Cadence Virtuoso L (spec) |

| Cadence Virtuoso XL (spec) |

| Cadence SourceLink 註冊步驟 |

| 如何自動收到 Cadence SourceLink 軟體更新通知 |