本文要點

嵌入式系統在運行期間需要節能,以確保較長的電池續航時間、降低公用電力消耗並防止產生過多熱量 |

|

透過採用各種節能模式和實施廣泛的功耗管理策略,現代器件使設計師在控制功耗方面有了更多施展空間 |

|

嵌入式系統的處理器可以成為耗電大戶,但也可以借助獨特的演算法在管理功耗方面發揮積極作用 |

此圖中的 IC 具有低功耗睡眠模式,在這種模式下,它們在收到喚醒/警報信號之前不消耗能源

任何與電子產品打交道的人,無論是作為設計師還是隸屬其他職能部門,都知道電子元件會產生大量熱量。它們在運行過程中也會消耗大量能源。當今世界非常注重能效,降低電子系統的功耗始終是人們關注的焦點。

由於多種原因,嵌入式系統是降低功耗和提高能效的主要物件。有的嵌入式系統靠電池供電,要求電池續航時間長達數年,並且對電池形狀有特殊的要求。有的嵌入式系統靠電網或發電機供電,但這仍需要節約能源,以降低總體功耗並防止產生多餘熱量。

一些基本的嵌入式系統功耗管理技術可以大大減少熱量產生、節省系統空閒期間的多餘功耗等。當今的器件、高效的調節器設計和先進的功耗管理演算法可以發揮巨大作用,確保新的嵌入式系統高效節能。如果您正在規劃新的嵌入式系統設計,請注意以下技巧,以確保您的系統以最高能效運行。

利用嵌入式系統的功耗管理技術降低功耗

所有嵌入式系統都提供用於特定用途的計算能力,但它們所包含的元件遠遠不只是一個 CPU。嵌入式系統的許多領域都可以採用功耗管理策略來降低功耗:

處理器: |

|

功耗調節: |

|

外設: |

|

信令協議選擇: |

|

無線通訊: |

|

嵌入式韌體和軟體: |

下表顯示了在上述每個領域中實現節能的一些機會。其中一些領域在嵌入式系統開發中更為突出,應給予更多關注。下面將討論這些特定領域。

處理器 |

各種處理器可以自動進入低功耗模式,或者可以在代碼中配置啟動低功耗模式的功能。 |

|---|---|

功耗調節 |

對於特定的功耗,應該進行功耗調節以使效率最大化。對於 AC-DC 轉換器,請使用 PFC 電路以確保高效的電能轉換。 |

外設 |

外設可以放置在一個 layout 中,這裡它們擁有自己的調節部件和功耗,可根據需要切斷對這些部件的能源供給。 |

信令協議選擇 |

許多器件可以與多個介面進行通信,因此設計人員和韌體 / 軟體發展人員在某些情況下可以自由選擇功耗最低的介面。 |

無線通訊 |

無線協定可能不需要持續連接,可根據需要關閉 RFFE 和數據機。 |

嵌入式韌體和軟體 |

可以優化韌體 / 軟體本身,或者可以實施功耗管理策略來開啟 / 關閉外設。 |

軟體和韌體

很簡單,代碼執行策略包括編寫代碼,以便系統在最大程度減少邏輯運算元量的同時完成所需的任務。使用數位邏輯來實現計算任務會增加任務的演算法複雜性,固件開發人員應該考量用來實現演算法的邏輯。

對於單電路板電腦這樣的系統,應該優化作業系統本身,儘量減少後臺運行的任務數量。Linux 內核是嵌入式電腦的標配,因為 Linux 內核可以根據需要定制或多或少的週邊應用支援。透過消除後臺進程和服務,處理器可以在空閒時執行更少的任務,降低功耗。

器件和處理器選型

正如上表所示,功耗在很大程度上取決於以上每個領域的元件選型。尤其值得注意的是,許多處理器單元 (MCU、FPGA、MPU 等等) 被專門作為低功耗器件進行銷售,並使以下的嵌入式系統功耗管理技術成為可能:

使用各種信令協定執行指令,因此可以根據需要選擇功耗最低的協定。 |

|

進入低功耗休眠模式或空閒模式,在這些模式下,將縮減內核電壓和頻率以降低功耗。 |

|

降低 ADC 或其他接收器的取樣速率,這將降低與模擬感測器交互時的總功耗。 |

|

動態開啟 / 關閉各種外設。 |

|

使用具有禁用/啟用設置的外設,禁用/啟用設置可以通過標準的低速數位協定 (I2C、SPI、GPIO 等等) 觸發。 |

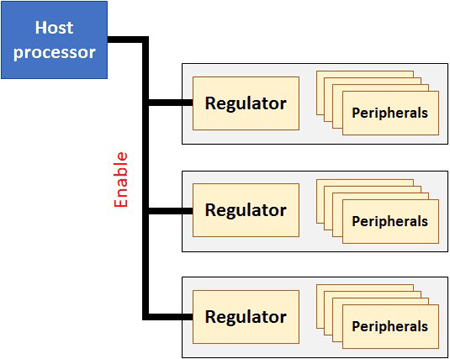

最後一點需要一個功耗管理策略,將功耗分配到不同的功能模組,每個模組都有自己的功耗調節器。如以下區塊圖所示,這可以借助一些傳感介面和低速數位介面來實現。

區塊圖顯示嵌入式系統的外設功耗管理技術

當您需要在嵌入式系統中實現任何功耗管理技術時,Cadence 可為您提供強大的系統設計和分析工具,自動執行系統分析中的許多重要任務,包括利用一組整合的場求解器進行電源完整性模擬和功耗管理分析,如果想進一步瞭解深入問題,歡迎點擊下方瀏覽資料手冊、白皮書等更多內容:

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」