概述

單純從 PCB 物理設計方面來分,可將 PCB 設計流程分為器件佈局、佈線、後處理三大階段。每個階段設計品質好壞,將直接影響下一階段的設計難易度及效率。PCB 設計涉及硬體電路原理、訊號/電源完整性、印刷電路加工/組裝等等,要實現高品質高效率地交付,需要設計者具備較為廣泛的知識面。

總體流程

為便於理解,透過一個流程圖來闡述 PCB 設計總體流程。該流程圖只概述 PCB 設計整體流程,各階段之間不是完全獨立,也不一定嚴格遵照該順序。比如,佈局階段也可進行佈線,該階段的佈線即是 Fanout,即把器件的引線都設計完成。

PCB 設計的各環節不完全獨立,其設計順序與各公司的設計流程相關,可根據公司流程要求,自行隨意調整。例如,如果把 DFM 的檢查嵌入到設計流程中---即透過設定 DFM 規則,確保設計過程中就滿足可制造型,這將有效提升我們的設計效率及品質,避免後期的重複修改。對於設計者來說,也可免除很多重複不增產值的勞動。

各階段詳述

前期準備

前期準備階段,電路圖、機構圖、DFx 規則、SI/PI 設計規則等都是 PCB 設計啟動的輸入條件。輸入條件準備得越充分,後續的設計工作將越順暢。但是,在實際專案開發中,電路圖、機構圖、PCB 圖都在同步設計,所以就會出現 PCB 設計返工的情況。我們需要儘量考慮周全,最大程度地減少返工,提升設計品質和效率。

PCB 設計工程師應在已有條件下,儘量做好前期準備,才能交付高品質的 PCB 設計文件。這些前期準備包括但不限於如下幾個內容,涉及需要舉例圖示的部分,以 Cadence 的 Allegro PCB Designer 為範例,因為我從業期間用的是該工具。

1. |

電路圖 --- 網表導入 |

|---|---|

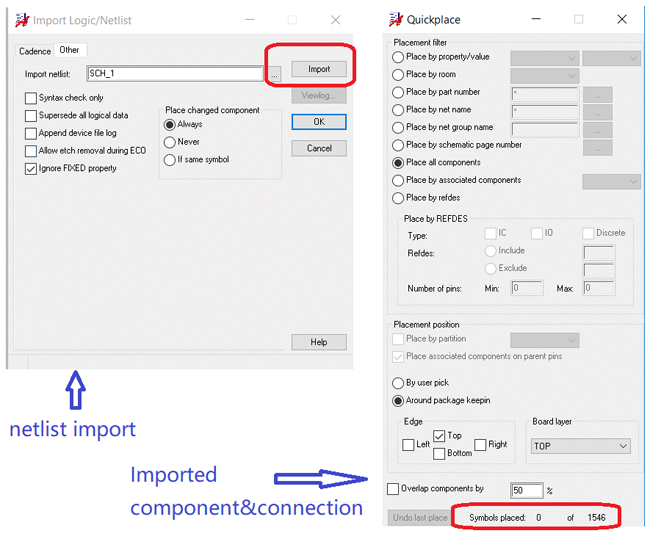

基於電路圖生成能夠成功導入 PCB 設計工具的網表。網表承載的是各元器件之間的邏輯互連關係。在此,默認 PCB 設計所需器件的 footprints 已準備就緒。我們只需執行網表導入命令(File >> Import >> Logic / Netlist),即可將器件邏輯連線關係從電路圖轉化到 PCB 設計工具中。如圖所示。 |

2. |

機構要素圖導入 |

|---|---|

導入機構工程師提供的機構要素圖,繪製 PCB 外形,擺放有特殊位置要求的元件,例如金手指、連接器、LED 指示燈等等。(命令:File >> Import >> DXF) |

|

3. |

DFx 規則設定 |

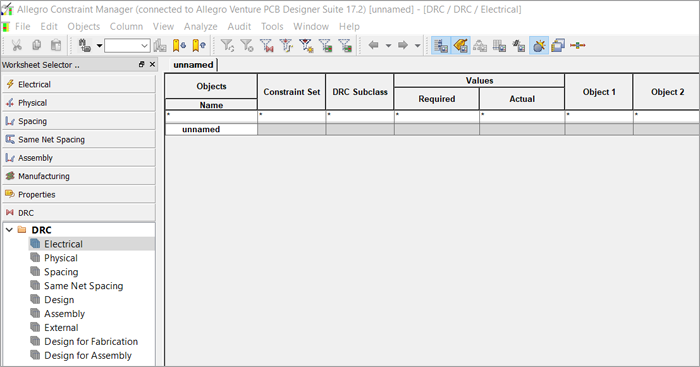

DFx 規則指 PCB 加工要求、PCB 所使用的器件組裝要求、PCB 測試要求等,這些要求都資料化並以規則的形式在 PCB 設計工具(例如 Allegro)中設置,用於驅動設計實現。 |

|

4. |

SI / PI 設計規則 |

訊號完整性和電源完整性要求,資料化後透過規則設定,落實到 PCB 設計中。 |

Allegro 的 CM 圖示

佈局階段

佈局階段分為模組佈局及整體佈局兩個大的階段。

1. |

模組佈局 |

|---|---|

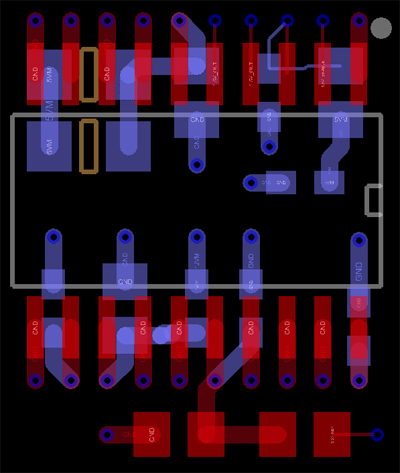

將電路圖各功能模組的器件都按照訊號流向佈局完成。根據個人設計習慣不同,這個階段的工作內容也會不同,我習慣於同時完成所有器件的 Fanout,並將其定義成一些獨立的模組。在此階段,如果我們所用的工具能夠支撐佈局複用,那能為我們的設計進度帶來質的飛躍。 |

|

2. |

整體佈局 |

把各功能模組按照他們的邏輯互連關係,一一擺放到 PCB 的 outline 內。這時候,我們需要對各功能模組非常熟悉,還要理解該 PCB 的訊號流向,電源樹結構等,這有利於整理佈局的合理性。同時也要考慮工藝加工要求、單板散熱要求、系統組裝要求等,確保整體佈局完成後,DFx 的規則都得到落實。 |

模組佈局實例

說明:上文提到的佈局複用,是針對一個 PCB 中有很多個相同模組的設計。在這種情況下,如果工具支援佈局複用,那我們只需要佈局一個模組,其他相同模組就可以在幾秒-幾分鐘內複用完成,可以大幅提升設計效率。

佈線階段

佈線階段的難易程度與佈局的合理性相關,如果佈局時的佈線方案考慮得比較成熟,那此時只需按照規劃完成連結。但如果佈局時只是簡單的完成器件擺放,那到了佈線階段就會比較痛苦,我們將發現我們不得不邊佈線邊調整佈局,因為佈線實在是太混亂了,完全沒有頭緒。這種情況一般出現在初入行的時候,那真的會讓我們返工很多次。在此,我將按照我的流程給大家介紹佈線階段的詳細步驟。

1. |

規則審視 |

|---|---|

審視各類規則 - SI / PI 規則、DFx 規則、DFT 規則等,確保這類檔都是最新稿,並將它們資料化後設定完成。 |

|

2. |

檔更新 |

保證機構圖和電路圖都是最新稿,儘量將修改的風險降至最低。 |

|

3. |

層疊設定 |

根據設計要求和各訊號的空間順序,規劃合理的層數。此處需要考慮諸多細節因素,比如阻抗控制、高速訊號、介面處設計、電源結構等等。 |

|

4. |

平面層處理 |

PCB 設計中的平面層,通常是用於處理電源和地訊號的。我喜歡優先把電源設計完成,保證足夠的通流能力,同時也能在訊號設計時考慮下訊號回流路徑的設計。當然,我們也是可以把電源地的處理放到後期來設計的。 |

|

5. |

模組佈線 |

按照各功能模組的布局,將其內部的訊號全部連接,同時將其與其他模組互連的訊號引出該模組的區域。這個設計步驟非常重要,如果此時我們遺留了一個訊號在模組中間,未將其引出,有可能會導致我們返工該模組的佈線。 |

|

6. |

模組間主要訊號佈線 |

將各模組之間的訊號連接。此時,需要考慮如何按照規劃完成這些訊號的實體互連,且要保證訊號完整性,比如回流路徑、過孔數量、阻抗突變等等。 |

|

7. |

其他訊號佈線 |

PCB 設計到最後,會有一些控制類或者偵測類的低速訊號,這些訊號佈線要求低,但是要確保他們都有連接通道。 |

|

8. |

線長調整 |

根據 SI 的設計,我們需要對一些訊號進行補償。我習慣在佈線完成後再來進行該調整。因為這時能夠看到佈線的實際效果,可以即時關注調整部分的訊號走向,避免出現跨分割、相鄰層重疊等設計。 |

|

9. |

添加測試點 |

給需要測試的網路添加測試點,其實就是替換過孔的過程,同時給測試過孔打上標誌。這個就是按照要求設計完成即可,沒有太多注意事項。 |

|

10. |

調整絲印 |

PCB 設計過程中,器件位置根據需要被調整,所以絲印也不會是整齊的。因此,設計完成後,我們就必須把它們擺放整齊,且不能錯位。這看似一個很簡單的工作,但是哪怕小小的失誤都會引起較嚴重的品質事故,導致單板報廢。所以,此階段需要耐心和細心。每個企業都會根據自身需要,或者行業要求在 PCB 上增加一些額外的文字,我們也需要確保這些文字清晰可見。 |

佈線階段至此結束。到此時,我們需確保網表是最新的,未擺放器件數為零,未連接數為零,規則管理器中的規則都得到滿足。

檢查階段

設計完成後,為了確保設計品質,我們需嚴格審查 PCB。我來分享一些從業時期的檢查心得,供大家參考。

1. |

後模擬驗證 |

|---|---|

設計完成後,針對關鍵訊號,需要進行後模擬驗證,以確認設計符合 SI/PI 的要求,確保訊號高品質傳遞。 |

|

2. |

規則審查 |

根據 SI / PI、DFx 等設計要求,檢查規則資料的正確性。在資料正確無誤的前提下,確保所有規則都得到滿足。 |

|

3. |

佈線優化 |

根據自己積累的 checklist,逐項檢查設計品質。這些檢查項包括多餘孔、冗餘走線、跨分割佈線等等。 |

|

4. |

工具輔助檢查 |

類似短斷路這樣的設計失誤,必須依賴於一些工具來檢查,人工很難發現。 |

品質保證的過程完成後,PCB 設計階段就結束了,PCB 可發到 PCB 廠家去加工,整個設計流程結束。

文章授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」