By John Burkhert Jr

大家也許已經遇到過或即將面臨這個問題:

一個全新的概念給團隊帶來了商機,但是為了節省時間而需要利用已有的設計來減少工作量。儘管單板外形可以重複使用,但是某個連接器的位置卻不能複用。

設計的生搬硬套非常困難,這無異於削足適履。

「一個新設計,無論是原創還是翻新,都需要良好的基礎。」

除了過度擁擠的問題之外,有時將全新或修改後的電路放入預設的形狀因素中,會比在電子器件周圍新建結構更加費力。這就好比與其改造一套不合心意的精品房,不如按照自己喜好裝修一套毛坯房來得容易。一般而言,我採取的 第一步措施是調研設計規則——檢查上一次反覆運算的密度指標,並讀取記錄新電路圖網表資料前後的引腳數量等內容,這讓我清楚地瞭解接下來的步驟。在這一步,單位面積的 pin 數 是我的技術指標 。而接下來的步驟重點請聽我逐一解釋——

1. 不破不立

注意打開、短路的數量以及網表導致的缺失的封裝是非常必要的。layout 的第一個實際操作是刪除導致違反設計規則(短路)的物件。不破不立,新的設計不需要相同的佈線;而定義了舊的射頻路徑及其所有接地過孔的精心設計的鋪銅恰恰是我們棄舊迎新的阻礙。但是請記住這點:當元件並未固定下來時,試圖保持同一的佈線會導致重複壓力損傷。

2. 全盤皆在

透過仔細刪除器件周圍的走線,再創建一個包含該器件本身及其 fan-out 和匹配電路元件的模組(module),我們可以移植整個器件。接下來我們在 X 和 / 或 Y 維度中按照既定量移動部件組,訣竅是要準確地知道移動的距離和方向。切記,在嘗試大幅度移動之前需要 保存資料。

下面針對器件必須被移動或成為可重用的候選物件的情況,我們來做一個演示:

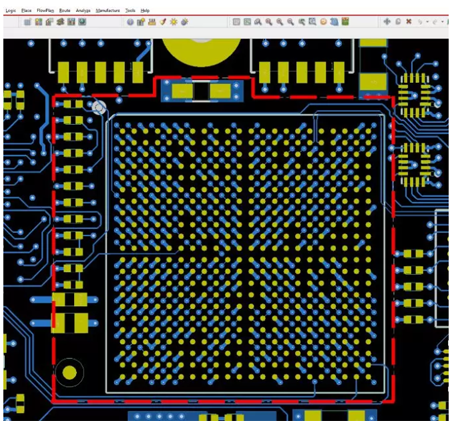

圖 1 - 我們希望保留的 fan-out 和離散器件的佈局

圖1 顯示了我們想要「切割」的器件。 紅色虛線內的所有內容都必須清除,即器件本身加上左側的元件列部分。

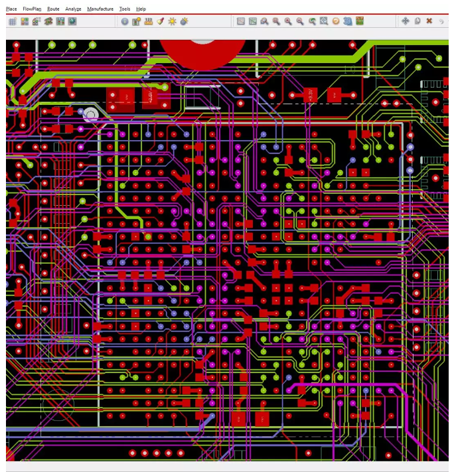

圖 2 - 表層下面有過多內容

然而表層下面的連線過多,大大增加了我們的操作難度。在這種情況下,我們可以逐層處理並刪除所有跨越虛線的走線;或者我們可以預覽每層,然後在其周邊進行四次簡單切割,從而順利取走想要的部分。

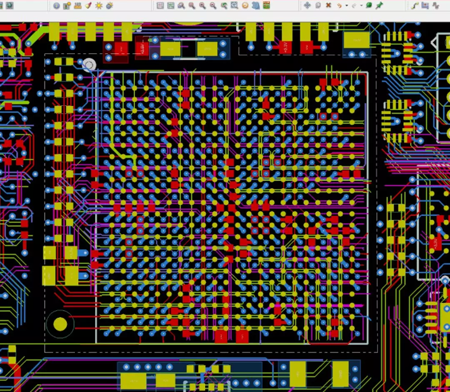

圖 3 – 準備移動的器件

現在,路徑已經清晰明顯,我們可以將整個器件重新放置。剩餘的走線由於與開始時的順序和層次相同,因此如果新位置相當接近,則連線可以一起恢復。我們此處沒有考慮電源,但將銅層重整為新拓撲結構的過程需使用 highlight 命令和創意多邊形功能。

3. ( 重新 ) 校準設計規則

一旦整體的晶片佈局概念獲得批准,我們就應該能夠具體化密度級別。IPC 識別三種級別並具有最小、標準和最大尺寸的設計規則。較大的焊盤可以為每個部件提供更大的空間,並且可以透過其寬大的焊盤尺寸來說明解決節點溫度問題,從而提高設計的可靠性。

但是由於大焊盤不能通過回流焊工藝保持元件的完美對齊,而容易引起裝配線的問題。請記住,切勿在同一塊板上混合不同密度的封裝,同一部件存在兩種焊料外形的情況將導致至少部分焊點出現問題。

4. 層疊驗證

現在我們已經為舊的電路板配備了新的元件組合和連接方案,下一步即要驗證舊的層疊。如果我們可以使用佈線通道將最複雜的器件 fan-out,我們的目的就達成了。但如果沒有改進的餘地,甚至發生訊號無法完全消除的情況,問題就變得棘手了。

這時候,我們就需要 與電路圖團隊進行有效溝通。通常而言,大多數問題的解決方案都需要更多而非更少的電路,我們也無法在發現問題之前解決問題。因此,在 layout 過程中進行中途改進是很正常的。但是為了最大程度降低問題的棘手度,我們能做到的便是預見這個可能並 在 placement 的時候,在各個地方留有餘量。

5. 「綠地」方法

「綠地」專案 -是指不受先前工作所施加的限制條件的專案。這是比擬在綠地上的建設中,不需在現有建築或基礎設施的約束下工作。

也許我們即將展開一個「綠地」項目:全新的電路板設計揭示了全新的產品外形,我們期望在某些位置具備新的安裝孔。這會使電路板原先寬裕的區域變得受限於封裝,同時又增加了連接器的數目。而其要點是—— PCB 正在往兩個方向發展:物理和電氣。團隊中的每個人都從設計小部件這樣一般而又模糊的概念開展項目,有時甚至直到項目的最後一天, 我們才透過反覆運算來確定最終的設計形式。

除了共同開發之外,我們已經達到了所有元件都能設計在電路板上的水準。Fan-out 研究或讓我們對舊的層疊設計富有信心,或為我們提供新的層疊設計;而不管怎樣,我們都因此實現了第一個進度目標。

6. 佈局

現在是時候進行關鍵電路高級模擬了。將風險元素定義為高速、寬頻和電源完整性這三大方面,使我們能夠在刻蝕任何銅之前透過虛擬反覆運算而保持領先。連接所有「特殊」網路,使 SI / PI 專家進行深入研究。設計的早期階段產生的種種不確定性問題,迫使我們使用現有技術來獲取對設計的性能見解;而在我們現有的設計技能中,模擬分析顯然是最關鍵的效率倍增器之一。

早在金拱門還是麥當勞的時候,其經營者有句名言適用於此:

「如果你有時間靠著休息,你就有時間打掃衛生」

這意味我們要在忙碌的間隙搞定小事。

當我們為模擬進行修改時,也是 瞭解絲印、裝配子面板和各種可交付成果的好時機。很可能 10% 的部件將被移動,參考指示器則必須在電路板完成時再次進行對齊。而這意味著,我們在關鍵的流片時間裡不需要在意其他 90% 的部件。在 layout 過程中巧妙地使用停工時間有助於推動我們的設計成功。

總結

一個新設計,無論是原創還是翻新,都需要良好的基礎。而該基礎的原則是圍繞設計需求,並將這些需求轉化為電氣約束和機械標準。最終佈局脫胎於一次次的揭露設計痛點的 fan-out 優化中,而這實際上就是要為 layout 付出大量的時間:有史以來最複雜的 PCB 設計就誕生於周而復始的失敗。

我們的工作始于清理舊部件並且要持續管理,這樣設計階段的後期工作才不會成為設計規則檢查的噩夢。將時間管理和專注於捕獲設計意圖(規則)作為佈局階段的一部分,會使我們(或自動佈線器)在解決其餘難題時處於有利位置。前期的努力付出不僅會在當下的設計中得到回報,更會在日後的工作中收穫額外的驚喜。良好的開始雖不能保證良好的結局,但糟糕的開頭則意味著出局無疑。明智地去選擇,讓我們一起笑到最後 。

文章授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」