科技已成為我們生活中不可或缺的一部分且正在不斷改變我們的世界。正因如此,系統設計變得更加複雜,為了確保性能、功能和可靠性,設計的模擬參數不斷增加。優化擁有眾多模擬參數的設計是一項極具挑戰性的工作,設計人員對此深有體會,因為這項任務需要耗費大量的計算資源、時間和成本。最終,這種方法將難以為繼。

試想一下,假設一項設計模擬有 10 個可控制的參數,而每個參數有 10 個可能的值。為了優化設計,我們必須查看所有可能的組合,也就是需要執行 100 億次模擬!如果採用傳統的人力密集型流程 (設計、測試和改進),這需要數十年才能完成。確保設計一次成功至關重要,而精確的電磁 (EM) 模擬是這一過程中的關鍵步驟,但這需要耗費大量時間。

用傳統的優化工作流程代替手動操作,能否實現真正的最優設計?

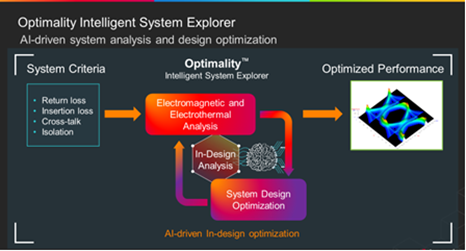

事實證明,針對任何規模或複雜程度的系統最優設計,我們可以利用 Cadence Joint Data and Analytics (JedAI) Platform 中使用的強化學習,非常快速地建立一個機器學習 (ML) 模型。Cadence Optimality Intelligent System Explorer 是一款生成式 AI 驅動的多物理場優化軟體,它採用人工智慧 (AI) 驅動的先進多學科分析和優化 (MDAO) 技術。

Optimality Intelligent Explorer 與 Clarity 3D Solver 和 Sigrity X 完全整合,Sigrity X 是 Cadence 的高速訊號與電源完整性 (SI/PI) 平臺。設計人員可以將系統級 SI 和 PI 模擬與分析負載轉移到 Optimality Explorer上運行,從而更快地實現設計優化,避免重新設計,整體上加快產品上市速度。

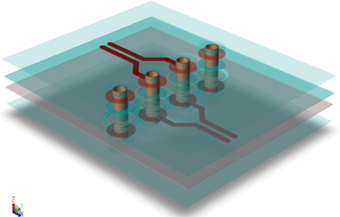

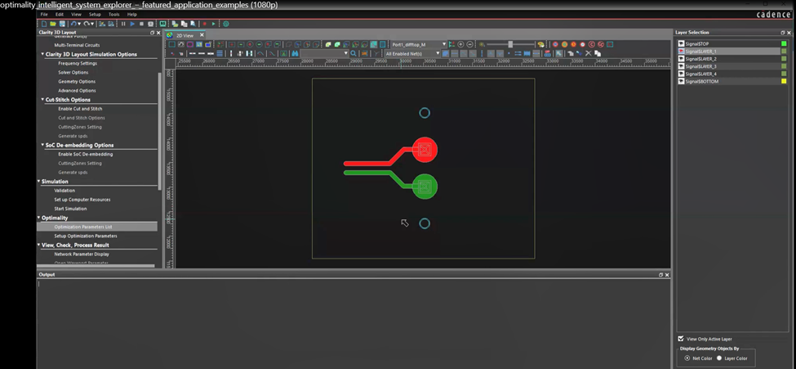

本文將透過一個簡單的測試案例,展示如何使用 Cadence Clarity 3D Solver 和Optimality Explorer 省時省力地優化差動對 (Differential Pair) 貫孔 (Via) 過渡。本例使用一塊 6 層基板的 PCB 板,GND 平面位於頂層、底層和第 3 層,差動對位於第 2 層和第 5 層,VDD 平面位於第 4 層電鍍通孔 (PTH),GND PTH Via 緊挨著訊號 Via。

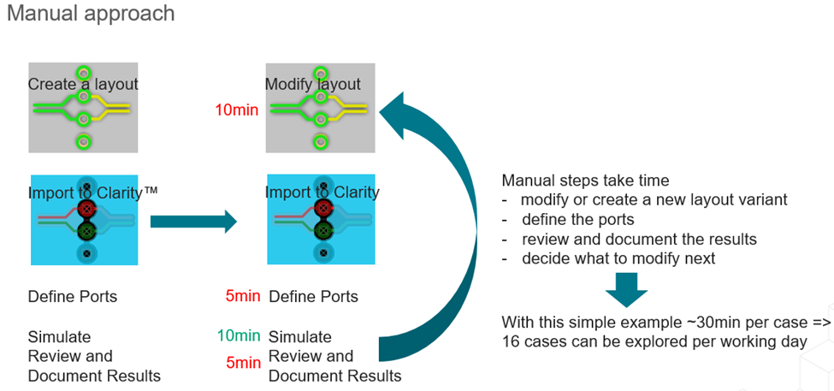

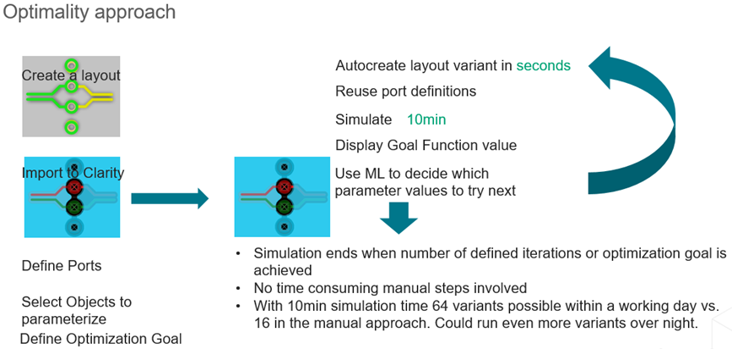

本例中,設計和分析目標是實現目標差分阻抗,並優化特定頻率下的低插入損耗 (S21) 和回波損耗 (S11)。我們使用 Optimality Explorer對 layout 進行參數化處理,以便瞭解如何修改才能改善設計性能;在與手動流程進行比較時,我們發現 Optimality Explorer 實現了設計流程的自動化,並能更早地完成設計收斂。如下圖所示,手動流程包括一個重複迴圈的流程:創建初始 layout、定義埠、運行模擬、記錄每種情況的結果,以及探索需要修改的內容。這不僅極為耗時,而且需要大量的手動操作。

Optimality Explorer 與 Clarity 3D Solver 相互配合,利用 AI 深度學習,能夠比蠻力計算更有效地找到解決方案。同時,Optimality Explorer 實現了流程自動化,無需人工干預;該流程包括定義要優化的參數和設定優化目標,然後自動創建 layout 並運行模擬,以實現優化目標。Optimality Explorer 支援多物理場模擬,減少了所需的模擬資料或模擬時間,能夠以更少的模擬次數實現設計收斂。

Optimality Explorer 方法的速度更快,無需人工干預即可通宵運行,為探索不同設計方案提供了一種更高效的方法。它適用於所有設計階段,如間距、返回路徑 Via 位置、平面開槽、鑽孔尺寸和隔離焊點 (Pad) 等,使用者可根據製造工藝的可行性探索這些參數的值。

工作原理 / 步驟:如何設置 Optimality Explorer 運行?

Optimality Explorer 是一款功能強大的工具,可實現設計流程自動化——它可以定義優化參數和變數,在設定的邊界條件內智能地選擇隨機值。它還可以為優化定義目標函數目標和函數類型。模擬完成後,使用者可以觀察圖表和收斂圖,以獲得最佳結果。如果對結果不滿意,可以重新開始模擬,繼續優化,直到達到預期結果。

利用 Optimality Explorer 可以更快地找到更好的解決方案。此外,範本功能可將設計變數自動添加到參數清單中,輕鬆優化佈線並保持所有設計層的一致性。即使在低頻範圍內,使用這種方法也能更高效地找到更好的解決方案。在返回路徑周圍放置 Via (訊號周圍的 Via) 可能非常複雜,尤其是在有微孔和埋孔的情況下。訊號從核心層到底層的過渡可能十分複雜。利用 Optimality Explorer 提供的功能,用戶可以快速分類和載入參數,比較最佳和最差的情況,並查看它們之間的顯著差異。在 Optimality Explorer的助力下,早期採用者已經成功優化了 Via 結構,改善了設計性能。

「我們是 Cadence Optimality Intelligent System Explorer 的早期採用者,在具有多個通孔結構和傳輸線的軟硬結合 PCB 板上,該工具性能卓越。Optimality Explorer 的 AI 驅動優化讓我們發現了新穎的設計和方法,而這些是我們利用其它工具無法實現的。Optimality Explorer 為原本就性能強大的 Clarity 3D Solver 增加了智慧,説明我們加速達成性能目標。」

— Kyle Chen,微軟首席硬體工程師

結論

業界需要轉變模式,摒棄過去重複「設計、測試和改進」這一迴圈的傳統流程,轉而採用生成式 AI 驅動的技術,在滿足時間限制的同時獲得優化設計。許多 SoC 設計師和 Optimality Intelligent System Explorer 的早期用戶現在都認為,傳統的人力密集型優化流程已經退出歷史舞臺。Optimality Explorer 能夠説明設計團隊優化設計,在設計流程的早期更快地發現和緩解熱問題,大大縮短了實現真正的優化設計反覆運算所需的時間。它使設計工程師能夠探索 3D 電磁 (EM) 和高速訊號及電源完整性的結果,鎖定最佳設計。它可説明設計團隊在不影響準確度的情況下,加快電子系統的分析和優化,輕鬆分析和優化 3D 電磁 (EM) 以及高速訊號和電源完整性結果。

譯文授權轉載出處 (Graser 偕同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」