By Ken Willis, Cadence

假設我們正在致力於 PCI Express Gen 4 串列鏈路的研發,資料的傳輸速率為 16Gbps。再假設我們能夠獲得供應商提供的 AC 耦合電容、封裝和連接器的模型,以及來自 SerDes 接收端的 IBIS-AMI 模型。接下來還需要PCB 的走線和過孔模型,以及發射端的 IBIS-AMI 模型。假設供應商暫時無法提供這些資料,那就讓我們先來解決 PCB 架構的問題吧。

PCB 互連的預佈局建模

PCB 走線的建模可以從獲取層疊結構開始,包括串聯鏈路差分對的材料、電介質和導體厚度、阻抗、線寬以及間距。接下來,需要確定串列鏈路(通常與接地層相鄰)的主要佈線層,以便您可以生成適用的微帶線或帶狀線模型。有了這些資訊,下一步就是估算互連的長度。從這個層面上來講,「佈局規劃或 PCB 的粗略佈局是很有用的。您可以透過平面佈局工具輸入基本的 PCB 輪廓、層疊結構,從封裝庫中提取部件,甚至可以定義一些簡單的網路,所有這些都沒有一個正式的設計、完整的電路圖或網表。

佈局規劃時,不要忘記 AC 耦合電容。它們將被放置於電路板的頂層、在 SerDes 器件附近、還是與大部分其它分立元件一起位於電路板的背面?這種選擇會導致不同的過孔配置,所以在這一點上需要仔細考慮。在整個系統設計中,表面貼裝連接器也屬於這一類。

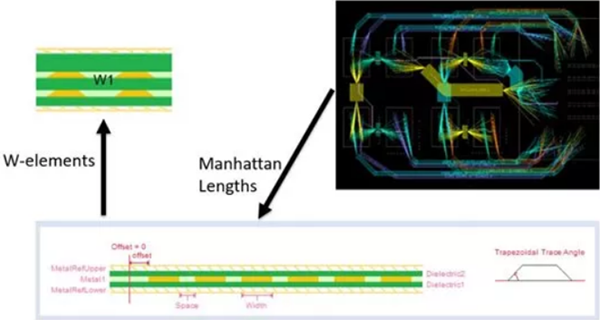

從平面佈局中,找到串列鏈路的曼哈頓長度作為初始的 PCB 長度。將這些資訊輸入到 SI 工具中,為 PCB 的主要佈線生成一個 W-element 模型,並將其放入 SI 的模擬平臺。

圖 1:提取平面佈局的曼哈頓長度進行佈線前的走線建模

對模擬平臺所需的其他走線模型也重複此過程,包括微帶線的扇出走線、連接到 AC 耦合電容任一側的走線等。

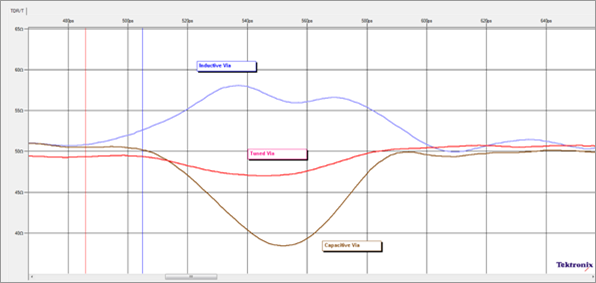

使用 PCB 上的通用走線模型後,我們將開始關注過孔。過孔是板上幾十或數十億位元串列鏈路的重要組成部分。它們通常代表整個信號路徑中最大的「速度突變點」,優化這些過孔設計使其插損和回損最小,對高速率傳輸資料至關重要。在特殊情況下,可能通過僅有微帶線的佈線消除過孔,但通常不會這樣做。高資料速率串列鏈路的過孔數量當然應該儘量減少,但通常無法被完全消除。

圖 2:過孔不連續性「速度起伏」(Tektronix提供)

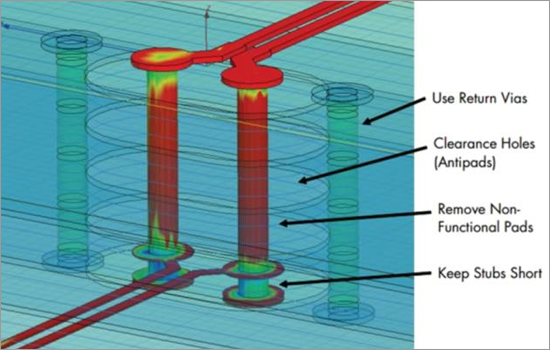

鑽孔直徑、焊盤尺寸、反焊盤設計以及接地通孔都是設計中的關鍵因素。過孔的一個重要考慮因素是分支線長度,或者說是信號過孔的未使用部分,這可能引起通道中信號的反射。透過仔細選擇佈線層、利用盲孔或背鑽等技術可以有效的控制分支線的長度。

圖 3:透過結構參數進行優化

關鍵參數的自動掃描可以顯著加快串列鏈路的過孔優化設計。一旦確定了所需的過孔結構,就需要確認並將其應用在 PCB 的佈線當中。傳遞這些過孔設計參數的自動化機制是非常有效的,可以確保它們在物理佈局中按照預期實現,成為「正確的設計」,並且使過孔對最終眼圖的影響最小化。

延伸閱讀

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」