作為一名射頻前端設計的工程師,大家肯定都有過這樣的疑惑:我究竟是做 IC 設計的,還是做板級電路設計的?如果是前者,為什麼我們做模擬不跑 corner,不跑蒙地卡羅,甚至連個精確的電晶體模型都沒有,每天要花大量的時間在實驗室裡面做調試工作。錫膏、烙鐵、鑷子是我們每天都要見到的好朋友。如果是後者,我交付給客戶的必須是一片沒有任何瑕疵的晶片,每一個管腳都要正確定義,每一個指標都要嚴格過關,甚至還要說明客戶負責週邊電路的設計和調試。

但不知大家想過沒有:我們為什麼會有這樣的疑惑?為什麼我們不能像普通的 CMOS 積體電路設計流程那樣:搭框架 -> 跑模擬 -> 調參數 -> 投片 - > 封裝測試 -> 交付?為什麼我們不能把主要的設計精力花在模擬階段,透過對電路的精確設計和參數的精准把握定位問題、分析問題、解決問題。而需要花費大量的精力在實驗室裡面,面對各種未知的情況,透過反復的預估、猜想、驗證來進行調試?而大量測試儀器的花費,也是一筆不小的開支。

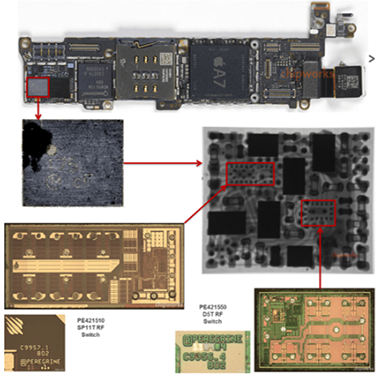

圖 1:繁瑣的實驗室調試

面對摩爾定律的終結,異質積體電路由於其優良的性能及強大的相容性越來越被業界重視。作為異質積體電路的先驅,射頻前端模組一直是其中最重要的一個組成部分。麻雀雖小,五臟俱全。一個幾毫米乘幾毫米的前端模組裡面,包含了好幾種不同工藝的裸片:CMOS、GaAs、SMD、SOI、IPD、MEMS 等等。而從數量上來講,好幾片甚至十幾片尺寸不同、材料不同、厚度不同甚至封裝工藝不同的裸片要放到一個封裝中,還要通過各種高低溫可靠性測試,這無論對設計者還是封裝測試的人來講,都是一個極大的挑戰。

圖 2:不同工藝裸片構成的前端整合模組

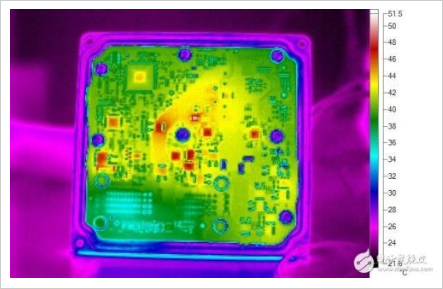

而從電路模擬上來講,無論是晶圓廠、基板廠還是封裝廠,甚至小到一個普通的 SMD 器件的生產廠商,都無法從根本上提供一個精確而有快速的模擬模型。一是因為射頻功率電路本身的複雜性,電路的性能與其存在的環境密切相關:電磁環境、熱環境、材料環境等等。單單靠某一廠商的努力,即使提供了所謂精確的模擬模型,也無法保證在實驗室或者客戶的環境下的各種性能優良。二是因為本身模型提取的難度,因為無論器件的 RF 模型還是熱模型,都與電路的 Layout 密切相關。而如何定義模型與模擬工具的邊界也是一個業界的難題。

圖 3:電路工作中複雜的電熱環境

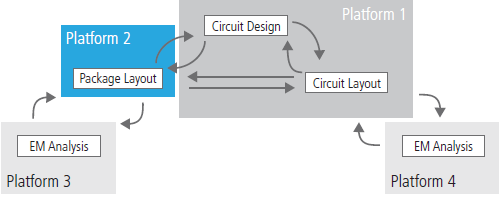

同時,也有一些 EDA 工具廠商針對這些問題給出了一些解決方案。但目前依舊沒有任何一個完整的設計模擬平台能夠將這些設計、模擬、版圖工作放到一個統一的整合環境下來完成。工程師需要在不同的工具平台間不停切換,進行大量的資料導入匯出的工作。這也是一個費時費力的工作,大大降低了工程師的工作效率。

圖 4:前端射頻模組設計中需要不同設計模擬平台之間的切換

由此可見,要想在模擬階段完成主要的射頻前端電路的設計,需要整個業界的共同努力。而作為 EDA 行業的領跑者,Cadence 目前推出一款基於 Virtuoso 平台的射頻前端全整合設計模擬工具,針對射頻前端設計的各種問題,基本解決了從設計到模擬的一體化問題。並與各大晶圓廠合作,共同研發與他們工具相容的器件模型及 PDK,從而達到真正的協同模擬。

關於如何利用 Virtuoso 平台實現這一目標,我們將在未來幾篇文章中陸續探討,請大家繼續關注。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」