本文要點

阻抗不匹配會導致平行網路出現訊號反射和不同步現象,從而導致接收器上出現位元錯誤。 |

|

要快速識別阻抗超標,需要在 PCB 設計工具中使用規則管理器,然後在設計規則中設置阻抗限制和公差。 |

|

佈線後模擬工具可用於檢查不符合阻抗規則的網路,並確定哪些區域的設計應該更改。 |

透過規則管理來控制阻抗,準確發現訊號反射

走線阻抗控制主要在於確保走線的尺寸大小合適。如果獨立考慮一條走線,其阻抗值是很明確的。但是,當它靠近另一條走線或導體時,由於意外耦合作用,該走線的阻抗將與最初的設計值不同。這個問題非常棘手,會導致沿著互連的阻抗變化不定,而傳輸線和接收器之間的極端阻抗不匹配將導致訊號反射。

儘管我們已根據最佳實踐對 PCB layout 進行了佈線,並且佈線的走線寬度全部符合設計值,但是互連中也有可能出現阻抗變化。這時就需要使用規則驅動設計,即,在對 layout 進行佈線時,根據設計規則來檢查電路板。如果要處理一塊工藝比較陳舊的電路板,那麼就需要分批檢查阻抗;為此,可以運行一個批次處理設計規則檢查 (DRC),一目了然地瀏覽阻抗超標情況。

要糾正整個電路板上的阻抗錯誤,Sigrity 的佈線後模擬功能可以助我們一臂之力,用以分析整個單端和差分互連的阻抗。同時,還可以發現互連線上特定位置的訊號反射,如貫孔或連接器過渡處。在下文中,我們將介紹如何使用 Allegro PCB layout 工具和 Sigrity 分析功能。

定義阻抗控制的規則

阻抗控制的目的是確保 PCB 上的走線在每個互連中的幾何形狀都是一致的。該方法適用於單端和差動訊號對佈線。為此,需要遵循我們的高速訊號標準來定義這些約束規則,而這些訊號標準又取決於所選的零件或設計的介面類型。

PCB 設計軟體的適應性很強,確保使用者能夠定義任何物理和電氣規則,以符合可製造性設計 (DFM) 要求和訊號標準。Allegro 提供的設計工具允許使用者使用 Allegro 規則管理器來定義所需的阻抗值和公差。此工具可在 Allegro PCB Designer 或 Allegro Sigrity SI 內使用。

對四個阻抗控制網路進行分析

在接下來的例子中,我們將討論如何定義和檢查現有 layout 中一組網路的阻抗規則。如上圖所示,這四個要檢查的網路是 DDR3 資料匯流排的一部分,定義的阻抗是 34 歐姆。此時,我們要檢查這些走線的阻抗是否在 JEDEC 標準的限制範圍內,以及在這些走線上是否會發生過度的訊號反射。

定義規則

在開始定義規則之前,我們需要確定規則定義是針對單個網路,還是針對一組網路。Allegro PCB Designer 允許使用者將幾個網路劃分到一個網路組,因此可以將同一組設計規則分配至整個網路組。請注意,不是必須要將網路分配到網路組;一個網路也可以有自己的設計規則和約束。所有設計規則都可以在 Allegro 規則管理器中訪問、查看和編輯。

要訪問 Allegro Constraint Manager 並定義電路板中的約束規則,請在 Allegro Sigrity SI 中打開 .BRD 文件。按一下 Setup 選單並找到 Constraints → Constraint Manager。打開 Constraint Manager 後,可以從螢幕左側的面板上訪問基於網路組和基於網路的電氣規則。

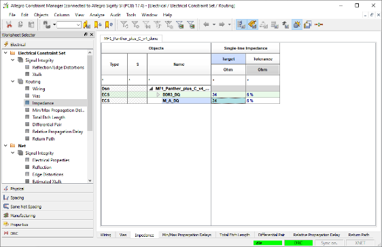

要為一個網路組設置阻抗規則,請打開 Electrical Constraint Set 選項,然後找到 Routing → Impedance。下圖是在該電路板上定義的兩個網路組。這兩個網路組都是 DDR3 介面的一部分,因此該介面上的走線阻抗應該設置為 34 歐姆 (Ohms)。阻抗公差設置為 5%。

網路組的阻抗規則。

我們要檢查的四條走線不屬於這些網路組,但如有需要,我們可以將這些走線分配到這些網路組。另一種方法是在 Electrical Constraint Set 中為這些走線單獨定義阻抗規則。為此,只需在 Constraint Manager 中向下滾動到電氣工作表中的 Net 部分。打開 Routing → Impedance 部分後,就可以查看所有的網路以及它們屬於哪個網路組。

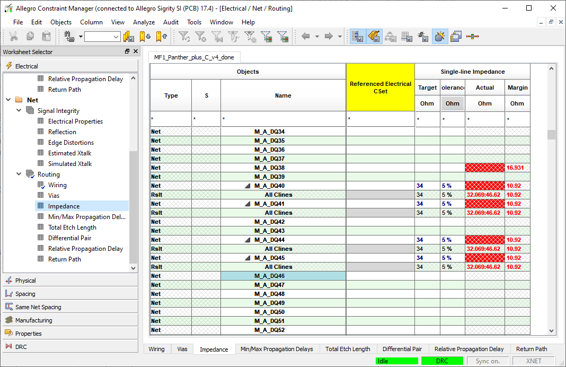

如果我們想把一個網路分配到電氣規則集,只需在 Referenced Electrical C Set 一欄下打開下拉式功能表,選擇所需的電氣規則集。現在,我們要把目標阻抗值分配到要檢查的各個網路。從下圖中可以看到,目標阻抗設置為 34 歐姆,阻抗公差為 5%。定義目標阻抗值之後,我們就會看到相應的網路被標記為紅色。如果該網路沒有立即顯示標記,只需從工具列運行設計規則檢查 (在 Tools 選單下選擇 Update DRC)。

各個網路的阻抗規則。

在上圖中,這四個網路被標記為了紅色,因為它們的最小阻抗和 / 或平均阻抗超出了 34±5% 的範圍(32.3-35.7 歐姆)。Constraint Manager 顯示,阻抗範圍為 32.069-46.62 歐姆;這些值可能出現在這些網路的任何位置。造成這種現象的原因包括與其他導體產生意外的寄生耦合、走線寬度不一致,或在參考平面的間隙上進行佈線。

請注意,Allegro Constraint Manager 還支援為 PCB 定義其他幾種物理和電氣規則。物理規則包括焊盤和走線間距,而電氣規則包括傳播延遲限制和返回路徑跟蹤。

確定違反設計規則的網路之後,就可以進一步瞭解到底是設計的哪些部分導致設計規則超標。另一種查看規則超標的方法是使用工具功能表中的 DRC Browser。該工具可以顯示電路板中超出設計規則的座標,並在不同的類別中標記出具體的規則超標專案。超標列表可能讓人有點眼花繚亂,但不必擔心,Allegro 提供了視覺化工具來顯示規則超標。這涉及到使用 layout 資料進行佈線後模擬。

運行阻抗和反射模擬

現在,我們已經準備好糾正電路板中的阻抗不匹配,要完成此操作,可以使用 Allegro 中的訊號完整性分析功能來發現阻抗變化並識別存在反射的位置。首先,在 Allegro 中打開電路板,點擊 Analyze 功能表,並選擇 Workflow Manager 選項。隨後螢幕上會顯示幾個可供執行的分析,包括 Impedance Workflow 和 Reflection Workflow。

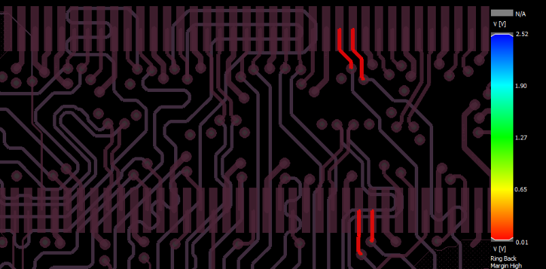

首先,選擇 Reflection Workflow 和要檢查的目標網路。選擇目標網路後,點擊 Start Analysis,開始模擬。模擬完成後,可以點擊 Reflection Vision 查看熱圖,熱圖中標出了網路上出現反射的位置。我們也可以點擊 Reflection Table 來查看具體的上沖/下沖值以及它們在電路板上的座標。在本例中的電路板上處理的是 DDR 線路,因此可以在 Reflection Table 中將這些值與 JEDEC 規範進行比較。

下圖是本例中四個網路的反射結果。從圖中可以看到,反射主要發生在零件焊盤上。相應的值以紅色標記,並且只產生了約 10 mV 的振鈴現象。在互連上很早就可以看到 30 mV 的振鈴,但用 Reflection Vision 工具不容易進行視覺化;需要按兩下阻抗表中的相應表單才能看到這些結果。

Reflection Workflow 結果

沿著這些網路出現了 30 mV 的振鈴,它們發生在靠近走線的多個點附近,相應的走線片段如之前的圖片所示。Impedance Workflow 分析有助於理解這些反射現象,它們是由沿互連線的阻抗變化而引起的,以視覺化的方式查看會更為直觀。

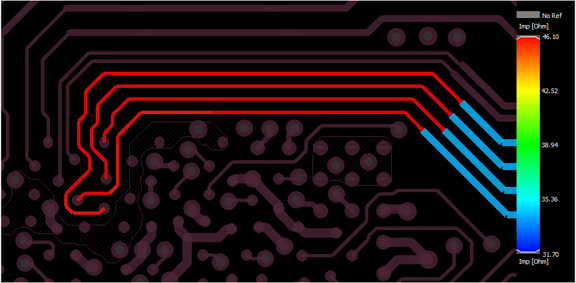

要檢查阻抗變化,請選擇分析工具列中的 Impedance Workflow 選項。選擇相同的網路進行分析並運行模擬。選擇 Impedance Vision 選項,可以查看整個互連的阻抗,同時也會顯示熱圖,其中阻抗值以不同的顏色表示。

四個網路的阻抗變化

從圖中我們可以直接看到,阻抗從約 46 歐姆突然過渡到約 34 歐姆,和 Allegro Constraint Manager 中顯示的資料相同。從紅色部分和藍色部分之間的長度變化可以明顯看出這一點。這對應於網路中具有較高上沖的區域。下一步是將訊號上沖和阻抗變化與訊號標準進行比較。這些網路的紅色部分對應 FPGA 上的 BGA 扇出部分,所以要限制扇出部分的寬度,防止出現過度的訊號反射和損失。

我們可以採用與上文相同的模擬步驟來檢查電路板中的不同網路對。只需選擇網路對的兩端,確保整個電路板的差動阻抗保持一致。對於差動對,還需要檢查是否符合長度匹配公差,該公差可以在 Allegro Constraint Manager 中定義。然後可以使用 DRC Browser 來確定哪裡發生了長度不匹配的情況,佈線工具可以對標準的長度匹配片段進行佈線,保持差動對同步。

Allegro 設計工具現已發佈至 22.1 版本,新版本中的許多功能都做了進一步增強,特別是在高速結構相關功能上,更加人性化、智慧化,同時更符合設計人員的需求;模組複用也越來越普遍,符合設計要求的查詢也經常出現在設計的 Layout 中。

想要進一步瞭解 Allegro SPB 22.1 的新功能以及諸多實用小技巧嗎?

歡迎點擊【 由繁入簡,輕鬆上手 Allegro / OrCAD 22.1 新功能 】免費觀看重播影片,快速掌握 Allegro SPB 22.1 新版本應用訣竅,縮短學習曲線,提升 PCB 設計效率!

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」