在數位系統中,PCB 的電源分配網路 (power delivery network,即 PDN) 需要在較寬的頻率範圍內具有較低的阻抗值,以確保在數位器件運行時,電壓波動能保持在較低水準。決定 PDN 阻抗的因素有很多,不單單是數位處理器中用於穩定功率輸出的電容器。在工作頻率達到 GHz 級別的先進系統中,PDN 阻抗不僅受到電容器的影響,還有很多因素會決定 PDN 阻抗,即便在非常高的頻率下也是如此。

SMD 電容器 (頻率範圍最高 10-100 MHz)

電容器是決定 PDN 阻抗並確保穩定功率傳輸的主要元件。大多數市售電容器都能保持較低的 PDN 阻抗,但它們所能達到的頻率範圍取決於以下多種因素:

電容值 |

|

ESR 和 ESL 值 (決定自諧振頻率) |

|

SMD 電容器外殼尺寸 |

要判斷電容器能否確保 PDN 阻抗維持在較低水準,最終考慮的頻率範圍是電容器的自諧振頻率範圍。總體來說,較小的外殼尺寸和較低的電容值可提供較高的自諧振頻率。

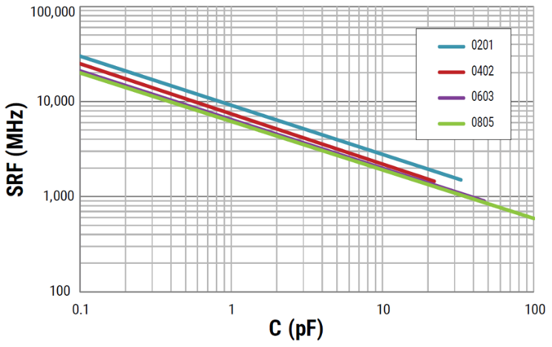

有些電容器是專門針對非常高的頻率設計的,如 RF 電路中使用的電容器。讓我們透過一個例子來瞭解一下這些電容器開始產生電感的頻率範圍。我們可以看到,這些電容器的自諧振頻率因外殼尺寸而異,可以達到非常高的數值 (理論上而言) 。實際上,並非所有電容器都能達到如下所示的極高諧振頻率。我們將在下文中詳細說明。

不同外殼尺寸下高頻電容器的自諧振頻率變化趨勢。

平面對 (頻率範圍接近 100 MHz-1 GHz)

當 PDN 阻抗曲線接近 100 MHz 的範圍時,電容器將停止供電,而 PDN 阻抗曲線將由平面電容決定。當數位系統需要較大的電流時,會使用電源-接地平面對,這樣也是為了提供較高的電容,以便在極高的諧振頻率下仍能保持電容阻抗。平面的功率輸出能力取決於電源-接地平面對中的擴散電感 (spreading inductance)。

最終,在非常高的頻率 (數十 Ghz) 下,平面將開始共振並從邊緣散發輻射。這時,平面對中的材料選擇和電介質厚度成為影響 PDN 阻抗和雜訊發射的主要因素。

封裝 (頻率範圍從 100 MHz 到 1 GHz)

先進數位零件的封裝可包含自身的電容,以便在 GHz 範圍內以較低的阻抗傳輸功率。這些零件可對 PCB 上的平面對進行補償,因為平面對在 GHz 頻率下可能會產生電感。此類封裝包括片式電容器,可能還包括嵌入式電容器,以確保穩定的功率傳輸和較低的 PDN 阻抗,直接作用於零件封裝中的半導體裸晶(die)。將這些電容直接置於封裝上,可避免 PCB 上的焊盤 (pads) 和貫孔 (vias) 產生電感,還可避免 BGA/LGA 封裝中的接腳電感。

CPU 封裝可包含自身的 PDN 元件,以便在低阻抗下實現功率傳輸。

裸晶電容 (頻率範圍大約在 1 GHz 以上)

半導體裸晶可提供自身的電容,通常在裸晶上直接提供總計 pF 級別的電容。該電容的好處是直接位於裸晶上,電感極小,可為數位介面供電。這是在 1 GHz 或以上的頻率下提供電容的最佳用例,以便支援速度最快的數位介面。

PCB 材料 (所有頻率)

任何 PCB 材料都會影響電磁波的傳播,從而影響 PDN 阻抗曲線。我們在上文介紹電源-接地平面對時說過,在數十 GHz 頻率下,平面區域會像平行板諧振器一樣開始共振。

為確保電源-接地平面對發揮最大作用,分隔二者的材料應具備一些重要特性:

首選高 Dk 值的材料,因為它們能提供更高的電容 |

|

損耗正切值適中或較高,以抑制噪音 |

|

首選薄層材料,以獲得更高的電容和更高的諧振截止頻率 |

使用非常薄的高 Dk 值電介質 (如嵌入式電容材料) ,可以減少振盪 PDN 的輻射發射,並提高總平面電容。這些材料的成本較高,但在高頻寬、高功率的數位系統中卻經常需要。

總結

我們透過下表總結了 PDN 的各個部分及其對頻率的影響。

| PDN 元件 | 頻率範圍 |

|---|---|

電容器 |

• 頻率最高 10-100 MHz • 受自諧振頻率限制 • 電容器陣列會產生電感 |

平面對 |

• 頻率接近 100 MHz-1 GHz • 決定電源 / 接地平面之間的平面電容 |

封裝 |

• 頻率接近 100 MHz-1 GHz • 封裝內電容可針對非常高的頻率 |

裸晶電容 |

• 頻率高於 1 GHz • 電容內置於半導體裸晶中 |

材料 |

• 影響所有頻率 • 影響電源平面 EMI 輻射的吸收 • 決定平面電容 • 決定 GHz 範圍內的平面共振 |

電源完整性的最後一個關鍵因素與 PCB 完全無關,這個因素是電源穩壓器或 VRM 的頻率回應能力。VRM 電路透過控制環路確保穩定的輸出電壓,而 VRM 的頻率回應需要足夠快,以便抑制功率輸出可能存在的雜訊。如果電源軌上出現快速暫態,VRM 就不能進入持續振盪狀態。在為大型數位處理器設計高電流/低電壓電源穩壓器時,暫態下的測量值應滿足要求。

PDN 阻抗設計是一項挑戰,但瞭解 PDN 阻抗的頻率範圍可幫助設計人員做出正確的工程設計選擇,以實現較低的 PDN 阻抗。

譯文授權轉載出處 (Graser 偕同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」