為了應對運算密集型工作負載,資料中心產業領域趨勢正在向異構運算發展。該趨勢同時推動著相應軟體解決方案的開發,以便在具有不同核心和記憶體配置的多台電腦之間分配工作負載。伴隨著高速運算而來的是對高速資料傳輸的需求:PCIe 匯流排是一種針對資料傳輸的關鍵性促成技術,其最新一代標準(4.0/5.0)大大提升了頻寬並降低了延遲。

儘管從資料輸送量的角度來看這很有吸引力,但是這些性能方面的提升也帶來了巨大的信號完整性(SI)設計挑戰。為了應對 PCIe 4.0/5.0 合規性測試,設計人員如今必須滿足非常嚴苛的性能要求,例如誤碼率(BER)測試(32 GT/s 的性能,帶 NRZ 信令)。隨著早期版本的 PCIe 6.0 仍跟隨這一潮流,這種趨勢似乎只會使這一挑戰愈發升級。設計板反覆運算和驗證測試不僅耗時而且成本高昂,也就不足為奇了。工程師們需要謹慎設計並測試高速 PCIe 序列連接的互連設計。

在以下應用中,我們將討論與信號完整性相關的 PCIe 4.0/5.0 設計挑戰。此外,還將進一步介紹關於設計人員如何利用先進的 CAD 工具來應對這些挑戰的深入見解。

圖 1:基於 PCIe 的高性能顯卡

詳細瞭解 PCIe 4.0/5.0 要求和合規性測試

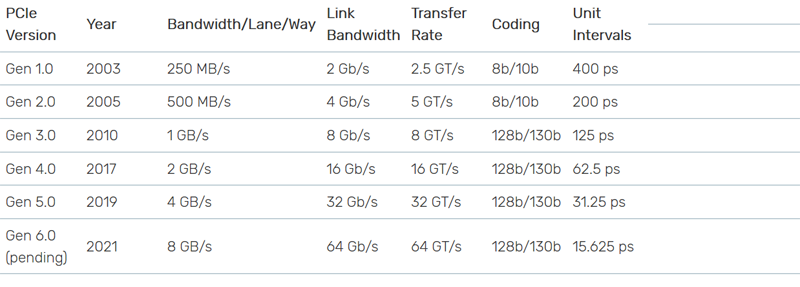

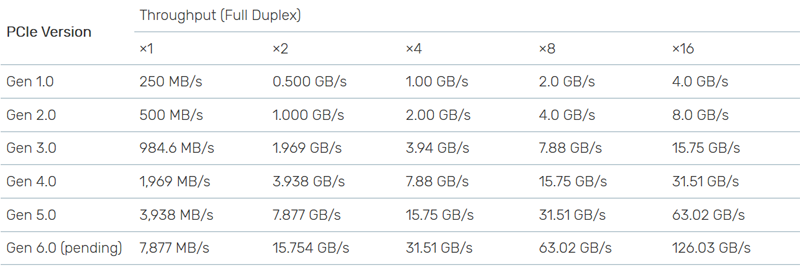

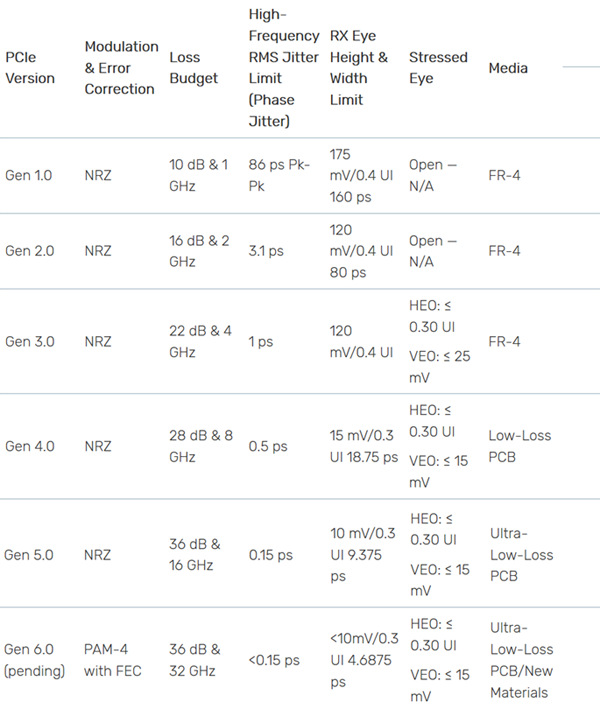

對電腦週邊更高的輸送量和性能需求,導致每一代 PCIe 都將頻寬和傳輸速率翻倍,同時將單位時間間隔減半。提高 PCIe 傳輸速率是資料中心應用擴充記憶體、存儲和互連頻寬的必然結果,因為每個 CPU 上的處理器整合的加速器越來越多。為了提高傳輸速率和頻寬,將產生更高頻率的信號。PCB 上導電走線的損耗量是走線上信號頻率的函數,這就意味著在較高頻率(即較高輸送量)下的損耗將會大於較低頻率下的損耗。

因此,PCI-SIG 必須提高實體層規格,並在每一代 PCIe 標準的最大傳輸速率的奈奎斯特頻率(Nyquist frequency)下加大損耗預算,同時降低可接受的抖動和眼圖高/寬限制(眼圖特徵)。從 PCIe 3.0 到 4.0 的過渡中,需要改用低損耗的 PCB 基板,以滿足新的規格要求。考量到容差越來越小,超低損耗 PCB 基板便成了實現 PCIe 5.0 要求的關鍵性工具。

儘管高性能 PCB 基板的介質損耗和色散遠低於標準 FR4,但滿足 PCIe 4.0/5.0 的要求對許多設計人員來說仍然是一個挑戰。PCIe 設計的通道損耗、通道不連續性和串擾會導致系統雜訊加大、眼圖閉合以及防抖動性能變差。要將 BER 保持在 1 萬億位元分之一的錯誤率以下(10 – 12 的誤碼率),就要求設計人員在物理和電氣設計的每個環節都做到謹慎管理預算:這包括將封裝和電路板設計中的損耗降至最低,同時還要考慮到其他 SI 性能要求。

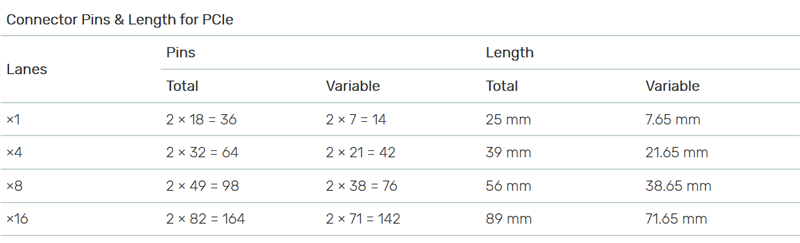

降低高頻下較大通道損耗的一種特定方法是使用接收器均衡和發射器去加重。由於 PCIe 4.0/5.0 被認為是閉合眼圖標準,這意味著通道的 SI將加劇符號間干擾,同時即使發射機顯示零抖動,也會迫使眼圖閉合;因此需要透過連接均衡來使眼圖張開。PCIe 3.0 開始之後還使用了長距傳輸擴展工具,如重計時器(retimers) 和重驅動器(redrivers),以便為伺服器和存儲系統提供更長的物理通道傳輸。當通道的物理長度超出 PCIe 規格時,擴展工具是必要的,這種情況通常發生在 PCIe 4.0 系統中,此等系統採用多連接器拓撲結構、電纜拓撲結構和單連接器內插卡拓撲結構,具有 9.5 英寸以上長度的底板通道和中等損耗的 PCB 基板。

在設計 PCIe 4.0/5.0 時考慮信號完整性挑戰

均衡、去加重和範圍擴展工具的有效性和設計取決於對通道的理解程度和對通道公差的嚴格程度。為了獲得此類資訊,精確的建模和物理設計是必不可少的。然而,對高速數位通道進行表徵和建模並不是一件容易的事情,即使是微小的誤差也會對高速信號的 SI 產生重大影響。

其主要原因是導電走線固有的電感和電容寄生值,以及這些走線周圍的絕緣材料對寄生值產生怎樣的影響。此外,PCB 生產公差儘管很小,但並不會完美。走線和絕緣材料尺寸變化產生的誤差,足以使寄生模型有失精准。另一個需要考慮的因素是 PCIe 通道並不是隔離的,並且通道的走線與附近的所有導電結構都會產生電耦合。這就意味著數學模型、2D 模擬和近似值通常都太不準確,無法正確預測寄生值以滿足 PCIe 4.0/5.0 代標準的要求。

推薦閱讀 PCB 設計同步分析 6 大隱藏技巧二 :訊號耦合干擾快篩

即使針對特定 PCB 物理設計的寄生提取是準確的,寄生值也可能不在 PCIe 增強的信號完整性電路和系統的最佳範圍內。優化走線和結構以儘量減小寄生值是最常見的方法,這通常需要進行複雜的參數分析,然後必須將分析結果回饋到模擬器,以確定物理結構是否滿足 PCIe 電路的要求。

由於寄生提取和走線優化技術通常很容易出錯,因此設計人員會定期對產品原型和物理設計進行反覆運算測試,直到設計佈局在 PCIe 增強的信號完整性電路的公差範圍內產生通道特性。這種嚴格的測試要麼需要對各種物理設計進行批量測試,要麼需要進行一系列的設計調整,無疑都會給設計過程帶來極大的延遲和成本。

在 PCB 設計中使用真正的整體的 3D 電磁場求解器縮短設計週期並提高性能

要規避與 PCIe 通道物理設計相關的反覆運算測試帶來的延遲,可以使用真正的整體的 3D 電磁場求解器,該求解器是為適應大型 PCB 結構的模擬而構建的。如果設置得當,3D 電磁求解器可以更準確地預測走線寄生值,並以易於集成到電路模擬器中的格式輸出結果。此外,具有足夠高的精度和速度來擷取小尺寸的 3D 電磁求解器甚至可以用於提供 IC 封裝和 PCB 走線的電磁模擬。與將透過不同 IC 和 PCB 寄生提取方法得到的結果串聯在一起相比,這種方法能夠更加精確和完整地展現寄生行為和通道特性。另外,對大型 PCB 結構以及小型 IC 封裝和電路結構進行完整的模擬,與將模擬分為多個部分、再分別進行模擬然後合併相比,可以生成誤差更小的模型。後一方法面臨的挑戰是所擁有的 3D 電磁求解器,速度和容量都不足以及時完成模擬操作。

推薦閱讀 視頻解密 | Clarity 如何為系統分析和設計提供前所未有的性能及容量

此外,值得注意的是,能夠執行參數優化的 3D 電磁場求解器可用於自動收斂到符合設計要求並考慮到工藝變化和其他生產公差變化的 PCB 物理設計中。借助容量足夠高、速度足夠快的 3D 電磁場求解器,可以顯著減少物理佈局和原型測試過程所需的時間和反覆運算次數,而傳統方法則難以實現高速數位信號所需的 SI 性能指標。

圖 2:與近似值和簡化模型相比,擁有足夠容量的精確 3D 模擬工具可以生成與 PCIe 通道特性的實驗資料更好匹配的模型。

Cadence 公司設計流程助力您成功通過 PCIe 合規性認證

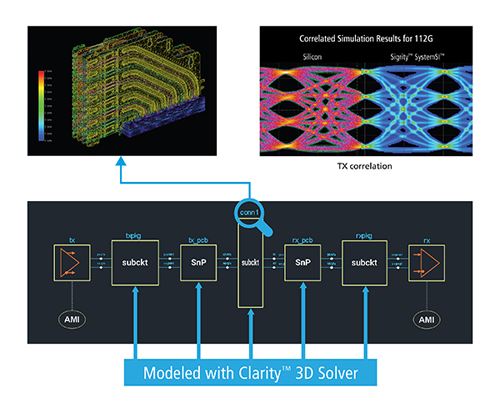

Cadence Clarity™ 3D Solver 不僅可以實現上述功能,同時還囊括了其他一些協助工具,有助於節省設計階段並具備黃金標準的模擬精度。與依賴單個計算節點的求解器相比,憑藉分散式多處理技術,Clarity 3D Solver 可以更迅速地應用於具有廣泛幾何變化的極其複雜和精細物理結構的模擬分析中。更多的處理資源可使 3D 求解器能夠為信號完整性(SI)、電源完整性(PI)和電磁相容性(EMC)分析提供更精確的模型,並且無需對結構進行近似或降級,從而對,「模擬器更加友好」。使用 Clarity 3D Solver 生成的模型與實驗室的測量結果會更為接近,並且可以直接導入到行業標準電路模擬器(例如 Cadence Sigrity SystemSI)中,以實現實際測量和模擬之間極高的相關性。

此等特性對於 PCIe 的合規性和互通性測試尤具價值,例如在 PCI-SIG 合規性研討會期間作為 PCI-SIG 合規性項目的一部分而進行的電氣測試。該研討會將同時進行互通性測試和合規性測試,其結果要麼為「通過」,要麼為「不通過」。產品在互通性測試中的通過評級分數必須至少為 80%,而合規性測試則為 100%。如果在合規性研討會期間,產品未通過測試,則意味著產品可能無法貼上 PCIe 合規的標籤,這可能會導致產品失去在競爭激烈的市場中脫穎而出的機會,並且需要進行重新設計,以在下一次 PCI-SIG 研討會上重新進行測試。

使用 Clarity 3D Solver 的設計人員在電氣測試(包括平臺和內插卡發射器和接收器特性測試)中將獲得關鍵性優勢,Clarity 提供的黃金標準精度互連模型模擬,增強了設計人員首次測試即可通過的信心。

此外,Clarity 是 Cadence 特有的同類之中最佳設計和分析流程中的一部分。這一流程包括一套完整的設計環境:包含 Allegro 平臺的高速設計規則、Aurora 工具的設計同步信號完整性和電源完整性分析、Clarity 工具的精確 3D 模型提取,以及作為最後一步的 SystemSI 工具的 PCIe 合規性模擬分析。這套包含了 Clarity 3D Solver 的完善且高度整合的解決方案體系構成了 Cadence PCIe 的整體設計流程,説明設計人員確保 PCI 產品按時、按預算投入量產。

推薦閱讀 白皮書下載 | 解決 112G 連接的訊號完整性難題

附件表格

參考資料

1. https://pcisig.com/

2. PCI-SIG PCI 4.0 and PCI 5.0 Specifications

3. https://pcisig.com/faq?field_category_value%5B%5D=pci_express_4.0&keys=

4. https://pcisig.com/pci-express%C2%AE-retimers-vs-redrivers-eye-popping-difference

5. PCI Express Retimers vs. Redrivers: An Eye-Popping Difference

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」