5G 是行動通訊發展的下一個重要里程碑,目標是到 2020 年實現更大的流量 (10,000 倍) 、更高的容量 (1,000 倍) 、更低的延遲 (<1 毫秒) 和更低的能耗 (降低 10%) 。而創新的高頻電子元件為下一代通訊系統以及未來無線連接生態系統奠定基礎。為實現隨時隨地高速傳輸資料,系統架構日益複雜,對零件級設計帶來巨大挑戰。

Cadence® AWR® Design Environment 提供完善的系統、電路與電磁協同模擬能力,結合 NI 的簡化測試解決方案,協助 RF 與微波工程師有效應對新一代射頻設計需求。

本白皮書為 PDF 版本,共 14 頁,將深入探討如何使用 AWR Design Environment 平台 (包括 AWR Microwave Office、AWR VSS 和 AWR AXIEM 軟體) 進行電路、系統與電磁協同模擬,並結合 NI PXI、VST 和 LabVIEW 的測量平台,有效優化寬頻 ET 功率放大器於不同頻段和應用情境下的設計效能,顯著加快産品開發速度。

本書重點

5G/LTE 包絡跟踪功率放大器的産品設計流程 |

|

LTE 功率放大器設計挑戰 |

|

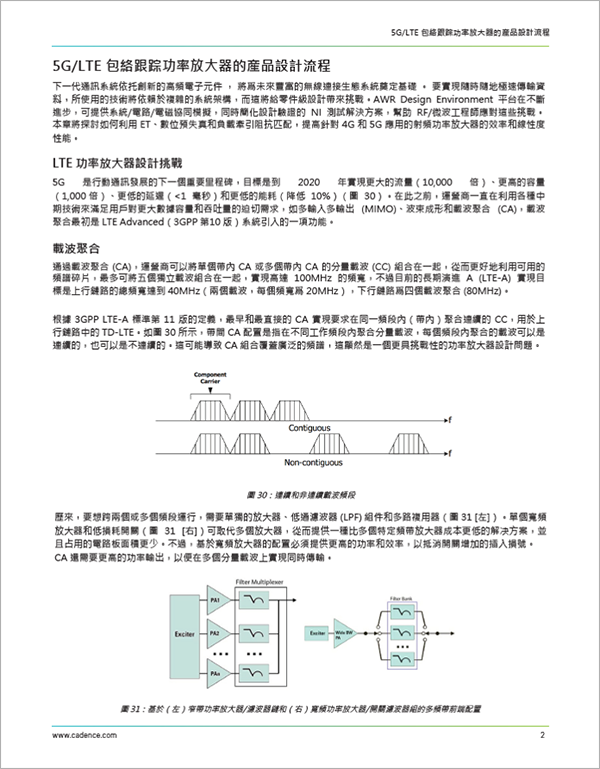

載波聚合 |

|

OFDMA、SC-FDMA、PAPR 和效率 |

|

負載牽引和匹配網路設計 |

|

透過系統模擬確定功率放大器的要求 |

|

使用 ET 和 DPD 提高效率和線性度 |

|

實際案例:使用 DPD 的 ET 功率放大器 |

|

用於 ETPA 開發的測試解決方案 |

|

使用 PXI、VST 和 AWR Design Environment 的 ET 結果 |

中文版授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」