By John Burkhert Jr

在之前「 第一批看完本文的 Layout 工程師都贏在起跑點 」這篇文章中,John 和大家討論了 layout 設計時的一些技巧策略。隨著專案向前推動,我們來到了生產階段,發現了在 REV1 貼片時隱藏著的預生產問題。這些問題要如何解決呢?有沒有辦法可以提前避免這些問題的產生呢?且看我們的 John 如何解答 ~

圖片來源:The1Thing.com

我們已經完成了設計的第二版修訂,但是仍有很多改進意見被不斷提出:

採購組 |

|

希望我們可以減少層數並縮小最小間距, 他們不明白為什麼總有那麼多電容。 |

|

故障分析組 |

|

擔心熱傳導路徑和 ESD 抑制。 |

|

生產單位 |

|

「用一個矩形來定位條碼和分佈在周圍的更多板級基準標記怎麼樣?另外,你能不能把這些都設計的分散些,特別是那些較高的器件?」嚴格來講,將元件均勻地分佈在電路板上是有價值的。 |

|

返工技術人員 |

|

對微控制器周圍的設計要求又有不同,一些小零件妨礙了返工噴槍的工作。 |

|

檢查組 |

|

會更加關注電路板上的極性標記。 |

|

測試團隊 |

|

希望增強電性測試覆蓋率以及 JTAG 連接器或 I2C 匯流排以獲得更完整的圖像。 |

以上這些還不包括電子和機構工程師的意見,我們都知道他們在改進建議方面有多麼執著。整個下游用戶群都已經表明了態度:他們代表最終使用者(即「客戶」),希望每個小配件都能正常工作並能夠在出現問題時被成功修復。

前車之鑒

我曾經在一個接收檢驗實驗室工作,我們的部門製造了用於海上石油鑽井平臺的一對多點無線電裝置。我的工作則是檢查隨機抽取的每一批電路板上隨機抽樣過孔的電鍍銅管壁。由於專注於在通孔管上上下搜索針孔空洞,視線經常會受到顯微鏡的干擾。也因此,我發現了 ECAD 的重要性。

焊接

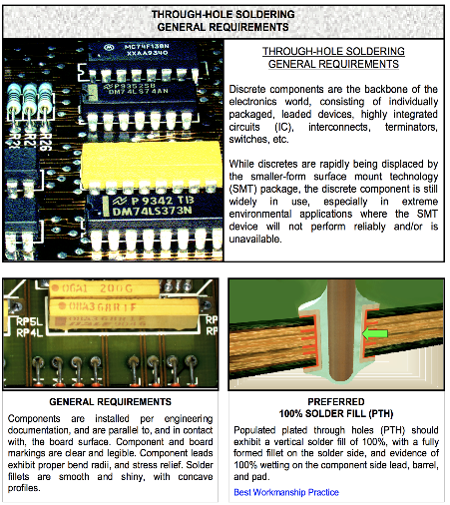

我們應該知道所有典型的焊接缺陷是什麼樣的,也應該能夠根據視覺或破壞性測試確定其可能的根本原因。裝配線上最常見的問題之一是在表面黏著 QFN、QFP(或類似的矩形)封裝下焊接大的接地塊。這需要焊接爐溫度曲線和焊錫膏數量/沉積的完美結合。相對於周邊較小的焊盤而更需要精確的數量。

資料手冊有時會對焊錫膏做出指導。如果我可以選擇元件,那麼所有資料手冊都會有實際測試資料的支援。於我而言,購買零件的第一條規則就是要有良好的封裝文檔。

一個例子:「e-pad」上的焊料空隙在 X 射線上顯示為圓潤焊點 (良好粘合區域)中的氣泡。在焊錫膏範本中創建類似於具有四個或更多開口的窗框圖案——相對于全尺寸開口的情況——可以減少焊錫膏的量。

另一個常見缺陷是焊料橋接,其解決方案會涉及防焊油墨、焊膏和/或金屬加工。焊球是另一缺陷,代表我們使用的焊料過多,或者在迴風爐中溫升太高。現在我們可以得出焊料空洞的根本原因:並不是由於焊料不足所致,諸如冷焊或干擾焊點之類的缺陷更可能與技術相關。

圖片來源:NASA

以上這些資訊都可在如 IPC J-STD-001 的技術手冊中找到。其目的並不是為了修復元件和 PCB 級別的問題,而是始終返回到基層並將更新放在將使用同一設備的任何未來產品上。封裝更新通常意味著設備檔案名的重命名或升級,以說明 PCB 的特定反覆運算是否具有改進的歷史。在某些行業中,這種詳細的可追溯性是必不可少的。

通孔元件

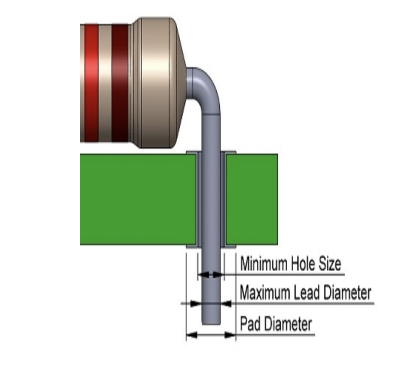

這些符號的佈局(或錯位)同樣可以引起不小的生產問題。通孔佈局的要點是為每個引線獲得正確的孔尺寸。

圖片:PCB-3D

孔尺寸是至關重要的,因為我們希望其空間足夠大以便於自動佈局,同時足夠小以在引腳上獲得良好的毛細管作用而將焊料芯吸到孔中。孔的標準尺寸通常超出引腳的最大尺寸約 10mil,但這是一個比例方程,有不同的方法來解決。ANSI 有一個適用于機械孔的標準,而IPC也有多種方法可以確定最佳數量。實際上,鑽頭的尺寸只有幾多種,我們不需要糾結在幾微米上。

表面黏著

無論採用何種技術,表面黏著焊盤都至少有三個元素:金屬、防焊油墨和焊錫膏範本。金屬和焊膏層是正片層:繪製的項目可見於圖稿中。防焊油墨被認為是負片層,因為在圖形上顯示的是從 PCB 剝離的區域。

基本上,我們在做的是設計阻焊層開口之間的空間。不亞於金屬焊盤層,焊盤之間的這些小油墨壁也能左右組裝過程的結果。當足夠牢固可以防止焊點熔合在一起時,我們稱其為錫堤;當太薄而不能粘附在 PCB 上時,我們稱其為裂片。最小堤寬的閾值是 4mil。能夠檢查這些阻焊裂片的 CAD 系統會成為我們的得力工具。

我們在放置元件時要注意使其遠離 PCB 邊緣,因為電路板的邊緣會在中心區域之前達到回流溫度。除了元件立起,當引線以不同的速率從焊膏變為液體再到固體時,一些元件會被物理拉開。這在現實生活中發生在放置 RF 輸入的繞線電感上。儘管在電子方面這是一個好方法,但在實踐中會成為一個潛在的缺陷。不時出現的故障是最難解決的問題。

想必我們都想最大限度地降低由於 DFX 難題而引起的專案進度影響,如果我們在初始設計和修訂時就注意了以上三個方面的問題,不僅我們的設計品質會有所提升,PCB 原型設計轉到生產階段的過程也會更為平順,我們的信心和聲譽也會隨之提高~快行動起來吧!

文章授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」