如果不是射頻設計界的一員,那麼所有模擬振盪器 (oscillator) 的使用看起來可能都很深奧。然而隨著新產品的設計頻率越來越高,更多積體電路和電路板設計人員都應該熟知 RF 振盪器元件和電路。

一旦達到千兆赫 (GHz) 以上的頻率範圍,相比離散元件,系統級晶片 (SoCs) 和積體電路 (ICs) 便成為了 RF 振盪器的更佳選擇。對於涉及 GHz 頻率範圍的設計人員,本文將討論一些所有設計人員都應該了解的基本振盪器及重要的 layout 技巧。

科普小知識振盪器 是用來產生具有周期性的類比訊號(常是正弦波或方波)的電子電路。

射頻振盪器 (RF Oscillator) 的設計

許多標準振盪器電路都可以採用現成的元件來設計。這些電路通常包括一個或多個 FET 場效應管 (BJT 雙極型電晶體、JFET 結型場效應管或 MESFET 金屬半導體場效應管)、多個無源元件、一個或多個運算放大器和 / 或一個變容二極體。要使上述任何一個電路達到 GHz 頻率,都需要使用 GaAs (頻寬小於 10 GHz) 或 GaN (頻寬大於 10 GHz) 有源元件。

由於多種原因,很難讓這些由離散元件構成的振盪器在 GHz 高頻率下工作。所涉及的問題是由共振頻率足夠高的微小電感器和電容器的可用性,以及實際電路佈局中的寄生效應所引起。所涉及的成本也將比簡單地使用 RF 振盪器積體電路或晶體振盪器要高。儘管存在這些困難,我們也可以使用離散元件來構建一個可以在數百或數千兆赫的頻率下與商業現貨元件一起運行的 RF 振盪器。

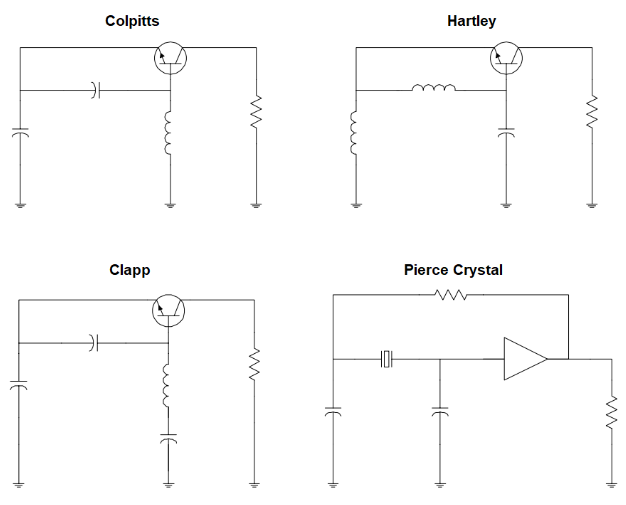

圖 1:四個基本振盪器電路

如果在設計一個必須在高功率下工作的自訂信號鏈時,沒有可用的 RF 振盪器積體電路,則可以使用離散元件構建上述任何振盪器電路或壓控振盪器 / 壓控晶體振盪器/數控振盪器 (VCO / VCXO / NCO) 電路。用離散元件製造上述任何振盪器都需要自共振頻率足夠高的無源器件。

特定電路可能輸出方波、三角波 / 鋸齒波或指數波 (弛緩振盪器, relaxation oscillator)。 將輸出轉換為正弦波的最簡單的方式是使用積分器、微分器、高階 RC 濾波器或限幅電路。例如,壓控振盪器 (VCOs) 大都是產生三角波,可以用史密特觸發電路 (Schmitt trigger circuit) 將其轉換成方波。使方波透過截止頻率接近基波的三階 (或更高階) RC 濾波器後,便可以將方波輸出轉換成近似正弦波,然而這對於 GHz 頻率下的離散 COTS 元件相當困難。更精確的信號轉換方法則需要運算放大器和 LC 儲能電路,這些不在本文討論範圍之內。

將 RF 振盪器引入信號鏈

微波器件公司已經花了大量時間開發和完善 RF 振盪器電路的積體電路。這些元件的相位雜訊往往相當低,並且通常都是表面黏著元件,尤其是在設計用途為高頻工作時。這些元件可以選用上述任一電路,也可以使用內部整數型 / 分數型鎖相迴路 (PLL) 將頻率合成至高頻。可供選擇的電路頻率範圍是幾 MHz 到數十 GHz。

這些 RF 振盪器積體電路也可以使用一個數控振盪器 (NCO) 或壓控振盪器 (VCO) 分別生成一個 MHz 或 GHz 信號。這些積體電路還可以用作 PLL 回饋迴路中的基底振盪器,用於合成更大頻率。採用這種實現方式時須注意,因為該系統中使用的任何 RF 振盪器的頻寬都較為有限。此外,迴路濾波器 (基本都是低通濾波器) 和相位檢測器限制了擷取和鎖定範圍,使兩個範圍都較小。應選用頻寬足夠大的振盪器,使其能夠與擷取 / 鎖定範圍重疊。

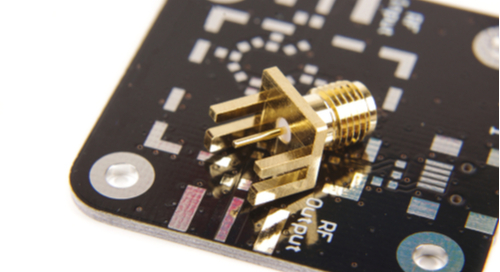

RF 振盪器積體電路、任何由離散元件構成的 RF 振盪器以及信號鏈中的所有其他元件都應使用表面黏著元件,因為當通孔類過孔與通孔元件一起使用時,可能會出現某些信號完整性問題。在次 WiFi 頻率下,只要反鑽所有過孔和殘留元件短截線,通孔元件就不會有信號問題。然而,這增加了製造和組裝成本,因為需要多個步驟來移除過孔和元件引線上的短截線。因此,最好在較高的射頻頻率下使用表面黏著元件。

圖 2:與任何 RF 振盪器一起使用時,連接器 (如:邊緣安裝的形狀記憶合金 (SMA) 連接器) 等需要精確的阻抗匹配。

毫米波 (mmWAVE) 振盪器佈線要點

如果將 mmWAVE 頻率的 RF 振盪器用作穩定的基準振盪器,則應儘量避免使用任何過孔,尤其是通孔類過孔。毫米波電路板中的通孔類過孔問題與插入損耗和共振有關。首先,這些結構往往相當大,因此它們的幾何共振頻率往往與RF振盪器的輸出頻率相似。過孔中的任何共振信號都將成為 EMI 電磁干擾和容性過孔間耦合的來源。

其次,將這些過孔的阻抗與互連匹配,以防止反射並確保低插入損耗很難。對於高度穩定的 RF 基準振盪器,確保信號完整性和防止失真至關重要,而且,需要適當調整過孔尺寸以防止插入損耗。對於調頻或用於調變另一個信號的 RF 振盪器,過孔構建需要精確,以具有足夠寬的平緩頻寬。例如,如果過孔阻抗頻譜沒有正確建模,則對於高密度互連 (HDI) 電路板中的 RF 振盪器,可能很難確保 5G 調變方案 (如濾波器組多載波 (FBMC)、通用濾波多載波 (UFMC)、廣義分頻多工 (GFDM) 以及濾波正交分頻多工 (f-OFDM) )中的信號完整性。

無論是從零開始設計 RF 振盪器,還是需要將現有元件加入 PCB 中,只要使用正確的 PCB 設計和分析軟體,便可以設計、佈局這些電路和 PCB 並模擬其行為。Allegro® PCB Designer 中的分析工具和 Cadence 的全套分析工具非常適合運行 RF 振盪器電路的預佈局分析;Cadence 的佈局後分析工具如 Sigrity、 Aurora 也非常適合檢查複雜佈局中可能出現的信號完整性問題。

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」