本文要點

即使進行了完美的阻抗匹配,所有傳輸線也都會存在某些訊號完整性問題。 |

|

由於損耗、色散和寄生元件而經常出現的一個問題是符號間干擾。 |

|

這種訊號完整性問題會導致位元流中的錯誤,但謹慎的通道設計和驅動器 / 接收器選擇可以有效減少錯誤。 |

可能影響PCB訊號完整性的問題清單很長,但在高速通道中特別應該診斷的一種問題是:符號間干擾 (Intersymbol Interference, ISI)。這種特定的訊號完整性問題涉及位元流中訊號之間的干擾,就像其名稱所示。那麼,是什麼導致了這種訊號完整性問題?如何減少符號間干擾?

這個問題通常在電信環境中討論,但是在 PCB 中也會出現類似的效應。雖然我們永遠無法完全從 PCB 中消除訊號完整性問題 (包括符號間干擾),但可能可以將符號間干擾減少到在典型測量中不會被注意到的程度。本文將討論如何在高速通道中減少符號間干擾。

什麼導致符號間干擾?

符號間干擾是與數位位元流或用於訊號標準 (如 PAM-4) 的脈衝流有關的問題。所有有限頻寬通道都將顯示符號間干擾,而每個電氣通道都是到某個高頻率的有限頻寬。

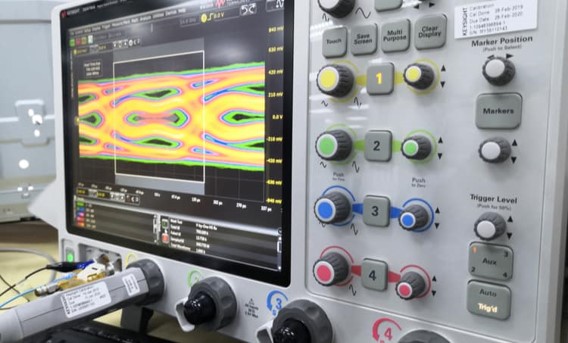

此訊號分析儀測量結果顯示了極端的符號間干擾

當數位訊號流被接收器讀取時,其中一個訊號會干擾後續的訊號,這種現象被稱為符號間干擾。在電信系統中,特別是在無線系統中,符號間干擾通常是由於訊號的副本以不同的時間到達接收器所造成的多徑效應引起的。就算是對於具有互連和數位位元流的鬆散佈線PCB而言,也可能存在符號間干擾問題。

在數位通道中,位元串流可能會出現一些問題,導致符號間干擾,包括:

輕微阻抗不匹配引起的反射 |

|

相位失真引起的拉伸脈衝 (由基板中的色散引起) |

|

接收器輸入處看到的慢脈衝回應 (由負載電容引起) |

|

極端的抖動,平均抖動時間與訊號的 UI 相當 (這種情況很少見) |

符號間干擾可能聽起來有點玄乎,但在時域波形中很容易被發現。儘管它是由頻域問題 (有限頻寬) 引起的,但在時域中可以很容易地看到它。

診斷符號間干擾

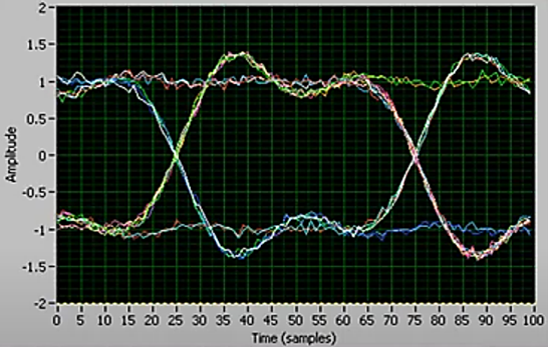

符號間干擾可以在眼圖中看到,如下圖所示。只要在 PCB 上放置測試夾具,大多數高頻寬示波器或數位訊號分析儀都可以用來收集此測量資料。

眼圖顯示符號間干擾

一個完美的眼圖會有完全重迭的訊號,沒有任何抖動 (水準上升時間變化) 或雜訊 (訊號電平變化) 。在上面的圖像中,當我們看到波浪狀的訊號行為重迭在高電平和低電平之間時,就會出現符號間干擾。抖動表現為訊號上升時間的水準變化。

在 PCB 板層級上如何減少符號間干擾

在上述清單中的四個要點中,只有前三個非常常見。關於第四點有關抖動的問題,由於功率穩定性的微小變化,總會存在一些抖動。然而,類似 UI 一樣巨大的抖動並不常見,除了很可能是高 PDN 阻抗之外的多個問題也導致了非常大的抖動。

如果要減少符號間干擾,需要著重於三個方面:阻抗不匹配、色散 和 緩慢的脈衝回應。以下表格概述了一些方法:

| 問題區域 | 電路板因素 | 解決方案 |

|---|---|---|

阻抗不匹配 |

• 色散 • 負載電容 • 其他改變走線阻抗的寄生效應 |

理解高速通道都是有頻帶限制的: |

延伸脈衝 |

• PCB 基板色散 • 由於互連的幾何形狀造成的幾何色散 |

• 根據 Heaviside 準則進行設計 (通常只適用於 RF) • 使用具有比較平坦的 Dk 與頻率曲線的基板 • 將延遲時間編入位元流 |

脈衝回應緩慢 |

• 負載電容 • 其他寄生電容 |

• 使用負載電容較小的零件 • 增加其他分流組件 (例如覆銅) 的間距 • 將延遲時間編入位元流 |

選擇更少色散的 PCB 層壓板和具有更小負載電容的元件等解決方案只能解決部分問題。對於高資料速率通道,最好的解決方案是確保極其精確的阻抗匹配並添加延遲時間。程式設計延遲到位元流中的解決方案將降低總資料速率,但也會降低誤碼率。對於阻抗不匹配,只需記住:我們只需要關注一定範圍內匹配阻抗 (通常是幾個 GHz) 即可。

還有兩種方式可以強制接收器完全忽略由符號間干擾引起的訊號電平的干擾UI變化,即遵循 Nyquist ISI 標準並使用均衡技術。

Nyquist ISI 標準

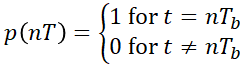

有一種特定的取樣率可以在接收器元件中使用,以便恢復的訊號完全不受符號間干擾的影響。當接收器讀出具有以下特性的數位脈衝流時,就可以滿足 Nyquist ISI 準則:

Nyquist ISI 標準

在這裡,Tb 是資料流程的位元率。這個方程式表明,當接收機恰好以位元速率進行採樣時,只要比特波形在任何其他採樣時間都為 0,它始終會準確鎖定到所發送位元的真實值。透過精確地塑造所傳輸的波形,可以實現這種性質,需要使用脈衝整形濾波器。

均衡

採用均衡化方案,如分佈回饋均衡化,旨在透過估算演算法恢復訊號品質。這將理想地消除可能疊加在接收訊號上的符號間干擾或其他雜訊。但是,均衡化不是只需「添加」到元件中即可。它是使用特定電路實現的,該電路內置於元件中。新一代 DDR 和 PCIe 正是在接收端使用均衡化,我們可以期待在未來其他信令標準的下一代中更加標準化。

高速互連設計可能會很困難,需要平衡許多目標,尤其是學習如何減少符號間干擾。Cadence 的 PCB 設計和分析軟體可以説明我們使用業界最佳的 CAD 工具和強大的訊號完整性分析工具設計和佈局互連,實現自動化系統分析中的許多重要任務。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」