快速檢查先行除錯

電路板佈線設計工具都有 Design Rule Check(DRC) 的幾何檢查功能,以確認所繪製的設計檔案不會有兩點問題: 1. 安全間距不足 2. 應接而未接。讓板子不會因為間距不符設計規範或因未確實連接而無法正常運作。

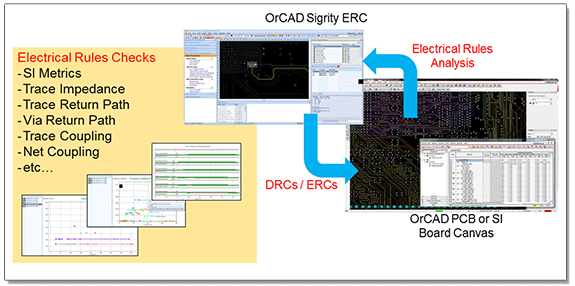

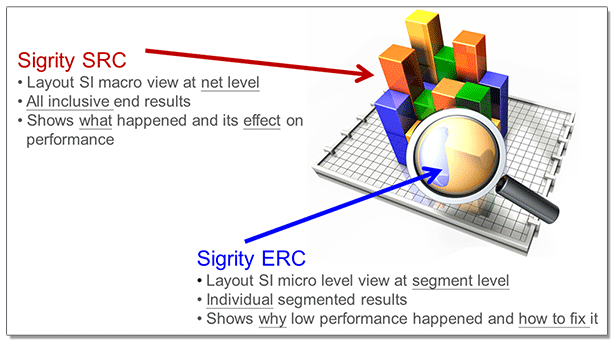

隨著高速訊號設計的普及和額定工作電壓的降低,訊號完整性的分析更顯重要,但 SI 分析往往需要較詳細的設定和人員的經驗才能夠順利且有效的執行。Sigrity ERC / SRC 是以電性規則進行 ERC 檢查和以批次模式進行 SRC 檢查,讓 PCB 設計人員在 Tape Out 前,能夠自行以方便的界面和流程找到問題點或嚴重程度,以便先行排除潛在問題,而不用等到完整的 SI 分析報告才進行修改。

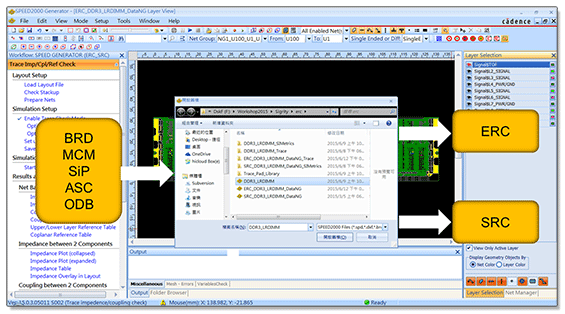

ERC / SRC 可以直接載入 Cadence 系列如的 Allegro 的 BRD、APD 的 MCM、SiP 的 SiP、PADS 的 ASC 以及其他 CAD 的 ODB 檔。

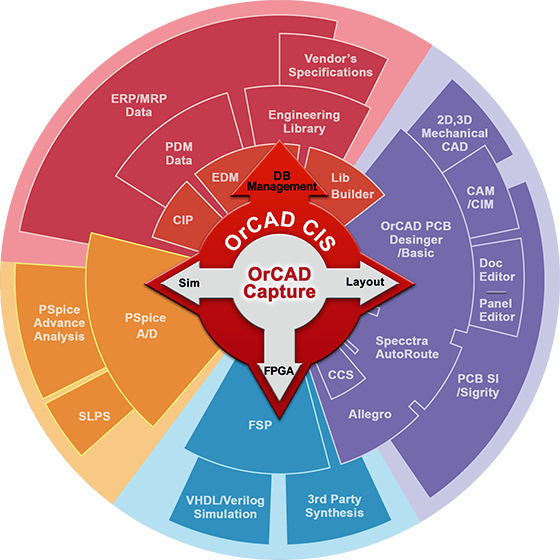

OrCAD 產品關係圖

Sigrity ERC

ERC 會將載入的幾何結構做電性規則檢查 Electrical Rule Check,結果以 HTML 報表來列出訊號如:

阻抗 Impedance:貫孔數量、最大阻抗值、最大阻抗長度比、最小阻抗值、最小阻抗長度比…。 | |

干擾 Couple:最大干擾源訊號名、最大干擾比、最大干擾長度…。 | |

對應參考電源 / 地 Ref:在同層 (co-planar) 與上下層之參考舖面的對應關係。 |

若有設定 NETGROUP 的訊號群組與相關零件的關係,則可以圖形方式列出以下報告:

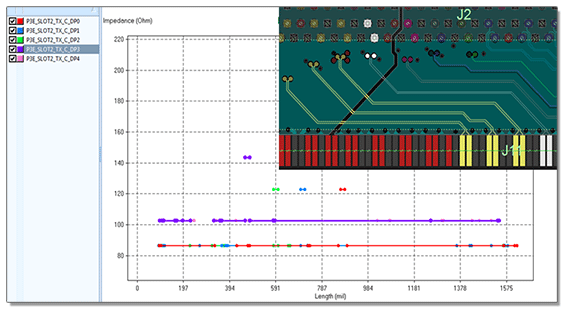

1. Impedance plot (collapsed)

將所設訊號各段的阻抗值以圖表方式顯示,可看到訊號的阻抗值與不連續狀況,若直接點選阻抗值線段更能直接對應佈線上的相對位置,找到問題線段之所在。

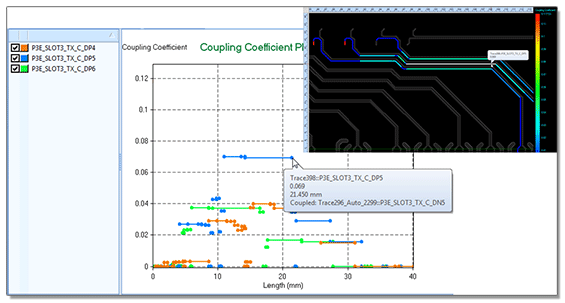

2. Coupling Plot (collapsed)

將所設訊號各段的干擾值以圖表方式顯示,游標停在其上時會顯示被干擾訊號名、干擾程度、干擾長度及干擾源訊號名。同樣地,若直接點選干擾值線段便能直接對應佈線上的相對位置,找到問題線段之所在。

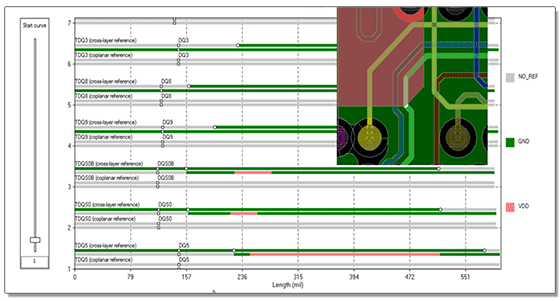

3. Reference Plot (expanded)

將所設訊號與參考電源 / 地各舖面的對應關係以圖表方式顯示,可察看電源地在同層 (co-planar) 或其上下層之參考電源層的對應關係。同樣地,若直接點選該圖表線段也能直接對應佈線上的相對應位置。

Sigrity SRC

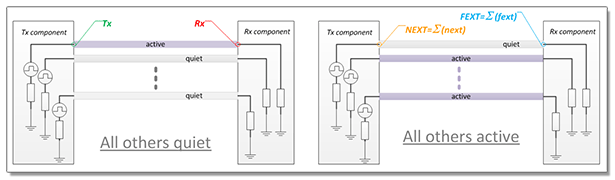

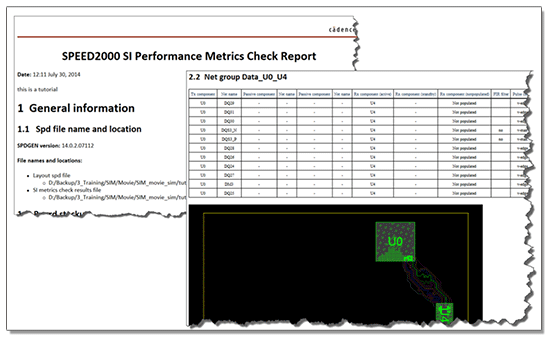

SRC 會將載入的幾何結構做訊號批次檢查 SI metrics Check,並列出訊號的被影響程度如:

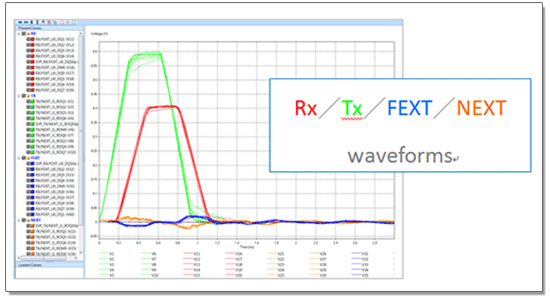

Tx / Rx 相關:發射端和接收端的訊號品質。 | |

NEXT / FEXT 相關:近端和遠端被其他訊號干擾的程度。 |

其結果以 HTML 報表來列出訊號 Tx / Rx / NEXT / FEXT 的影響程度,或是以 Excel 列出前十大干擾源之訊號名稱。

Layout 人員的 SI 品質分析

只要簡單設定流程,ERC / SRC 就像是定性或定量分析般,讓 Layout 人員利用 ERC 可以很快地找到問題線段所在位置,而 SRC 則可以得知問題的嚴重程度決定要先修改哪個訊號。

Sigrity ERC / SRC 並不是要取代 SI 分析,而是要填補 DRC 到 SI 分析之間的斷層。讓 Layout 人員先做 SI 的 Quality Check減少被 SI 人員退回重改 Rework 的次數,並希望減少 SI 人員為了確保最後的 SI 品質而配合多次的訊號分析,讓相互間的經驗能夠傳承,計畫的整體時程能夠縮短。