輕鬆降低產品設計成本

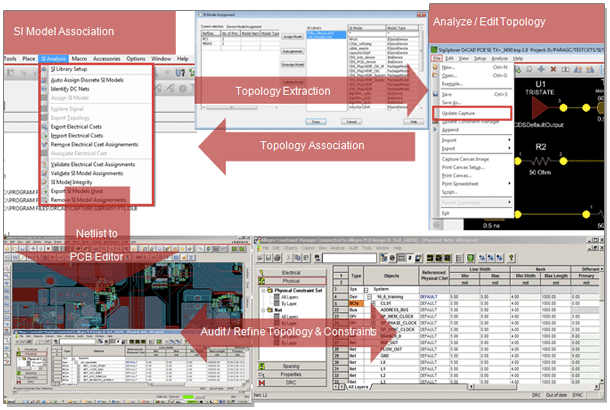

透過 OrCAD PCB SI 模擬及分析,並將這些條件予以設定並存成電氣規範檔案有助減少潛在的 SI 問題,讓您減少修改的機會並降低設計產品的成本。OrCAD PCB SI 支援 Capture 與 SigXplorer 可直接雙向連動作業。RD 或 SI 工程師要進行 Constraint 規範評估與設定時不需要再去麻煩 PCB Layout 工程師重工設定 Rule。也可以解決 Xnet 及 Rule 設錯的問題。

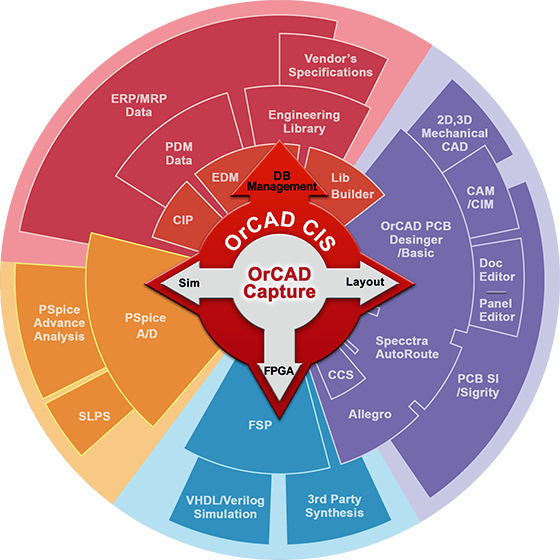

OrCAD 產品關係圖

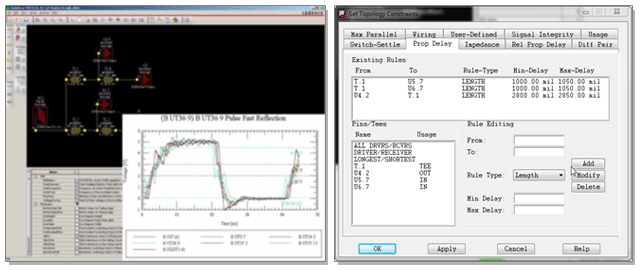

透過 OrCAD PCB SI 參數調變 (Solution Space) 分析功能在一次的模擬作業中就可得到數種不同參數條件下的模擬結果。並得到您所需要較為理想的設計參數後,可以透過 SI 的 Constraint 設計環境,將這些條件予以設定並存成電氣規範檔案,透過這樣的功能設計,您可以能夠整合各種不同的可能性考量,有助減少潛在的 SI 問題,讓您減少修改的機會並降低設計產品的成本。

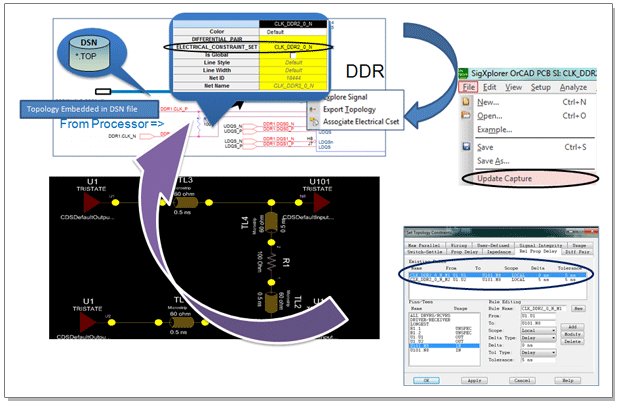

若需作 Pre-Simulation,OrCAD PCB SI 支援 Capture 與 SigXplorer 可直接雙向連動作業。RD 或 SI 工程師要進行Constraint 規範評估與設定時不需要再去麻煩 PCB Layout 工程師,我們可由線路圖直接產生電路拓樸結構並帶入到 SigXplorer 環境中進行訊號完整性的分析。

工程師在分析完畢後可在 SigXplorer 裡面設定 Constraint 後再回編到 Capture。當 PCB Layout 工程師在 netin 完成後,這些 Constraint 設定也隨著 netlist 的導入而自動帶到 Allegro / OrCAD PCB Layout 的 Constraint Manager 環境中。

且爾後當該份電路圖被再次利用時,工程師無須再去重複先前的作業,所有的拓樸結構、T 點、Xnet 及 Constraint 資料都已經存在電路圖上。