高效率的專業模擬中控平台

Virtuoso® Analog Design Environment(ADE) 是建構在 Virtuoso 設計平台中最佳的類比與混合訊號設計模擬解決方案,廣泛應用在 full-custom、analog、RF IC 設計領域,採用目前業界的模擬與分析標準,在使用上,ADE 提供圖形介面、整合波形分析與觀測、統計分析模擬結果,以目標導向指定參數範圍做模擬分析,並且支援多種模擬器演算(包含其他非 Cadence 模擬器) 。ADE 在 Virtuoso 環境中使用,無須擔心資料轉換的問題,更可針對電路中設定的參數依規格範圍掃描快速模擬測試,提昇您的工作效率。

特點

容易學習,快速上手 |

|

可圖形介面管理,更有系統 |

|

模擬狀態儲存,提高工作效率 |

|

整合各種模擬器,更具彈性 |

|

(Virtuoso Spectre Simulation / Virtuoso APS / Virtuoso AMS Designer / Virtuoso UltraSim / Virtuoso XPS) |

|

提高模擬廣度與除錯精準度,模擬更專業 |

|

視覺化圖像選單,加快電路除錯 |

|

強大的寄生模擬分析能力,提高成功率 |

|

PDK 應用,加速設計流程 |

流 程 特 點

PDK 應用大幅加快設計流程而提高工作效率

整合 Virtuoso Multi-Mode Simulation 實現類比、射頻、混合訊號模擬驗證

強大的寄生模擬分析能力,大幅提高第一次就設計成功的機率 ( first-pass success )

清楚而簡單的操控介面,協助使用者快速的找到電路問題

EASY-TO-USE INTERACTIVE SIMULATION ENVIRONMENT

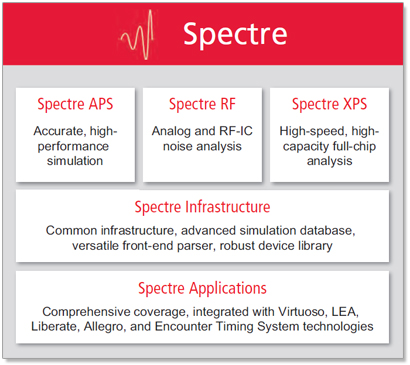

ADE 提供完整功能讓所有電路設計者快速完成模擬設定、環境建構與分析模擬結果,環境中整合了 Virtuoso Spectre Simulation、Virtuoso APS、Virtuoso AMS Designer、Virtuoso UltraSim、Virtuoso XPS。

使用者在設計流程中可快速且輕易地透過視覺化的圖形介面了解類比或混合訊號中特定參數對電路產生的效應,內建的 OCEAN 程式語言更加速 bash 演算,而透過 OASIS (Open Artwork System Interchange Standard) 整合套件,ADE 可輕鬆的與自家 Virtuoso 或業界使用的其他模擬器整合使用,加速電路設計。

BUILT-IN WAVEFORM DISPLAY AND SIGNAL ANALYSIS CAPABILITIES

新一代波型顯示器 (ViVA),包含波形計算功能,針對各種設計結果資料如電壓、電流、模擬參數、工作點做代數方程式運算,並提供更完善的 post-simulation 分析環境,在類比與混合訊號分析上支援更進階的波形分析模式,如 noise、corner、statistical、RF plots…等,支援 PNG、BMP、JPG、PPM、TIF、PDF、SVG 檔案格式。

INTERACTIVE SIMULATION

讓使用者可以快速改變參數值,減少電路設計者模擬流程所花的時間。

VIRTUOSO AMS DESIGNER SIMULATOR

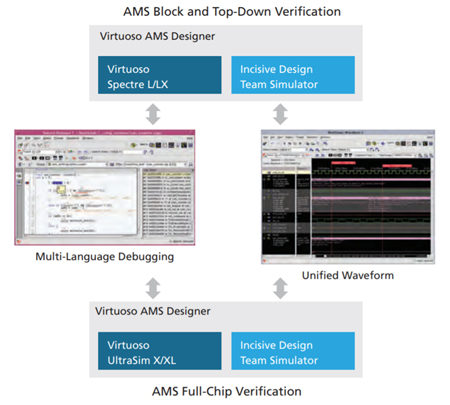

Cadence Virtuoso AMS Designer 整合 Cadence Virtuoso 類比模擬器與 Incisive 數位功能驗證於同一模擬與驗證平台中,使得類比、無線射頻、記憶體及晶片系統等…混合信號設計在此全客製化的環境實現。

Cadence Virtuoso AMS Designer 支援 Verilog-AMS 及 VHDL-AMS 混合訊號語言,當類比與數位連接時使用者可選取不同的類比模擬器於不同的設計模擬階段,例:block-level 的類比與無線射頻設計 (RF design) 時考量精確度可使用 Spectre Simulation,或欲同時考量到模擬速度效能則可選擇 APS (Accelerated Parallel Simulator),而當考量 Full-Chip 功能驗證時可挑選 UltraSim 並搭配數位 Incisive 彈性與便利執行此模擬、驗證的設計流程。

特點

提供 Virtuoso 類比及 Incisive 數位模擬 |

|

支援 Virtuoso ADE (Analog Design Environment) 中類比設計流程所使用的模擬參數模型,亦可使用於數位 Incisive 驗證環境中 |

|

支援由上而下 (Top-down) 的設計方法,使在初步設計階段的錯誤能夠提早被察覺,以確保設計可準時進入投片流程 |

|

支援混合信號的硬體描述語言 (Verilog-AMS 及 VHDL-AMS) 使模擬更加快速 |

|

結合 RF 封包分析與數位基頻 (digital baseband) 模擬,加快 AMS 對 RF 電路模擬速度,尤其是針對 SPICE 級的精確度模擬速度更明顯提升 |

|

提供可選式的類比模擬器,讓使用者滿足模擬速度與效能考量 |

|

支援圖形化使用者介面 (GUI) & 可透過 batch mode 下指令 (command) 來增加模擬的便利性 |

|

支援以數位區塊為主的混合信號驗證 & 導入低功率混合信號驗證解決方案 |

Virtuoso AMS Designer 驗證流程,可滿足電路設計在混合訊號驗證分析上整個流程的需要

支援多種硬體語言及「MEET-IN-THE-MIDDLE」的設計方式

Cadence Virtuoso AMS Designer 支援來自不同來源的晶片系統設計 IP 格式,包含 Verilog-AMS、VHDL-AMS、Verilog-A、Verilog、VHDL及SystemC 硬體語言。當於 Virtuoso Schematic Editor 使用 HDE 架構設計複雜的混合訊號專案 (包含上述硬體語言及 spice、Spectre Simulation) 時,AMS Designer 會自動插入介面元件 (IE / interface elements) 做類比與數位間的訊號轉換,並且它可將 bottom-up 的精確性與 top-down 的快速性作設計流程整合 (MEET-IN-THE-MIDDLE),它實現了速度需求和晶片精確性之間的最佳平衡性,而且以最佳的考量來執行模擬。

兼顧類比與數位模擬需求的混合訊號模擬器

整合式的模擬引擎,不僅提高混合性訊號晶片模擬之完整性,更讓使用者在模擬的準確性及效率間不再左右為難。因為依使用者的需求來選擇模擬器,所以使用者可在模擬、驗證設計流程中更具彈性且能滿足模擬速度與效能考量,讓使用者的創意永遠 Time To Market。

它的演算技術是建構在 Virtuoso Spectre Simulation、UltraSim 與 APS 這些類比模擬器,並且能相容與 INCISIVE 數位模擬器所構成的整合混合性訊號模擬器。

類比訊號為主或數位訊號為主的流程

針對混合訊號電路設計,Virtuoso AMS Designer 使用 ADE 的 netlisting 方式將電路符號方塊、行為模型方塊…等不同型式方塊獨立處理,而 Virtuoso AMS Designer 數位驗證使用 Incisive,Incisive 環境提供測試分析、Specman 及驗證平台。

針對數位設計為主的電路,AMS Designer 會以本身的 Incisive 環境來完成數位驗證工作,此時類比與數位間訊號傳遞轉換可使用一訊號控制檔 (single control file) 做為定義,類比方塊則被整合到數位的 SoC 中,如此類比與 RTL 設計方塊間可便利的調整其模擬精確度與速度以取得可接受平衡點。而互動式的模擬介面將開啟 SimVision 並提供從電路圖 cross probe 的功能。

針對類比設計為主的電路,執行 AMS 電路模擬前 netlist 必須先經過編譯(compile)與合成(elaboration)動作,若使用 ADE 中「Netlist and Run」單鍵功能,便會自動依照以下順序完成 AMS 模擬程序:

線路圖轉換為 Verilog-AMS Netlist |

|

編譯 Netlists |

|

執行合成 |

|

執行模擬 |

以上每個工具產生各自的紀錄檔案,若模擬失敗會在 CIW (command Interpreter window) 訊息顯示訊息,參考各記錄檔案可明確了解須修正的錯誤。

AMS Designer 可依使用者習慣區分不同的方式來做驗證

AMS-ADE 支援容易上手的 Virtuoso 圖形化使用者介面 (GUI) 的整合驗證方式來加速驗證過程所需的時間,而針對數位 IC 設計者常習慣在 batch mode 去下指令 (Command),AMS-irun 也支援 Incisive 模擬器透過命令列的方式去執行指令來做驗證。

「支援以數位區塊為主的混合信號驗證」與「導入低功率混合信號驗證解決方案」

針對數位區塊為主的設計,採用事件驅動 (Event Driven) 的架構以及 wreal 的模型化來達到高性能,而且 AMS 支援指標驅動 (Metric Driven) 的驗證方式可透過涵蓋率 (coverage) 這項指標來提升生產力及完整性,另外,針對類比混合性信號設計也導入低功率解決方案來協助設計者設計驗證低功率的電路設計。