# Cadence Physical Verification System

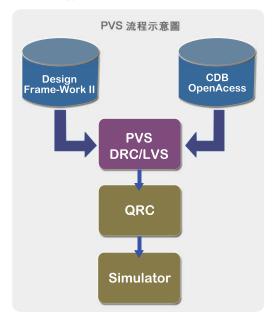

Cadence® Physical Verification System(PVS) 是由 EDA 軟體商 Cadence 所提出之新一代晶片驗証工具,它不僅能使用於類比/數位/混合訊號之設計平台,如 Virtuoso IC Layout Platform、Encounter,且更與寄生參數萃取軟體整合,如 QRC,以萃取佈局後寄生參數,提供使用者在晶片後段驗証的完整解決方案。

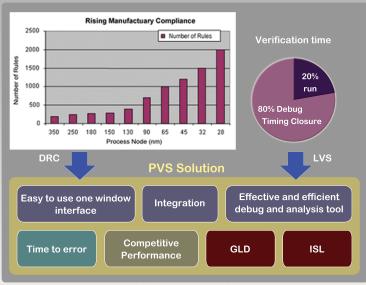

隨著半導體製程微縮的發展趨勢,晶片後段驗証 (Back-end Verification) 所耗費的處理時間與複雜度不斷提昇的情況下,Cadence® Physical Verification System(PVS) 驗証工具,憑其線性化的優異性能表現 (Performance),不僅能減少運算處理時的等待時間;另外其創新的即時值錯 (Time-To-Error) 功能,即時值錯已運算完成部份,讓使用者不再浪費時間等待運算結果,再者,其新創的人性化圖形除錯界面 (Graphic LVS Debug Interface)及互動式短路值察系統 (Interactive Short Locator),不僅能有效彌補值錯經驗不足的困擾,更能有效縮短來回除錯所耗費的時間 (Turn Around Time),以提昇工程師的效率及晶片產出。

此外,Cadence® Physical Verification System(PVS) 不僅同時支援 GDSII 與Open-Access 的格式,亦相容於目前工業界標準的驗証語言,以降低工程師跨平

台使用上的額外工作與難度。

Your EDA Partner

# Cadence Physical Verification System

PVS後段驗証解決方案示意圖

#### PVS DRC

- Easy to use one window interface

- · Time to error

- -Error Browser will pop up and allow viewing of errors while job is still running.

- Standard DRC Browsing capabilities

- -By Cell/ By Rule

- Error Waivers

# Time To Error

Error Browser will pop up and allow viewing of errors while job is still running.

## PVS LVS

轉換無障礙

· 內建類似業界標準語法之DRC/LVS命令文檔· 相容性高

支援業界標準語法之DRC/LVS命令文檔

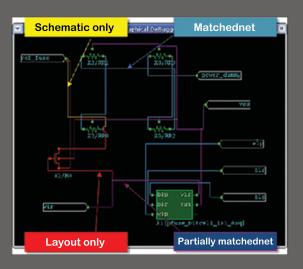

#### Rapidly identifies complex LVS mismatches

Graphic LVS Debug accelerates identification of complex LVS mismatches in chip designs

- Compares logical and physical design using a common schematic representation

- Guides navigation using design errors

- Can be launched with LVS debug environment, and graphical elements can be probed through the LVS debug environment

- All errors and warnings are easily navigated and show surrounding context

Strong functionalities and flexible usability

- Error Tags

- · World view or detail view

- · Filter net, devices for better understanding of error

- Drill down for more information on points of interest

- etc

#### LVS Hyper debugger --- Graphical LVS Debug

LVS debug is extremely time-consuming and experience dependent

- · Limitation of current tools

- -Static error report in batch mode, contain large data, difficult to understand

- -Errors in text report hard to identify relationship.

- -User cannot actively query more information on points of interest

- -Not allow easy navigation of the original design

- · Bind-key --- Cadence Composor like

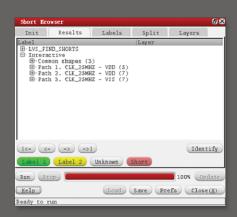

#### LVS --- Interactive Short Locator

### One-pass short isolation

- Locating shorts found in old-fashion LVS comparison report requires:

- -Additional manual work

- -Additional LVS extraction and comparison runs

- PVS approach facilitates one-pass short isolation for cell/block/full-chip designs

- -Run time typically <10% of extraction time and scales up to 5x with 8 CPUs

- -Start debugging while run is in progress as soon as first results are available

#### Interactive Short Locator --- Customer Testimony

| Node | Extraction Time      | TAT wi ISL         | TAT wo ISL |

|------|----------------------|--------------------|------------|

| 40nm | 1 hr 30 min (8 CPUs) | 30 min             | 2 hours    |

| 45nm | 1 hr 15 min (8 CPUs) | 3.3 hours          | 8 hours    |

| 65nm | 1 hr 20 min (8 CPUs) | 20 min<br>428 shrt | NA         |

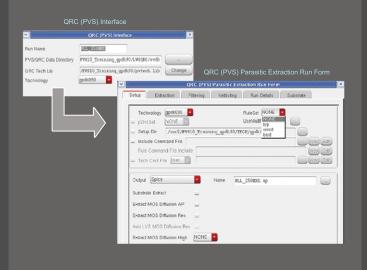

#### PVS to QRC interface

#### Fully solution for back-end verification ---

Support Cadence QRC flow to complete post-layout simulation

- · No additional licenses required to enable flow

- · Provides complete QRC GUI support

- TECHLIB feature makes PVS QRC flow easy to use

- Batch / interactive use model

- Support Spice, SPEF, DSPF, extracted view, etc. flows

- Parity of flow between PVS / Assura = easy transition