# An Alternative Signoff Approach - IBIS+AMI Models

Skipper Liang Graser Annual User Conference 2016 2016.July

cādence<sup>®</sup>

### Agenda

Traditional signoff flow – circuit simulation

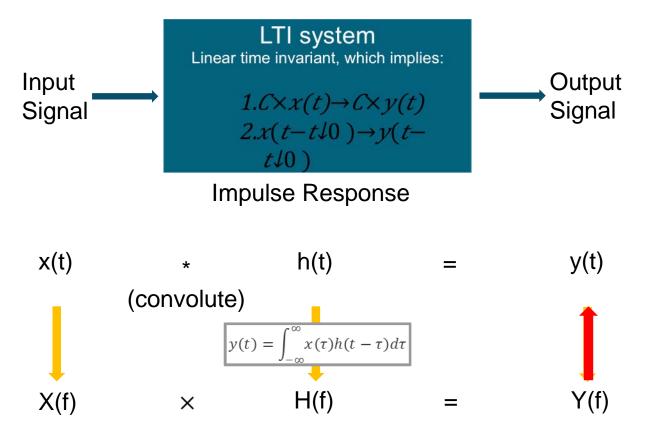

Channel simulation LTI system Channel simulation

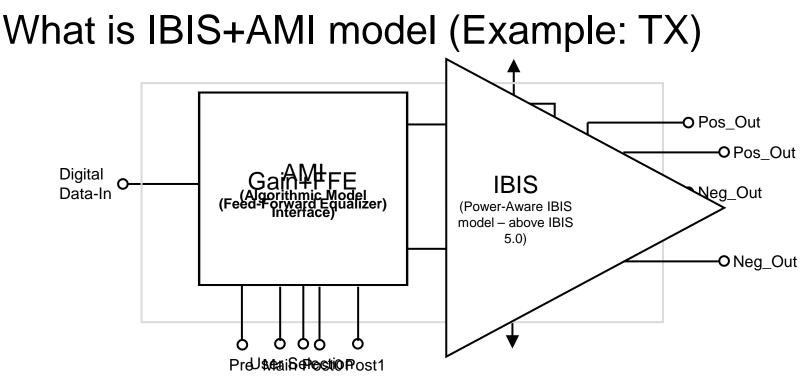

IBIS+AMI model What is IBIS+AMI model And your concerns?

**IBIS+AMI** model signoff flow

Why Cadence?

A real case

Conclusion

More than model generation/validation/simulation...

#### Traditional signoff flow – circuit simulation

#### **Channel simulation**

LTI systen

D.Channel Cimulation

#### IBIS+AMI model What is IBIS+AMI m

EAnd your concerne?

#### **IBIS+AMI** model signoff flow

Why Cadence?

A real case

Conclusion

More than model generation/validation/simulation..

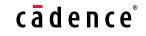

### Traditional signoff flow – Using transistor **SPICE netlist** model

1 ngnd 5 1 ngnd 5 1 ngnd 5 1 ngnd 5 R31 R41 R71 R81

Rshort pwr in pw

Circuit simulation:

#### 1. Kirchhoff's current law (KCL)

At any node (junction) in an electrical circuit, the sum of current flowing into that node is equal to the sum of currents flowing out of that node

#### 2. Kirchhoff's voltage law (KVL)

The directed sum of the electrical potential differences (voltage) around any closed network is zero

© 2016 Cadence Design Systems, Inc. All rights reserved. 4

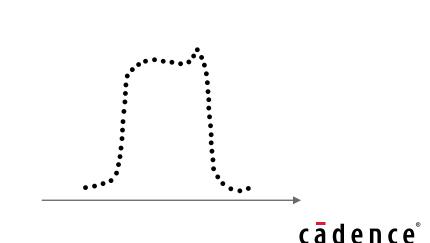

### Traditional signoff flow – Using transistor **SPICE netlist** model (con't)

#### Advantages:

- Accurate PI prediction under limited bits transmission

- Accurate jitter prediction under limited bits transmission

#### Disadvantages:

- Very slow for SPICE netlist model - Takes weeks/months to get bit error-rate (BER) prediction

- Can't model the adaptive mechanism in RX

### Agenda

#### Traditional signoff flow – circuit simulation

Channel simulation LTI system Channel simulation

BIS+AMI model What is IBIS+AMI mod

**IBIS+AMI** model signoff flow

Why Cadence?

A real case

Conclusion

More than model generation/validation/simulation..

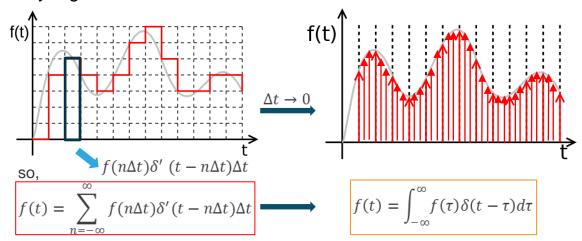

# LTI – Linear time invariant (con't.)

Signal expressed in an impulse-train format:

• Any Signal:

•

7 © 2016 Cadence Design Systems, Inc. All rights reserved.

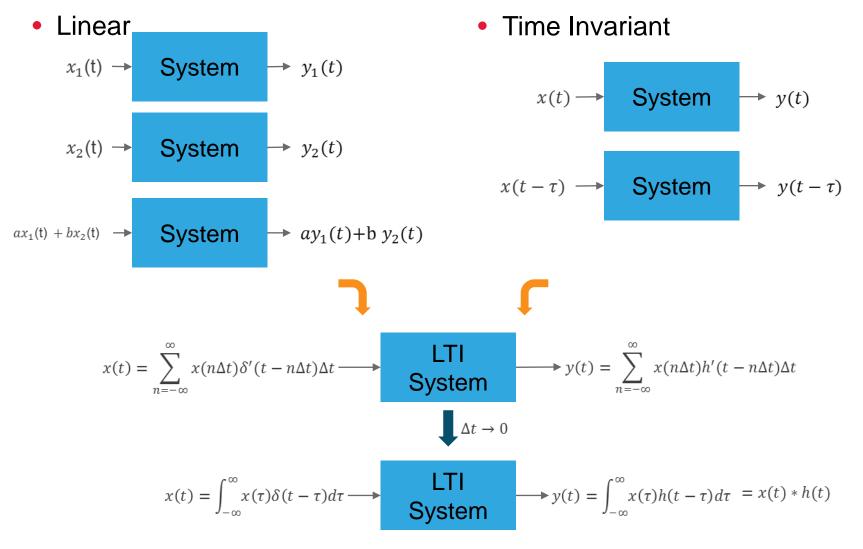

# LTI – Linear time invariant (Con't.)

# **Channel-Sim**

Channel simulation :

Multi-times faster than circuit simulation!!

What if the system is not an LTI one?

cādence

### Agenda

#### Traditional signoff flow – circuit simulation

Channel simulation

- Channel Cimulation

#### IBIS+AMI model What is IBIS+AMI model And your concerns?

**IBIS+AMI** model signoff flow

Why Cadence?

A real case

Conclusion

More than model generation/validation/simulation..

Accompanied with channel simulator:

- PI prediction with good accuracy without limits on transmission bits

- Jitter prediction with good accuracy without limits on transmission bits

- Very fast for IBIS+AMI netlist model -Takes minutes to get BER prediction

- Can model the adaptive mechanism in RX

But you might be concerned:

### cadence°

### Agenda

#### Traditional signoff flow – circuit simulation

#### **Channel simulation**

**LTI** system

D.Channel Cimulation

#### IBIS+AMI model What is IBIS+AMI m

### **IBIS+AMI** model signoff flow

Why Cadence?

A real case

Conclusion

More than model generation/validation/simulation..

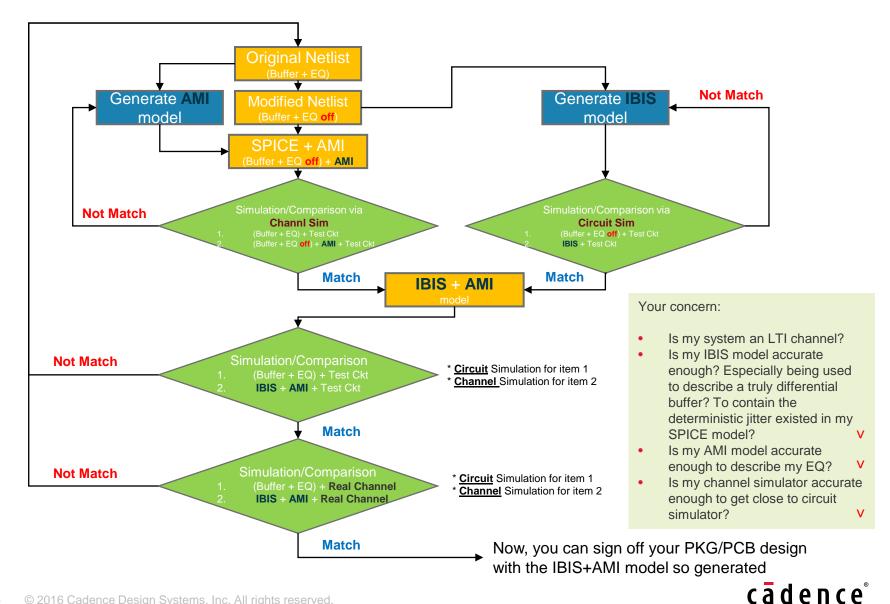

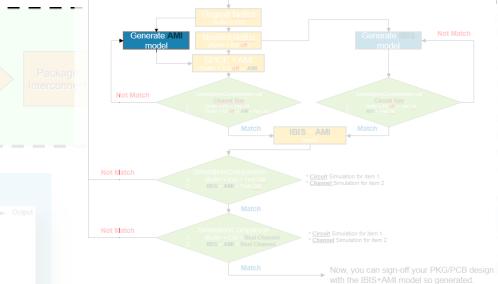

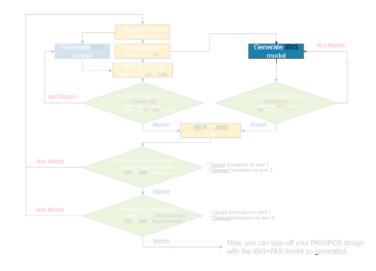

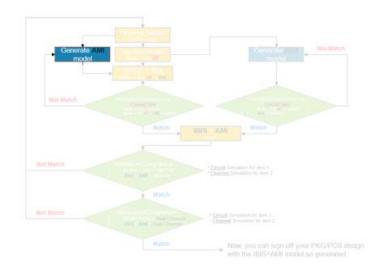

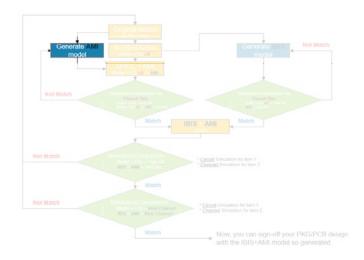

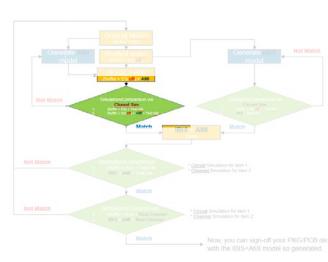

### **IBIS+AMI** model signoff flow

### Agenda

#### Traditional signoff flow – circuit simulation

#### **Channel simulation**

**DLTI** system

D.Channel Cimulation

# IBIS+AMI model

**IBIS+AMI** model signoff flow

Why Cadence?

A real case

Conclusion

14

More than model generation/validation/simulation..

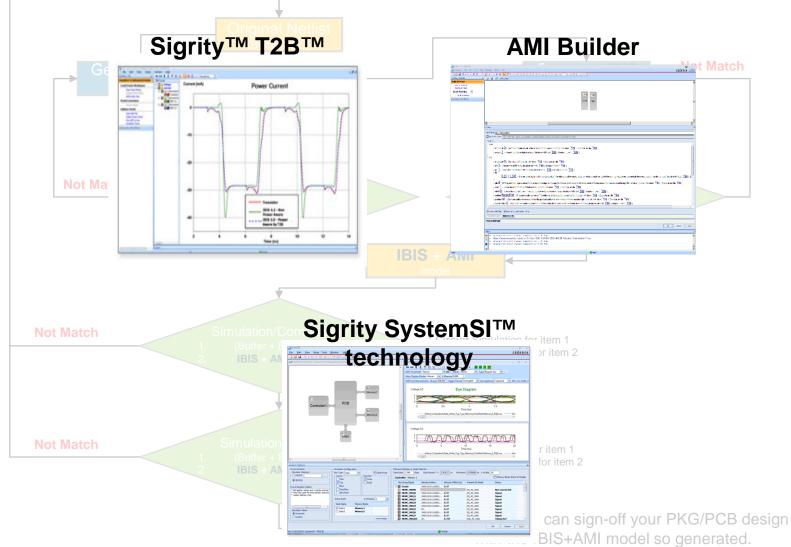

### Why Cadence?

15

cādence°

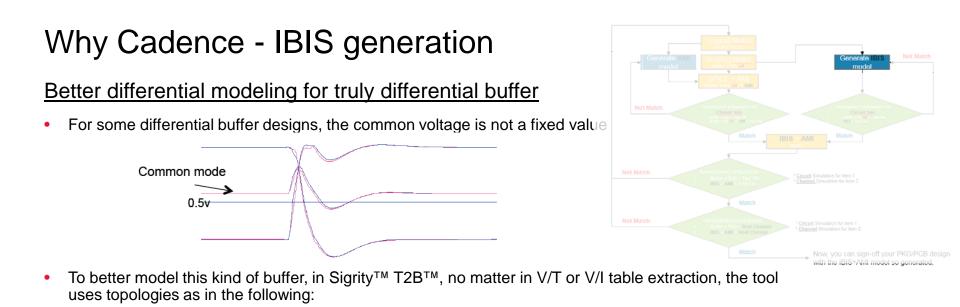

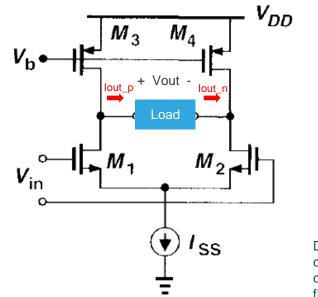

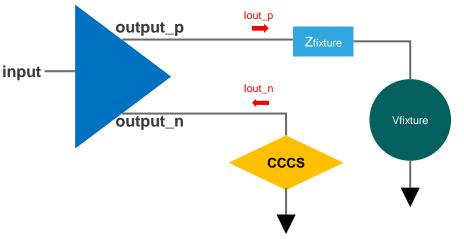

During modeling one of the positive and negative, Sigrity T2B will add a CCCS (current controlled current source) at the other side, with the value exactly the same as the current flowing out of the V<sub>fixture</sub> but in the opposite direction, to make sure the current flowing out of the positive pin coincides with the current flowing into the negative pin

### cādence<sup>®</sup>

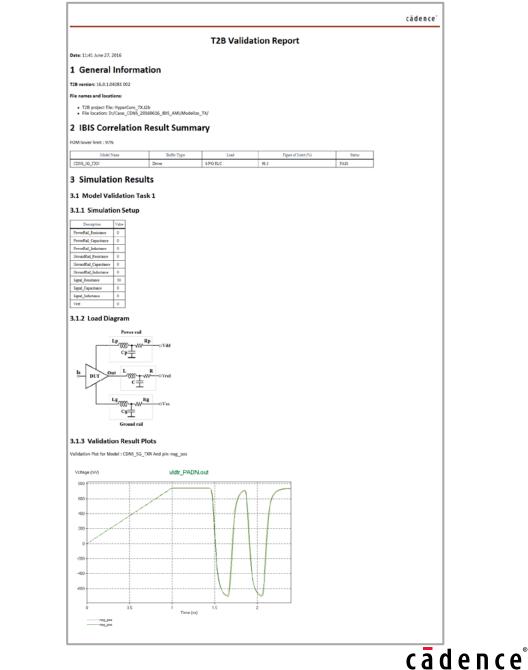

### Why Cadence – IBIS generation: Sigrity T2B (con't.)

#### Validation and report

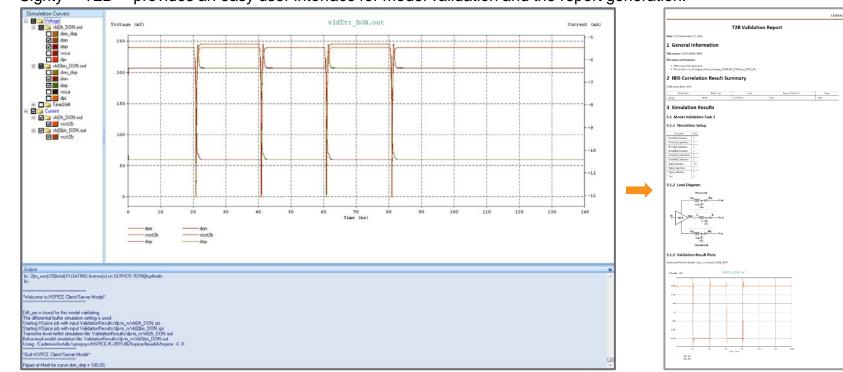

• Sigrity<sup>™</sup> T2B<sup>™</sup> provides an easy user interface for model validation and the report generation.

• A quantized mark for pass/fail criteria is introduced: FOM (Figure of Merit)

$$FOM = 100 \bullet \left[ 1 - \frac{\sum_{i=1}^{N} |Y_i(LAB) - Y_i(IBIS)|}{\Delta Y \bullet N} \right]$$

△Y: (Max-Min) of HSPICE waveform

### cādence®

### Why Cadence - IBIS generation: Sigrity T2B (con't.)

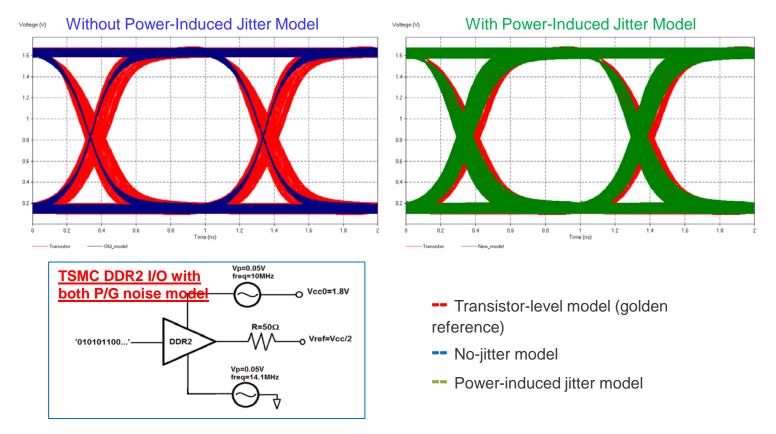

#### IBIS+ model

• Jitter aware and truly differential

#### Patent Pending

Several models for different power voltages, such as, typ/min/max, will be built into the new model which can be dynamically composed according to the real power voltage during the circuit simulation

### cādence<sup>®</sup>

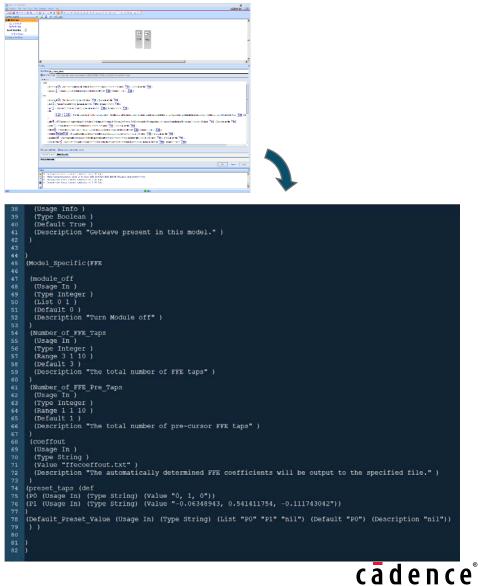

### Why Cadence - AMI generation: advanced AMI Builder

An abundant and rich library for you to describe your EQ design

### A friendly user interface to guide you through the model generation process

- Fast and accurate

- AGC adaption will be based on SNR or DFE

- © 2016 Cadence Design Systems, Inc. All rights reserved.

- cadence

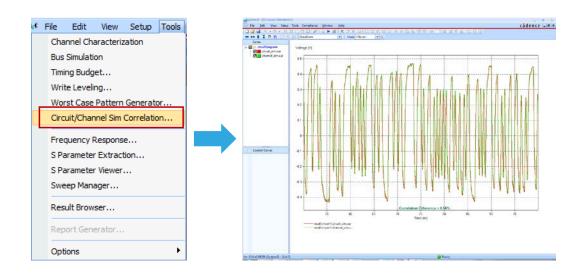

# Why Cadence – simulation: Sigrity SystemSI

One click to know if your system/channel to be analyzed can be treated as LTI or not:

Your concern:

- Is my system an LTI channel?

- Is my IBIS model accurate enough? Especially being used to describe a truly differential buffer? To contain the deterministic jitter existed in my SPICE model?

- Is my AMI model accurate enough to describe my EQ?

- Is my channel simulator accurate enough to get close to circuit simulator?

### cādence°

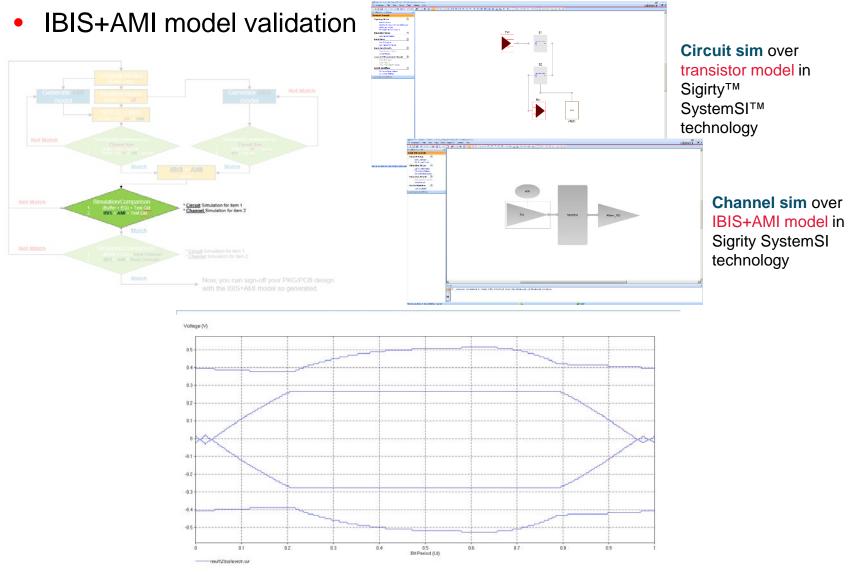

# Why Cadence – simulation: Sigrity SystemSI (con't.)

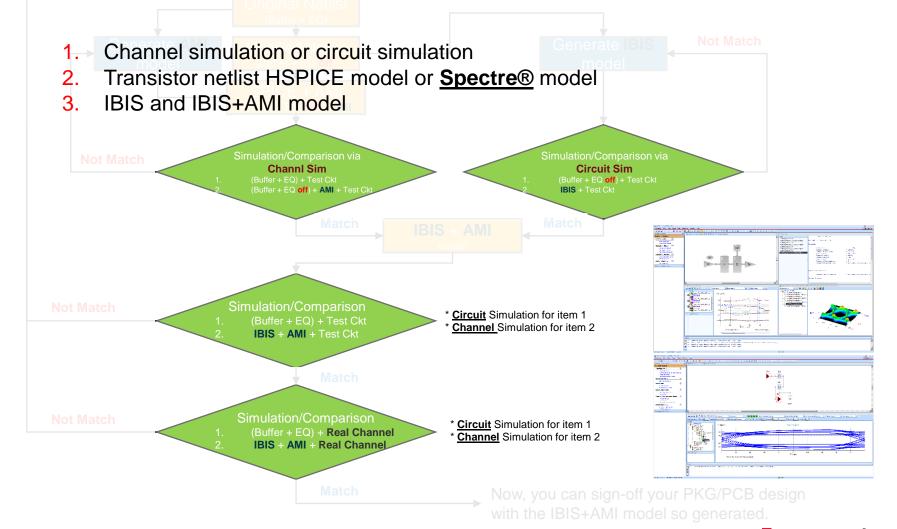

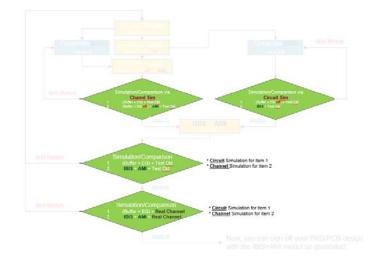

All these four blocks of simulation for model's validation can be done in Sigrity<sup>™</sup> SystemSI<sup>™</sup> technology no matter:

cādence

21 © 2016 Cadence Design Systems, Inc. All rights reserved.

### Why Cadence – simulation: Sigrity SystemSI (con't.)

- All these four blocks of simulation for model's validation can be done in Sigrity<sup>™</sup> SystemSI<sup>™</sup> technology no matter:

- 1. Channel simulation or circuit simulation

- 2. Transistor netlist HSPICE model or Spectre® model

- 3. IBIS and IBIS+AMI model

# Why Cadence ?

Now, please help yourself by checking:

### For IBIS model:

- 1. Does your IBIS generation tool describe a truly differential buffer well enough?

- 2. Are you forced to give up the V/T information in your IBIS during channel simulation due to channel simulation engine or extraction methodology?

- **3.** Or, can you just use a "Dummy" IBIS model (generated by AMI model generation tool) which behaves in just a different way from your own design?

# Why Cadence? (con't.)

• Now, please help yourself to check:

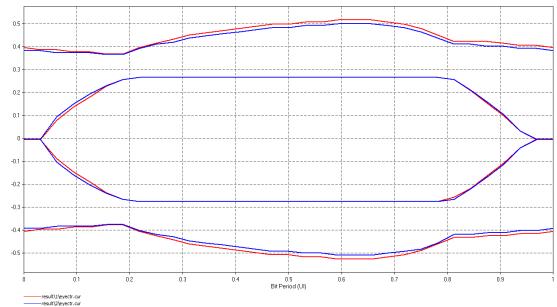

### For AMI model:

- 1. Does your AMI generation tool provide you a convenient way to validate your AMI model by:

- Channel simulation over your netlist of Buffer+EQ\_on

- Channel simulation over your netlist of Buffer+EQ\_off combined with AMI model so generated?

# Why Cadence ? (con't.)

• Now, please help yourself to check:

### For simulation:

- 1. Does your channel simulator tell you how LTI your system is with only onebutton click?

- 2. Does your channel/circuit simulator work with <u>Spectre®</u> netlist?

- 3. Does your channel simulator give results close enough to the result generated by circuit simulator? Is it easy to validate this item in your simulator?

- 4. Does your channel simulator provide power-aware result?

### Agenda

#### Traditional signoff flow – circuit simulation

#### **Channel simulation**

**DLTI** system

D.Channel Cimulation

# IBIS+AMI model

BIS+AMI model signoff flow

Why Cadence?

#### A real case

Conclusion

26

More than model generation/validation/simulation..

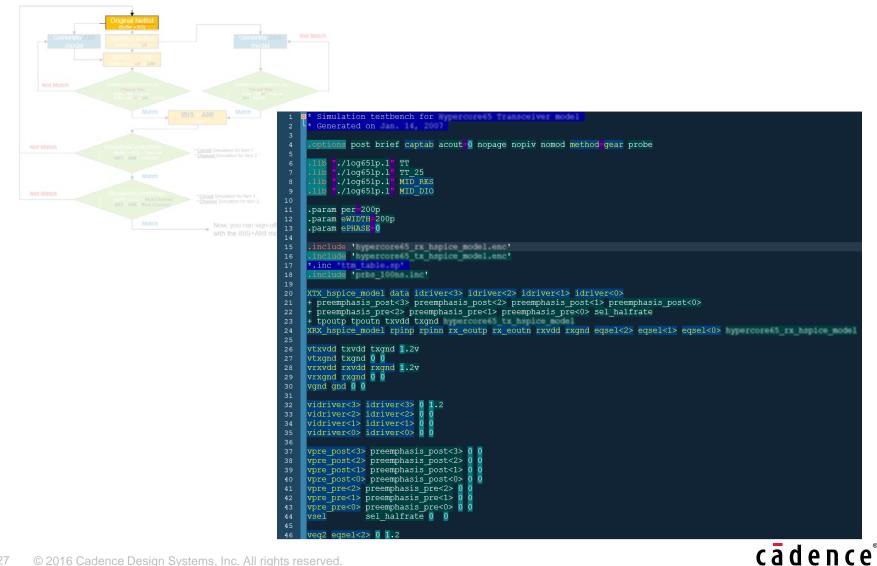

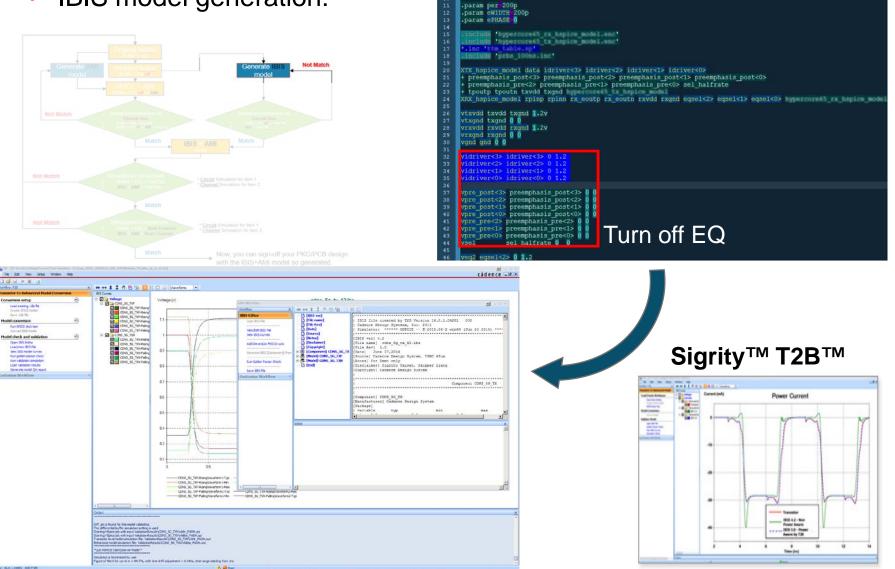

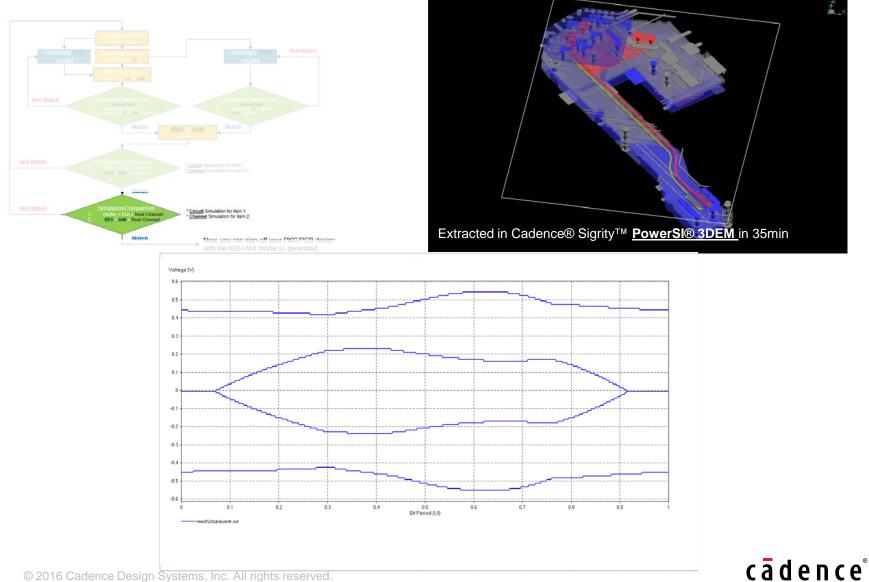

The original SPICE netlist: •

• AMI model generation:

#### **AMI Builder**

• AMI model validation:

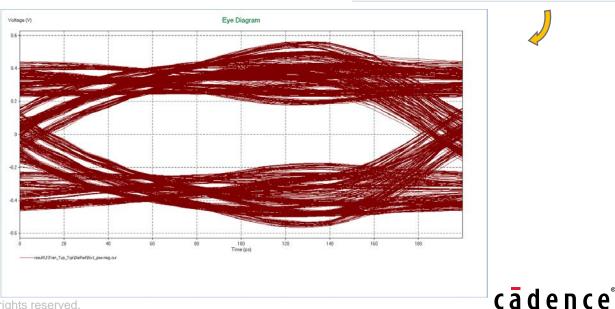

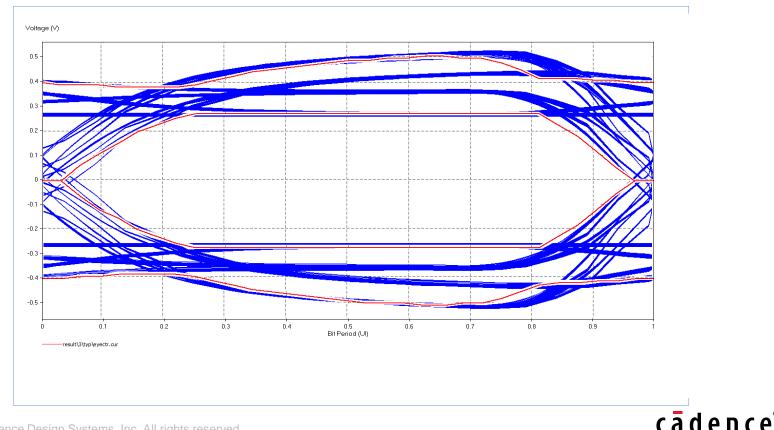

Voltage (V)

• IBIS model generation:

Generated on Jan. 14, 2007

./log651p.1 TT ./log651p.1 TT 25 ./log651p.1 MID RES ./log651p.1 MID\_DIO

ns post brief captab acout 0 nopage nopiv nomod method gear probe

cadence

• IBIS model validation

#### Sigrity<sup>™</sup> T2B<sup>™</sup>

cādence

• IBIS+AMI model validation over a real channel

### Agenda

#### Traditional signoff flow – circuit simulation

#### **Channel simulation**

**DLTI** system

D.Channel Cimulation

# IBIS+AMI model

BIS+AMI model signoff flow

Why Cadence?

A real case

#### Conclusion

More than model generation/validation/simulation..

# Conclusion

- An accurate IBIS+AMI model could be an alternative approach to validate your "system" design versus a transistor netlist model

- An accurate IBIS+AMI model consists of two parts an <u>accurate IBIS model</u> and <u>an</u> <u>accurate AMI model</u> – <u>validation</u> is the key

- An accurate IBIS should be generated by a tool which can well describe a <u>truly</u> <u>differential pair</u> in all V/I, V/T and I/T curves, such as Sigrity<sup>™</sup> T2B<sup>™</sup> technology

- An accurate AMI model should be generated by a tool with a rich library such that the generation tool can use all available means in the library to describe all your possible designs, such as Cadence® AMI Builder

- A simulation environment which supports transistor netlist models not only HSPICE, but also Spectre® simulation - is fundamental for IBIS+AMI model generation/validation, such as Sigrity<sup>™</sup> SystemSI<sup>™</sup> technology

- Sigrity SystemSI technology provides <u>good correlation between channel simulation</u> and circuit simulation Now, only with Sigrity SystemSI, you can trust channel simulation as you used to trust circuit simulation.

- More than model generation/validation and system simulation, Sigrity SystemSI + AMI Builder tools also provide a handy EQ design environment.....

### Agenda

#### Traditional signoff flow – circuit simulation

#### **Channel simulation**

LTI system

D.Channel Cimulation

#### IBIS+AMI model What is IBIS+AMI

#### **IBIS+AMI** model signoff flow

Why Cadence?

A real case

Conclusion

More than model generation/validation/simulation...

### cādence®

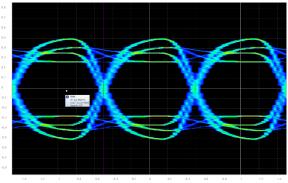

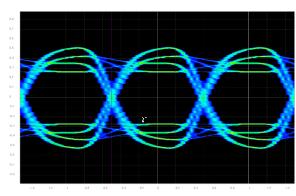

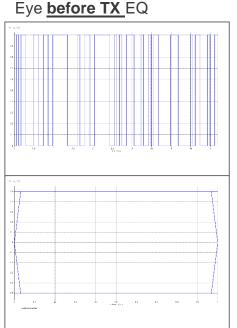

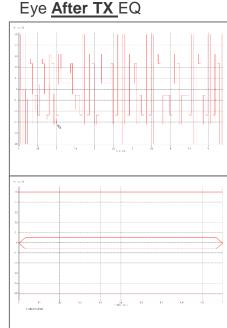

# Sigrity SystemSI – probe all eyes at every stage

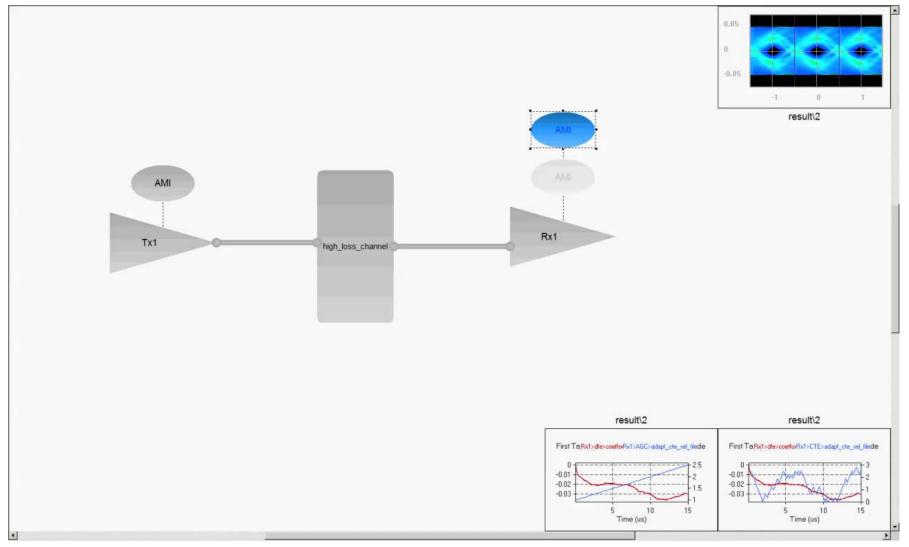

Accompanied with Sigrity<sup>™</sup> SystemSI<sup>™</sup> SLA, advance EQ designer can use "<u>Probe</u> <u>all eyes</u>" and "<u>Output last</u> <u>1000 bits at Tx\_input</u>, <u>Tx\_output, Rx\_input</u>" to validate if the EQ works properly

© 2016 Cadence Design Systems, Inc. All rights reserved.

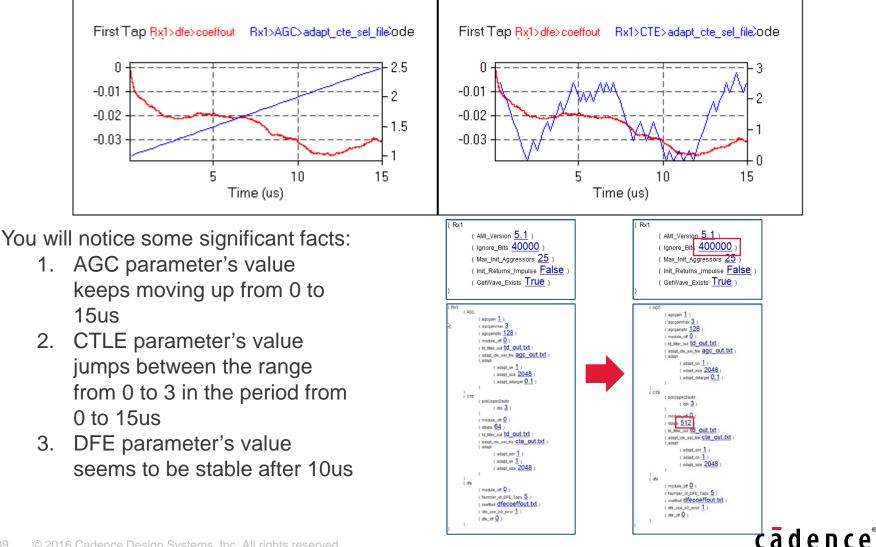

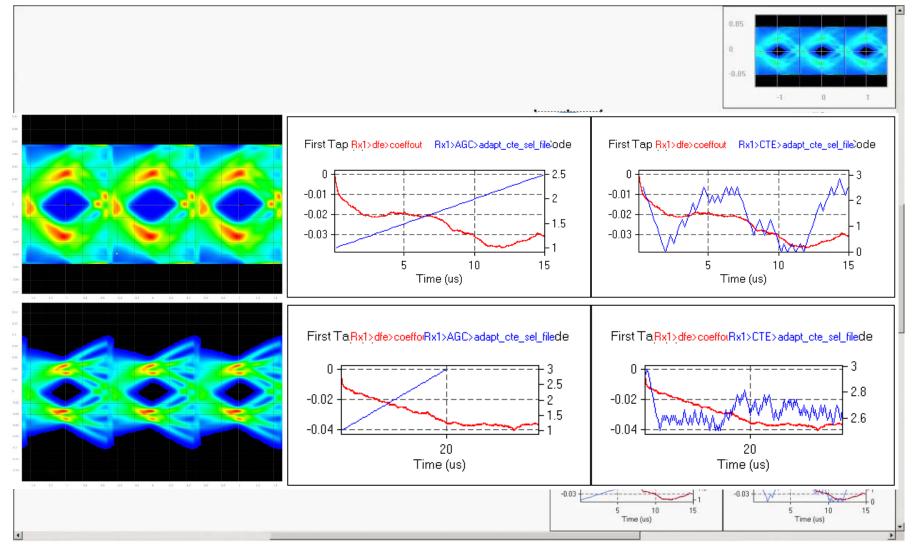

While using AMI Builder's AMI model in Sigrity<sup>™</sup> SystemSI<sup>™</sup> SLA, you will be able to observe the evolution of EQ adaption and it will help you have a more clear picture about how the equalizer works

### cādence°

As you can see, in this simulation, the adaption is not stable yet. The parameters of AGC, CTLE, and DFE are still under tuning to find a better value.

### cādence°

### cādence°

# cādence®

© 2016 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, PowerSI, and Spectre are registered trademarks and Sigrity, SystemSI, and T2B are trademarks of Cadence Design Systems, Inc. in the United States and other countries. All rights reserved. All other trademarks are the property of their respective owners.