## High Speed Serdes Signal Design Analysis with CTLE

Cliff Lin 2015/10/15

# Abstract

- Source of Signal Loss

- Pre-emphasis and Equalization

- USB 3.0 transmitter compliance test considerations

- USB 3.0 transmitter channel design case study

- Summary

# **Source of Signal Loss**

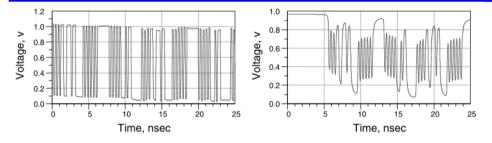

The important consequence of frequency-dependent loss and rise-time degradation is ISI: The precise waveform of the bit pattern will depend on the previous bits that have passed by. ISI is a significant contributor to jitter.

**Figure 9-3** 5-Gbps pseudorandom bit stream. Left: bit pattern when the rise time is much shorter than the bit period. Right: bit pattern when the rise time is comparable to the bit pattern, causing pattern-dependent voltage levels or intersymbol interference.

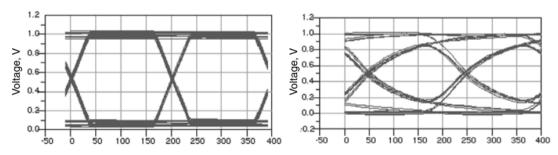

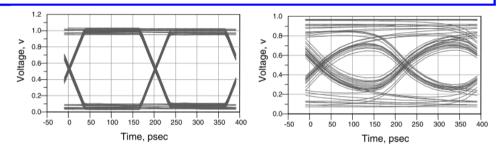

**Figure 9-5** Eye diagrams of a 5-Gbps pseudorandom bit stream. Left: little loss. Right: same bit pattern still with no loss, but a 4-pF capacitive discontinuity from four through-hole vias.

**Figure 9-4** Eye diagrams of a 5-Gbps pseudorandom bit stream. Left: little loss. Right: same bit pattern when there is a lot of loss, showing the collapse of the eye diagram, and increased jitter, indicated by the widening of the cross-over regions.

# **Source of Signal Loss**

It is important to note that the resistivity of copper, and most conductors, is very constant with frequency. Above about 10 MHz, the resistance per length of the signal path will be frequency dependent. Skin depth is driven by the need for the currents to take the path of the lowest impedance, which is dominated by the loop inductance at higher frequencies.

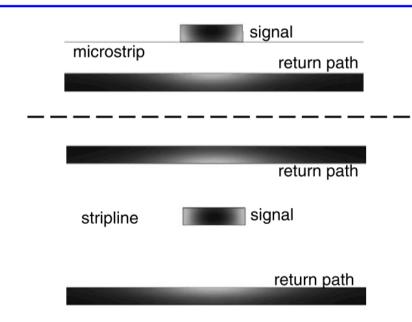

**Figure 9-6** Current distribution in 1-ounce copper, for near 50-Ohm lines, at 10 MHz, showing onset of current redistribution due to skin-depth effects. Top: microstrip. Bottom: stripline. The lighter the color, the higher the current density. Simulated with Ansoft's 2D Extractor.

At ADLINK, We CARE

$$R = \rho \frac{Len}{w \times \delta}$$

where:

R = the resistance of the line, in Ohms

$\rho$  = the bulk resistivity of the conductor, in Ohm-inches

Len = the length of the line, in inches

w = the line width, in inches

$\delta$  = the skin depth of the conductor, in inches

# **Source of Signal Loss**

The dissipation factor, usually written as the tangent of the loss angle,  $tan(\delta)$ , and also abbreviated sometimes as Df, is a measure of the number of dipoles in the material and how far each of them can rotate in the applied field.

The ratio of the powers, in dB, is:

$$r_{dB} = 10 \times \log\left(\frac{P_{1}}{P_{0}}\right) = 10 \times \log\left(\frac{V_{1}}{V_{0}^{2}}\right) = 10 \times 2\log\left(\frac{V_{1}}{V_{0}}\right) = 20\log\left(\frac{V_{1}}{V_{0}}\right)$$

(9-52)

| Voltage<br>Ratio | Power<br>Ratio | dB  |

|------------------|----------------|-----|

| 100              | 10,000         | 40  |

| 10               | 100            | 20  |

| 2                | 4              | 6   |

| 1.4              | 2              | 3   |

| 1                | 1              | 0   |

| 0.7              | 0.5            | -3  |

| 0.5              | 0.25           | -6  |

| 0.1              | 0.01           | -20 |

| 0.01             | 0.0001         | -40 |

# Abstract

- Source of Signal Loss

- Pre-emphasis and Equalization

- USB 3.0 transmitter compliance test considerations

- USB 3.0 transmitter channel design case study

- Summary

At ADLINK, We CARE

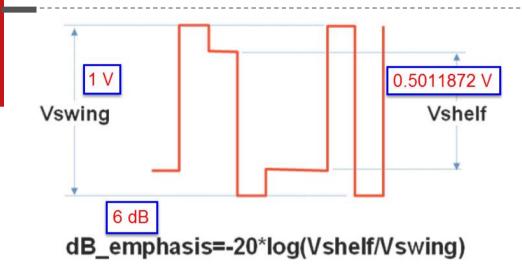

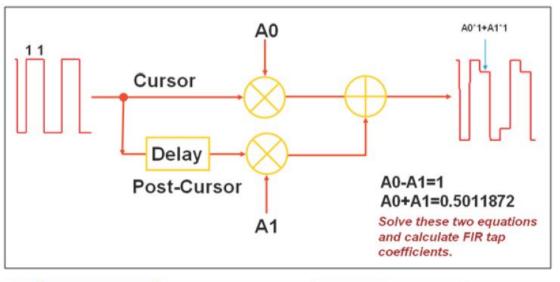

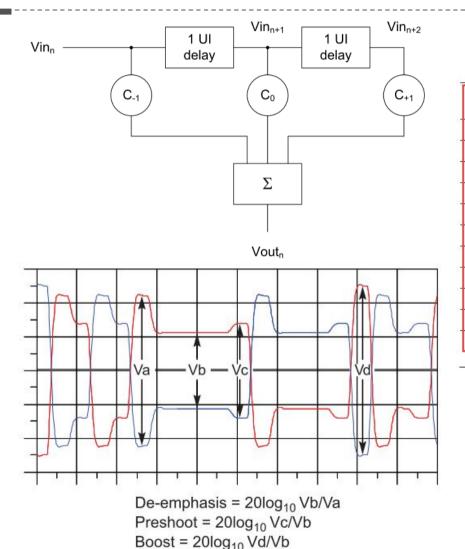

A de-emphasized waveform is defined in terms of the voltage levels called Vshelf and Vswing.

Vshelf is calculated first for a given level of de-emphasis.

Each unique channel has some optimum amount of transmitter de-emphasis that will deliver the best eye performance.

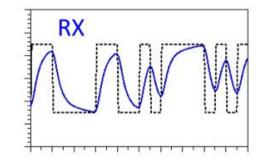

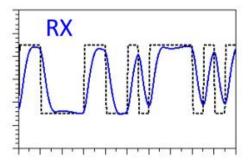

Figure 1. High frequency loss results in signal deterioration at RX

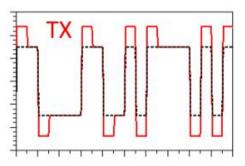

Figure 2. High frequency compensation with pre-emphasis

Cursor tap1 = (1+ Vshelf) / 2

Post cursor tap2 = tap1 - 1

Table 4-16: Tx Preset Ratios and Corresponding Coefficient Values

| Preset<br>Number | Preshoot<br>(dB) | De-emphasis<br>(dB) | C.1    | C <sub>+1</sub> | Va/Vd | Vb/Vd          | Vc/Vd          |

|------------------|------------------|---------------------|--------|-----------------|-------|----------------|----------------|

| P4               | 0.0              | 0.0                 | 0.000  | 0.000           | 1.000 | 1.000          | 1.000          |

| P1               | 0.0              | -3.5 ± 1 dB         | 0.000  | -0.167          | 1.000 | 0.668          | 0.668          |

| P0               | 0.0              | -6.0 ± 1.5 dB       | 0.000  | -0.250          | 1.000 | 0.500          | 0.500          |

| P9               | 3.5 ± 1 dB       | 0.0                 | -0.166 | 0.000           | 0.668 | 0.668          | 1.000          |

| P8               | 3.5 ± 1 dB       | -3.5 ± 1 dB         | -0.125 | -0.125          | 0.750 | 0.500          | 0.750          |

| P7               | 3.5 ± 1 dB       | -6.0 ± 1.5 dB       | -0.100 | -0.200          | 0.800 | 0.400          | 0.600          |

| P5               | 1.9 ± 1 dB       | 0.0                 | -0.100 | 0.000           | 0.800 | 0.800          | 1.000          |

| P6               | 2.5 ± 1 dB       | 0.0                 | -0.125 | 0.000           | 0.750 | 0.750          | 1.000          |

| P3               | 0.0              | -2.5 ± 1 dB         | 0.000  | -0.125          | 1.000 | 0.750          | 0.750          |

| P2               | 0.0              | -4.4 ± 1.5 dB       | 0.000  | -0.200          | 1.000 | 0.600          | 0.600          |

| P10              | 0.0              | See Note 2.         | 0.000  | See<br>Note 2.  | 1.000 | See Note<br>2. | See Note<br>2. |

PCI EXPRESS BASE SPECIFICATION, REV. 3.0

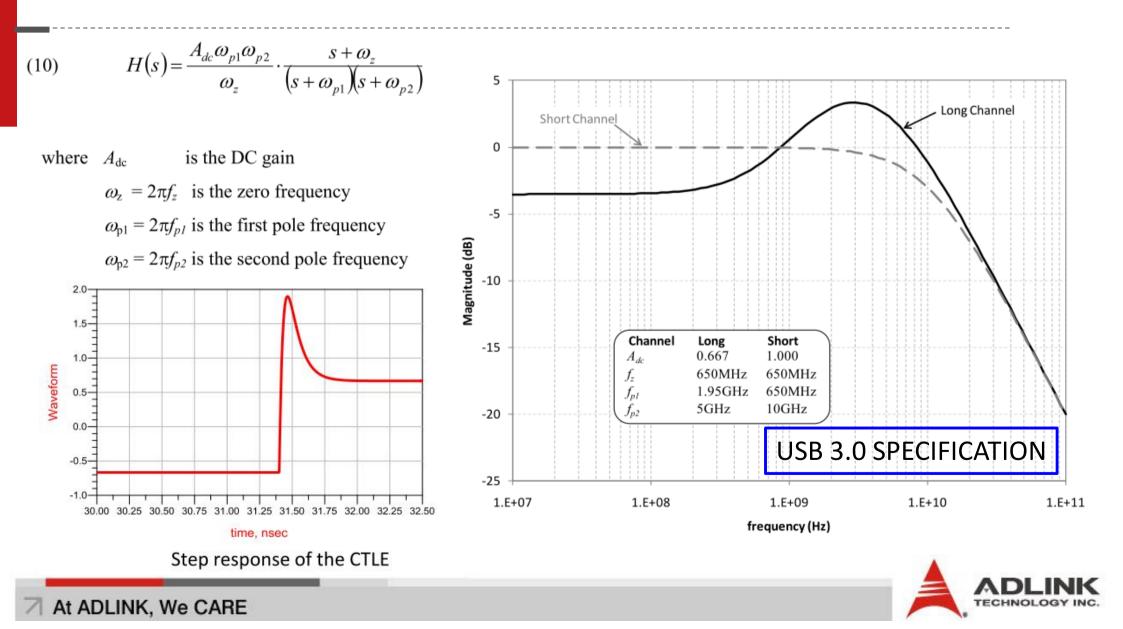

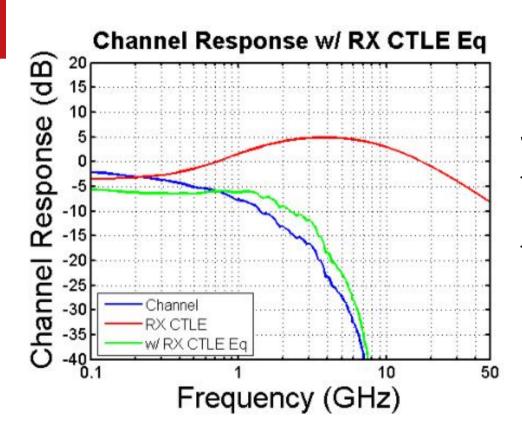

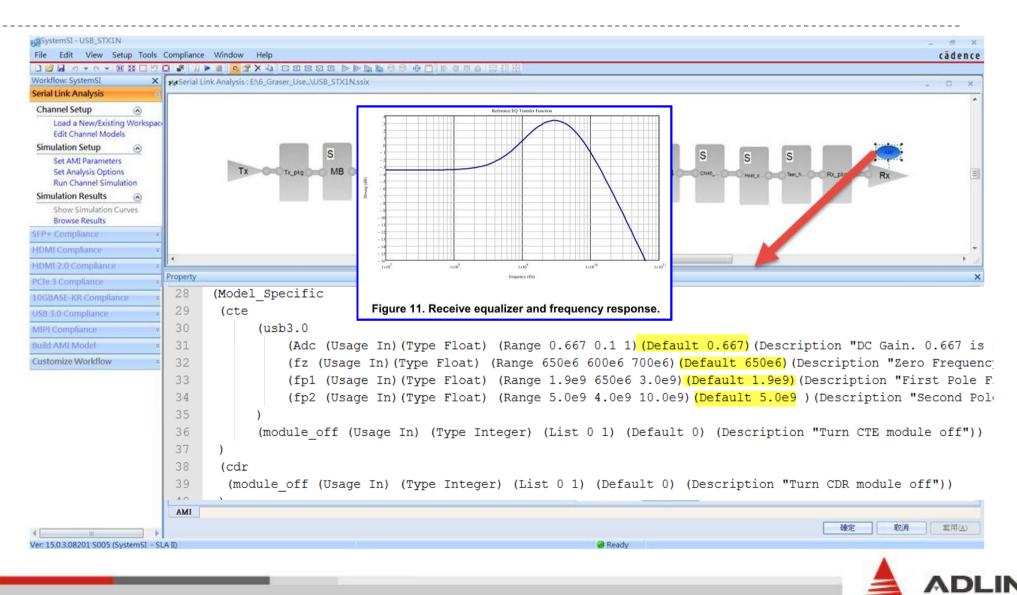

When a high speed digital signal propagates through a lossy channel, RX CTLE is used to boost high frequency components of the signal to compensate high frequency channel loss.

# Abstract

- Source of Signal Loss

- Pre-emphasis and Equalization

- USB 3.0 transmitter compliance test considerations

- USB 3.0 transmitter channel design case study

- Summary

DUT

U-026

Cable

|                                                   | 5GT/s            |                 |                                                      | 10GT/s                     |                |             |                       |                                      |

|---------------------------------------------------|------------------|-----------------|------------------------------------------------------|----------------------------|----------------|-------------|-----------------------|--------------------------------------|

| Signal<br>Characteristic                          | Minimum          | Nominal         | Maximum                                              | Minimum                    | Nominal        | Maximu<br>m | Unit<br>s             | Note                                 |

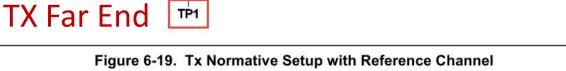

| Eye Height                                        | 100              |                 | 1200                                                 | 70                         |                | 1200        | mV                    |                                      |

| Dj                                                |                  |                 | 0.43                                                 |                            |                | 0.530       | UI                    | 300                                  |

| Rj                                                |                  |                 | 0.23                                                 |                            |                | 0.184       | UI                    | 250 -<br>200 -                       |

| Tj                                                |                  | 1               | 0.66                                                 |                            |                | 0.714       | UI ≧                  | 150                                  |

| 4. The eye heig                                   | ght is to be mea | asured at the n | nd cables at TP<br>ninimum openin<br>69 times the RN | g over the rang            | ge from the ce |             | Differential Voltage, | -100 -<br>-150 -<br>-200 -<br>-250 - |

| The complianc<br>(TP1), and the<br>reference equa | Tx specifica     | ations are ap   | oplied after p                                       | rocessing the next section | e measured     | data with   |                       | -3000                                |

SMP

**Test Channel**

Gen 1 eye mask

At ADLINK, We CARE

Tool

#### Table 3. Summary of transmitter compliance tests

| Parameter                                                                                                                                             | Symbol                             | Specification                   | Data Pattern          | Notes      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|-----------------------|------------|

| Differential Swing                                                                                                                                    | V <sub>TX-DIFF-PP</sub>            | 0.8V - 1.2V                     | CP8                   | 4, 5       |

| De-emphasis                                                                                                                                           | V <sub>TX-DE-RATIO</sub>           | 3.0dB - 4.0dB                   | CP7                   | 4, 5       |

| DC differential impedance                                                                                                                             | R <sub>TX-DIFF-DC</sub>            | 72Ω - 120Ω                      | CP8                   | 4, 5       |

| Deterministic Jitter                                                                                                                                  | Dj                                 | 0.465UI (max)                   | CP0                   | 1, 2, 4    |

| Random Jitter                                                                                                                                         | Rj                                 | 0.30UI (max)                    | CP0, CP1              | 1, 2, 4    |

| Total Jitter                                                                                                                                          | Тј                                 | 0.66UI (max)                    | CP0                   | 1, 2, 4    |

| Eye Height                                                                                                                                            |                                    | 100mV (min)                     | CP0                   | 1, 2, 3, 4 |

| Notes:                                                                                                                                                | 30.                                | .5                              |                       |            |

| <ol> <li>Measured over 10<sup>6</sup> consistent is calculated as 14.069</li> <li>Measured after received</li> <li>The eye height is to be</li> </ol> | times the RMS<br>er equalization f | random jitter for 1<br>unction. | 0 <sup>-12</sup> BER. |            |

| width $\pm 0.05$ UI).                                                                                                                                 |                                    | 1                               |                       | ,          |

| <ol> <li>All specified values in<br/>3.0 Specification. In<br/>supersede those contained</li> </ol>                                                   | case of conflict,                  |                                 |                       |            |

| 5. Optional measuremen                                                                                                                                | t for characteriza                 | ation and troublesh             | ooting purposes.      |            |

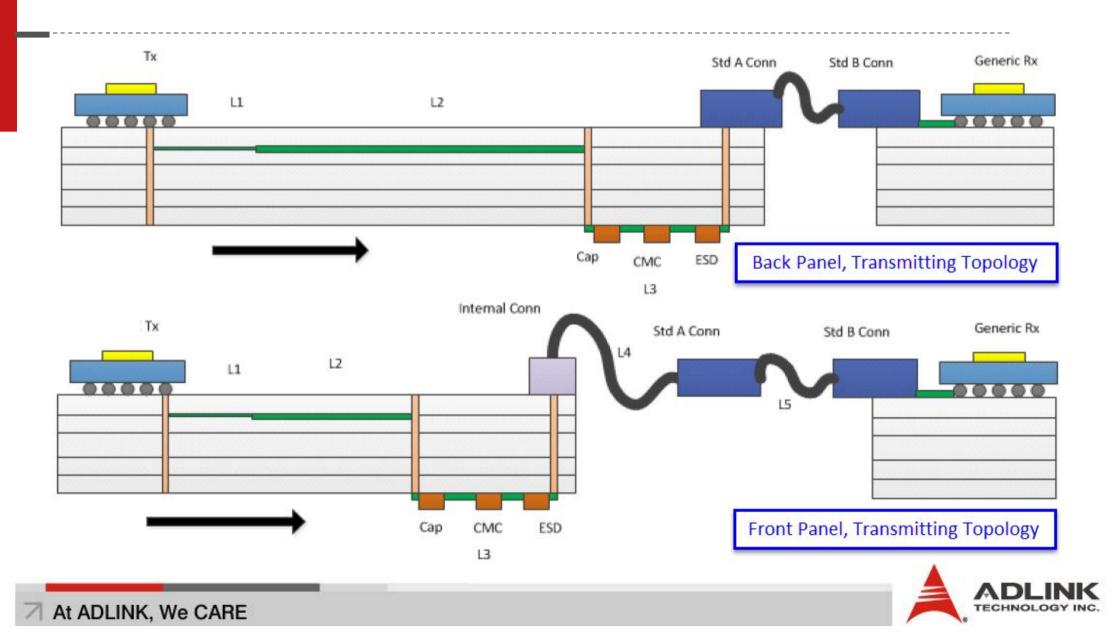

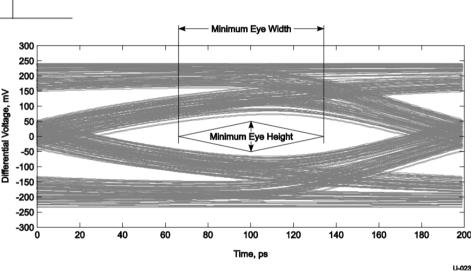

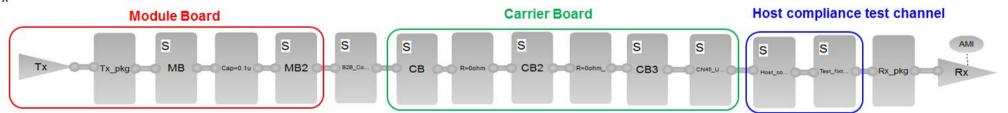

The "host compliance test channel" in Figure 6(a) is used to test compliance for host designs. The compliance channel includes a 3m length SuperSpeed cable (the maximum allowed by the spec) connected to a printed circuit board that has 5" of trace providing connection between a standard device connector and SMAs that then connect to a oscilloscope. The five inch trace length represents a maximum loss device design (PCB plus package).

USB 3.0 SuperSpeed Equalizer Design Guidelines

(a) Host compliance test channel

### Key specifications:

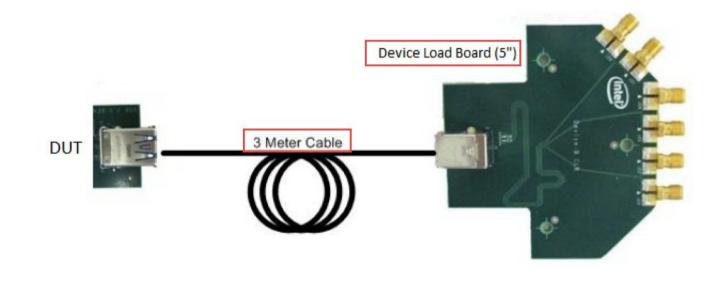

- Provides test point access for transmitter measurements

- Single-ended measurements as required by the USB 3.0 specification for transmitter and receiver validation and compliance testing

- Differential measurements using active probes allow probing of active bus transactions for debug and verification testing

- USB 3.0 power probing features for easy measurement of transient and steady state power states

Тур А

Typ B

**Upstream**

Hub

Тур В

#### Description:

The U7242A USB 3.0 test fixture will help simplify the USB 3.0 measurement process by providing access to the transmitter and receiver measurement points required for USB 3.0 compliance testing. It has been designed for direct SMA connections for easy and accurate measurements with direct connections to the oscilloscope and J-Bert SMA connections. It also includes probing connections for InfiniiMax active differential probes for the characterization and testing of active bus signaling of USB 3.0 and USB 2.0 traffic.

The U7242A USB 3.0 superspeed electrical test fixture provides signal accessibility and probing for USB 3.0 devices, host and hub upstream and downstream ports.

#### At ADLINK, We CARE

Host

Downstream

TVDA

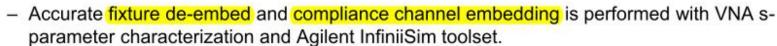

#### U7243A USB 3.0 TX Compliance Application

Use "KEYSIGHT\_ENA\_HOST\_CHANNEL\_3MCABLE.s4p" to express the "host compliance test channel".

#### 🚽 USB3\_TX\_Host\_Channel.tf4 🏼

At ADLINK, We CARE

4 5

- 6 ctDef.Transmitter.FileName='C:\Documents and Settings\Administrator\Desktop\USB30 U7242 SHORTCABLE FORHOST.s4p';

- 7 ansmitter.FileName='C:\Documents and Settings\Administrator\Desktop\USB30\DEVICE\_3MCABLE.s4p ;SimCktDef.Transmit

# Abstract

- Source of Signal Loss

- Pre-emphasis and Equalization

- USB 3.0 transmitter compliance test considerations

- USB 3.0 transmitter channel design case study

- Summary

| Sigrity BrdExtractor                             |                        |                |        |

|--------------------------------------------------|------------------------|----------------|--------|

| Settings<br>Translate MIXED Layer to:            | Plane or Signa         | 1              |        |

| Allow patches on Signal lay                      | iers                   |                |        |

| <ul> <li>Distinguish shapes of differ</li> </ul> |                        |                |        |

| Add pseudo plane(s) if lack                      |                        |                |        |

| Append net name to object                        |                        |                |        |

| Include elements with no n                       | et names               |                |        |

| Create Partial Ckt Names b                       | ased upon Compon       | ent Part Numbe | r      |

| Calculate via plating using                      | "Drill/Slot symbol" va | alues          |        |

| Split vias into several 2-lay                    | er vias                |                |        |

| Translate antipads as voids                      | 5                      |                |        |

| Translate only voltage net                       | 5                      |                |        |

| Treat pad on dielectric laye                     | er as drill            |                |        |

| Unionize traces shorter than:                    |                        | 0              | mm     |

| Maximum arc length replaced b                    | y line segment:        | 0.2            | mm     |

| Name affix :                                     |                        |                |        |

| Cadence Extracta Path:                           |                        |                |        |

| env File Path:                                   | 1.1.                   |                |        |

| C:\Cadence\SPB_16.6\share\                       | pcb\text\env           |                | Open   |

| extracta.exe Path:                               |                        |                |        |

| C: \Cadence \SPB_16.6 \tools \c                  | ocb\bin\extracta.ex    | e              | Open   |

|                                                  |                        | Sattings       | Cancel |

|                                                  | OK Restore             | Settings       | Cancer |

Via plating can also be translated if specified in the Allegro database "Drill / Slot symbol" information.

If non-functional pads will not be removed, select option "split vias into several 2-layer vias".

|                                |          | III.                   |                  |  |

|--------------------------------|----------|------------------------|------------------|--|

| <ul> <li>Enforce of</li> </ul> | ausality | View Material          | Import<br>Filter |  |

|                                | Auto :   | Set Layer Special Void |                  |  |

|                                | OK       | Cancel                 | Apply            |  |

| General                                     |               |

|---------------------------------------------|---------------|

| Keep shape enabled when the net is disabled |               |

| Gray Disabled                               | Hide Disabled |

| $\checkmark$ | EX1_DDR3_DQ<0>   | Eachie Sale at ad Nate      |

|--------------|------------------|-----------------------------|

| $\checkmark$ | EX1_DDR3_DQ<1>   | Enable Selected Nets        |

|              | EX1_DDR3_DQ<2>   | Disable Selected Nets       |

|              | EX1_DDR3_DQ<3>   | Enable All Nets             |

| $\square$    | EX1_DDR3_DQ <4>  | Disable All Nets            |

| $\checkmark$ | EX1_DDR3_DQ<5>   |                             |

| $\checkmark$ | EX1_DDR3_DQ<6>   | Edit Coupling Parameters    |

| $\square$    | EX1_DDR3_DQ<7>   | Delete Coupling Parameters  |

| $\checkmark$ | EX1_DDR3_DQS_N<0 | Set With Default Parameters |

|              | EX1_DDR3_DQS_P<0 | -                           |

| le                                      |                                                     |  |

|-----------------------------------------|-----------------------------------------------------|--|

| General<br>File Manager<br>Save Options | Schange the 'Network Parameters' options in PowerSI |  |

| Hotkeys                                 | Port Reference Impedance                            |  |

| ayout                                   |                                                     |  |

| Grid and Unit                           | Power Nets 1 Ohm                                    |  |

|                                         | Signal Nets 50 Ohm                                  |  |

| View<br>Processing<br>Trace             | Signal Nets 50 Ohm                                  |  |

| Starting Freq. | Ending Freq.      | Sweeping Mode | Freq. Increment |      |

|----------------|-------------------|---------------|-----------------|------|

| 0 Hz           | 10 GHz            | Adaptive      |                 |      |

|                |                   |               |                 |      |

|                |                   |               |                 |      |

|                |                   |               |                 |      |

|                |                   |               |                 |      |

| Customize Fr   | equency Ranges in | ACC, Defeult  | ОК              | Cano |

Calculate DC point as reference

**PowerDC Option**

| 2            | EX1_DDR3_DQ<0>                     | 5 | 200 |  |

|--------------|------------------------------------|---|-----|--|

| $\checkmark$ | EX1_DDR3_DQ<1>                     | 5 | 200 |  |

| 2            | EX1_DDR3_DQ<2>                     | 5 | 200 |  |

| 4            | EX1_DDR3_DQ<3>                     | 5 | 200 |  |

| ~            | EX1_DDR3_DQ<4>                     | 5 | 200 |  |

| ~            | EX1_DDR3_DQ<5>                     | 5 | 200 |  |

| 2            | EX1_DDR3_DQ<6>                     | 5 | 200 |  |

| $\checkmark$ | EX1_DDR3_DQ<7>                     | 5 | 200 |  |

| $\checkmark$ | EX1_DDR3_DQS_N<0>                  | 5 | 200 |  |

| 4            | <pre>EX1_DDR3_DQS_P&lt;0&gt;</pre> | 5 | 200 |  |

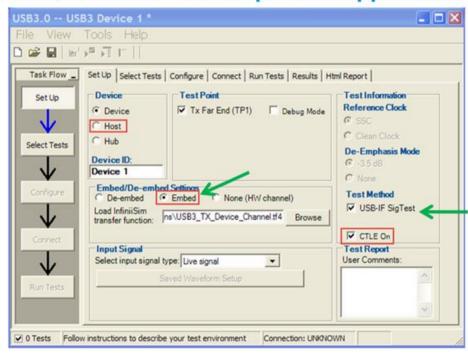

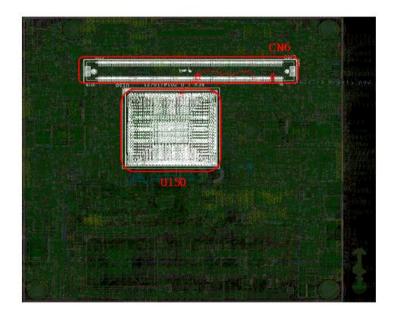

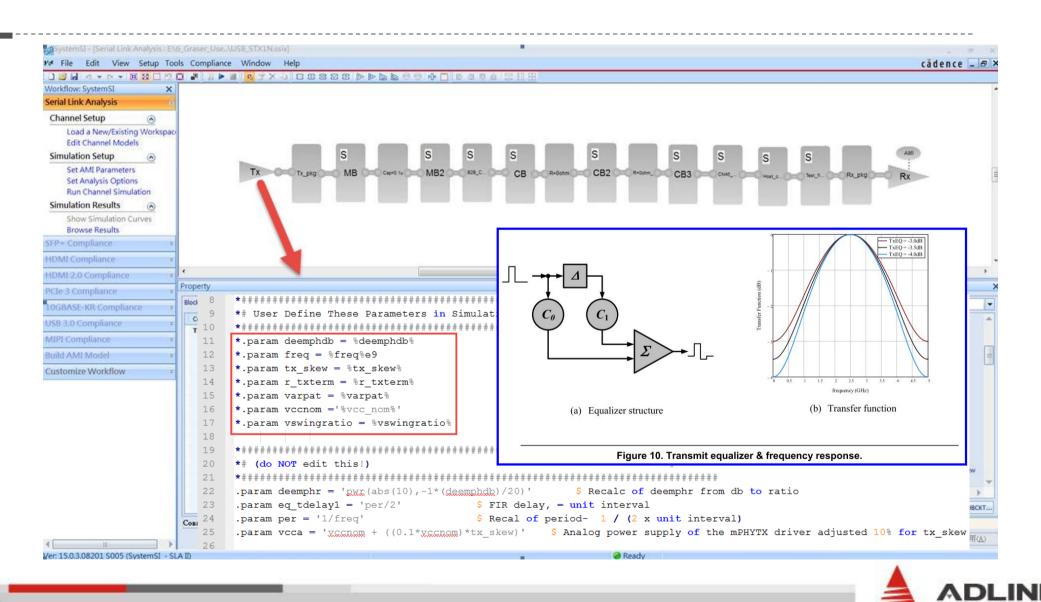

#### Routing (Module Board)

#### Routing (Carrier Board)

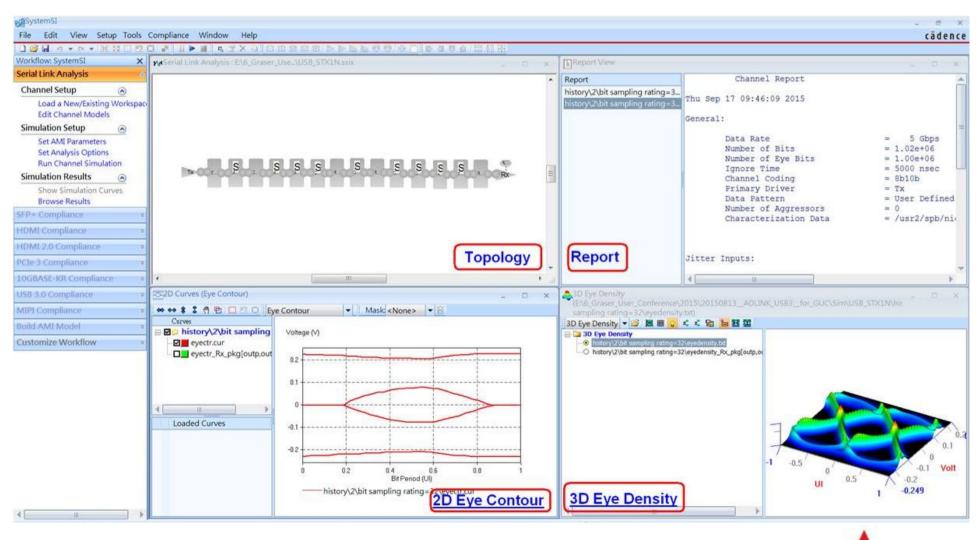

#### Topology

ΤХ

TECHNOLOGY

TECHNOLOGY

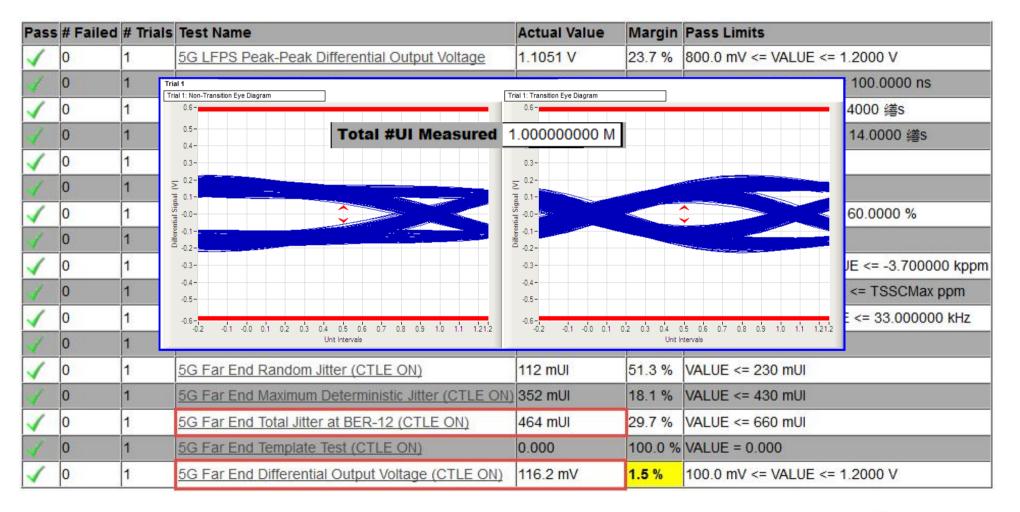

### USB 3.0 Report1

#### **USB 3.0 Compliance Report**

Generated by Cadence SystemSI, 13.0.2.01141 27<sup>th</sup> of January 2014

#### **Useful Links:**

Cadence website: <u>http://www.cadence.com</u>

USB 3.0 Specification: http://www.usb.org/developers/whitepapers/USB 3 0 e-Compliance methodology 0p5 whitepaper.pdf

|       |                         | Speed USB) Compliance Item *          | USB3 (Super | Vorkflowr. System SI 🛛 🗙 🛛                                                            |

|-------|-------------------------|---------------------------------------|-------------|---------------------------------------------------------------------------------------|

|       |                         |                                       |             | erial Link Analysis 🛛 🗧 🗧                                                             |

|       |                         | ose compliance iter                   | Choo        | FP+ Compliance ×                                                                      |

|       | Transition and a state  |                                       |             | IDMI Compliance ×                                                                     |

| 12    | Symbol                  | Parameter                             | No.         | Cle 3 Compliance ×                                                                    |

|       |                         | ht At test point 1 (TP1) (Table 6-12) | Eye Heig    | OGBASE-KR Compliance ×                                                                |

|       | Use CP0                 | Eye Height                            | 1           | ISB 3.0 Compliance                                                                    |

|       |                         | ential Swing (Table 6-12)             | Tx Differ   | Channel Setup 📀                                                                       |

|       | V <sub>TX-DIFF-PP</sub> | Tx Differential Swing                 | 2           | Choose a Template<br>Edit Channel Models                                              |

|       |                         | er (Table 6-12)                       | Total Jitt  | Set AMI Parameters                                                                    |

|       | Tj                      | Total Jitter                          | 3           | Simulation Setup  Choose Compliance Item                                              |

|       |                         | erance Test for Rx (Table 6-19)       | Jitter To   | Check Compliance                                                                      |

| 23    | Rx in BERT mode         | Stressed/Swept Jitter                 | 4           | Simulation Results 📀                                                                  |

|       |                         | • • • • • • • • • • • • • • • • • • • |             | Results Summary                                                                       |

| Cance | OK                      |                                       |             | Show Simulation Curves                                                                |

|       |                         |                                       | <u></u>     | View Compliance Curves                                                                |

|       |                         |                                       |             | ustomize Workflow 🛛 🗧                                                                 |

|       |                         | Stressed/Swept Jitter                 | 4           | Results Summary<br>Export Results<br>Show Simulation Curves<br>View Compliance Curves |

At ADLINK, We CARE

| Parameters | Symbol | Min | Max | Units | Simulation Results | Pass/Fai |

|------------|--------|-----|-----|-------|--------------------|----------|

|------------|--------|-----|-----|-------|--------------------|----------|

#### **Tx Differential Swing**

| Parameters            | Symbol                  | Min | Max | Units | Simulation Results | Pass/Fail |

|-----------------------|-------------------------|-----|-----|-------|--------------------|-----------|

| Tx Differential Swing | V <sub>TX-DIFF-PP</sub> | 0.8 | 1.2 | v     | 1.122              | Pass      |

#### **Total Jitter**

| Parameters   | Symbol | Min | Max  | Units | Simulation Results | Pass/Fail |

|--------------|--------|-----|------|-------|--------------------|-----------|

| Total Jitter | Tj     |     | 0.66 | UI    | 0.670              | Pass      |

#### Jitter Tolerance Test for Rx

| Parameters | Symbol | Min | Max | Units | Simulation Results | Pass/Fail |

|------------|--------|-----|-----|-------|--------------------|-----------|

# Abstract

- Source of Signal Loss

- Pre-emphasis and Equalization

- USB 3.0 transmitter compliance test considerations

- USB 3.0 transmitter channel design case study

- Summary

# Summary

1. Channel modeling, simulation and measurement can be critical to design success.

2. Using compliance kits in SystemSI automates the testing process.

3. We can use Non-IBIS model as the transmitter and receiver buffer model in SystemSI to conduct the large number of data bits simulation in a short time.

| Simulation VS. Measurement |                                                                                                                       |                                                                                |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Characteristic             | Simulation                                                                                                            | Measurement                                                                    |  |  |  |  |

| When to use                | Early on                                                                                                              | Near the end                                                                   |  |  |  |  |

| Requirements               | Simulation software                                                                                                   | Scope / VNA / prototype                                                        |  |  |  |  |

| Usage                      | <ol> <li>Understand system margins</li> <li>Making design tradeoffs</li> <li>Design verification</li> </ol>           | Prototype verification                                                         |  |  |  |  |

| Limitations                | <ol> <li>Everything must be modeled</li> <li>Not all effects can be included</li> </ol>                               | <ol> <li>Affects circuit performance</li> <li>Needs places to probe</li> </ol> |  |  |  |  |

| Advantages                 | <ol> <li>Fix problems before prototype</li> <li>Can probe anywhere</li> <li>No need for physical prototype</li> </ol> | <ol> <li>Includes most effects</li> <li>Close to reality</li> </ol>            |  |  |  |  |

## Thanks for your attention~