Addi / Mark 16 / Oct / 2015

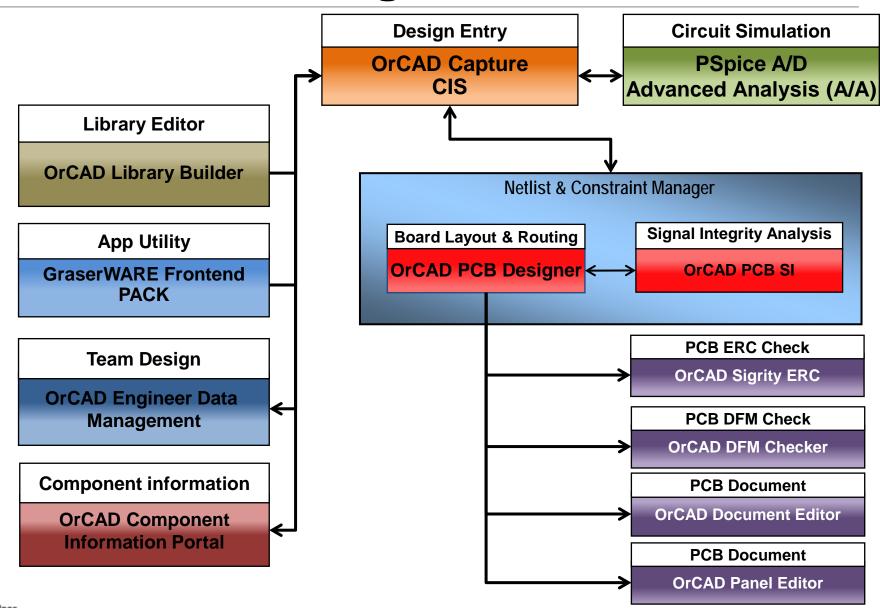

# OrCAD PCB Design Flow – Overview

# Topic

- OrCAD Capture / CIS What's New

- OrCAD Component Information Portal

- Circuit Design Challenges

# OrCAD Capture / CIS What's New

### OrCAD Capture / CIS What's New

#### Capture

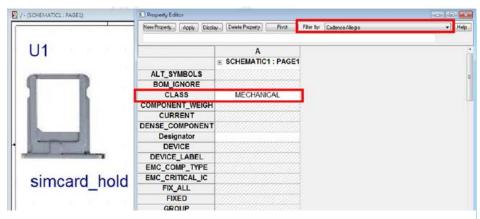

- View & Lite Mode Support

- Schematic Page Name in Title Block

- Mechanical Parts in Capture-Allegro Flow

- Part Properties Display

- Object Alignment in OrCAD Capture

- Object Distribution in OrCAD Capture

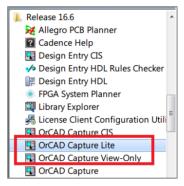

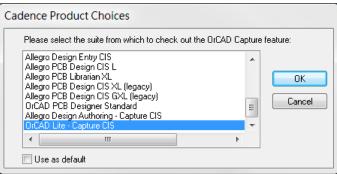

### **View & Lite Mode Support**

- Capture new version support starts at view or lite mode

- View mode : only preview schematic design

- Lite Mode: more functions can be used

- Search function

- Part / Net properties preview

- Full-featured operation under the limitations (Lite Mode only)

User Conference

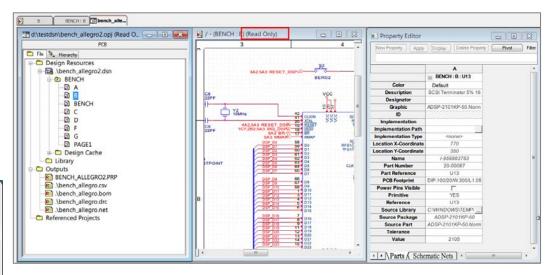

# Schematic Page Name in Title Block

Capture supports Schematic name and Page name on the title block property.

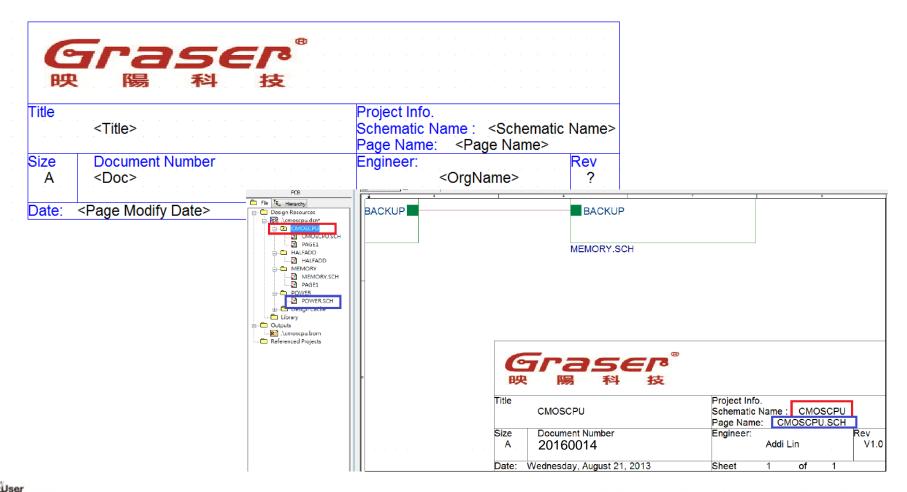

# Mechanical Parts in Capture-Allegro Flow

- Capture supports zero pin mechanical part, mechanical holes, and fiducials in Capture - Allegro flow.

- Parts should have the property of CLASS=MECHANICAL.

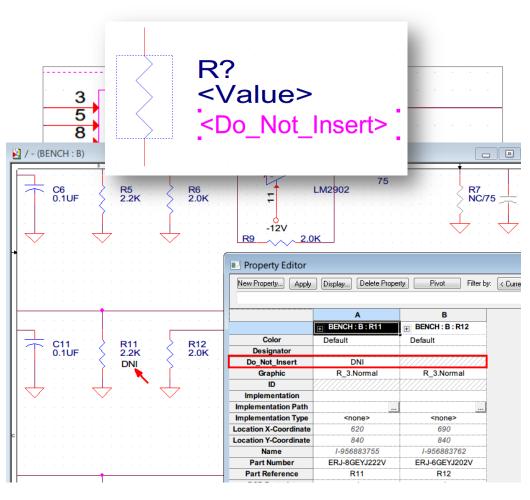

## **Part Properties Display**

New Display format in Display Properties dialog box

Value if Value Exists

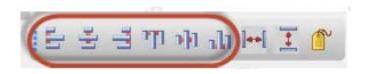

## **Object Alignment in Capture**

#### Alignment objects

- Vertically (Top, Middle, and Bottom)

- Horizontally (Left, Center, and Right)

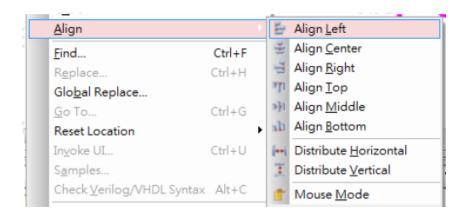

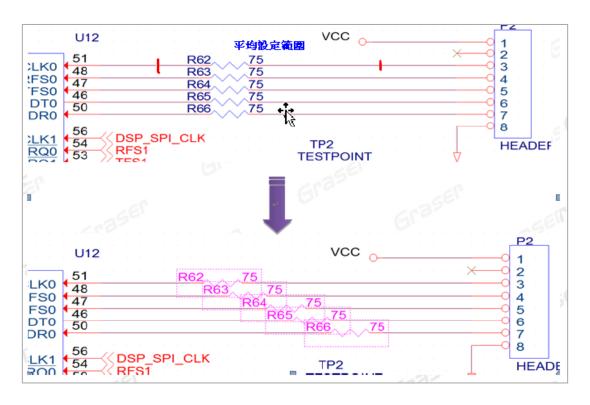

# **Object Distribution in Capture**

- Distribute objects

- Horizontally

- Vertically

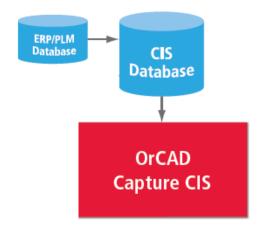

# OrCAD Component Information Portal

#### **Download Distributor Part Data**

- Distributor integrations enable access to parametric data for millions of parts

- Get costing and availability data along with electrical characteristics

- Easily define multiple sources for your parts to avoid supply issues

### Integrated in OrCAD Capture

CIP allows you to access and update component data without leaving Capture

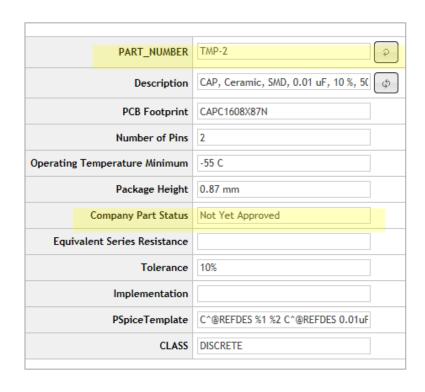

# **New Part Introduction (NPI) Flow**

- Add new parts in a controlled fashion

- CIP will flag the part and will send notifications to defined users who need to review and approve the part

- Engineers can use the part as a temp part in their design

- When the part is approved/rejected, part status will updated in engineers' view as well

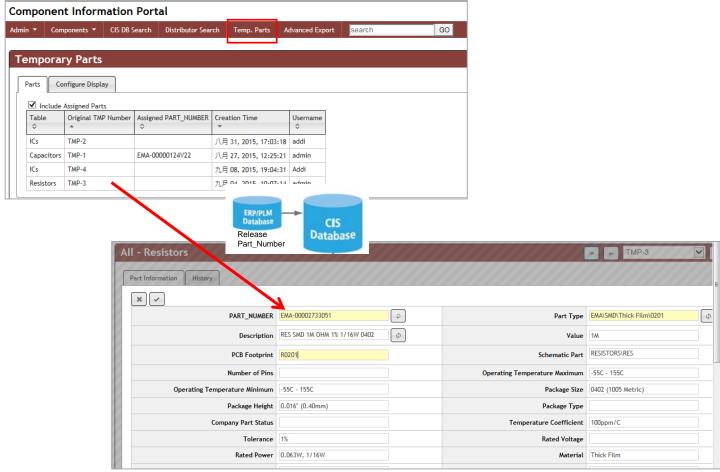

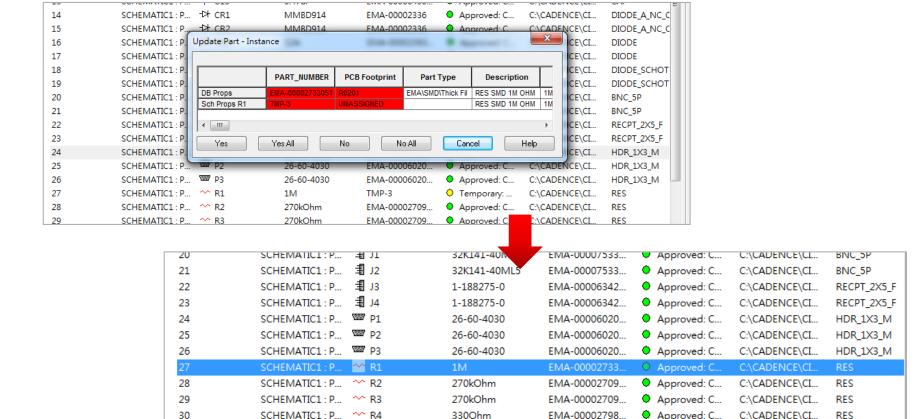

# **New Part Introduction (NPI) Flow**

Temporary Part Flow promoting concurrency

## **New Part Introduction (NPI) Flow**

Capture CIS updates part status to synchronize Part\_Number.

330Ohm

270hm

EMA-00002798...

EMA-00003252

31

32

SCHEMATIC1: P...

SCHEMATIC1: P... \* R6

C:\CADENCE\CI...

C:\CADENCE\CI...

RES

RES

Approved: C...

Approved: C...

# Circuit Design Challenges

# **Circuit Design Challenges**

#### How to Know

- Circuit design parts with library pin difference?

- Part status with database?

- Capacitor de-rating of net voltage?

#### OrCAD Tcl / Tk Utilities

- Part Library Check Utility

- Design Part Check Utility

- Capacitor De-rating Check Utility

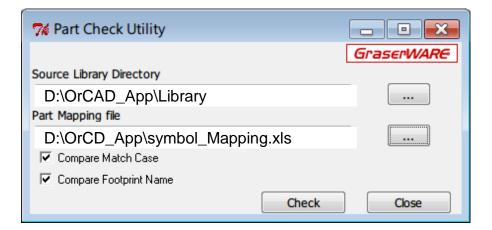

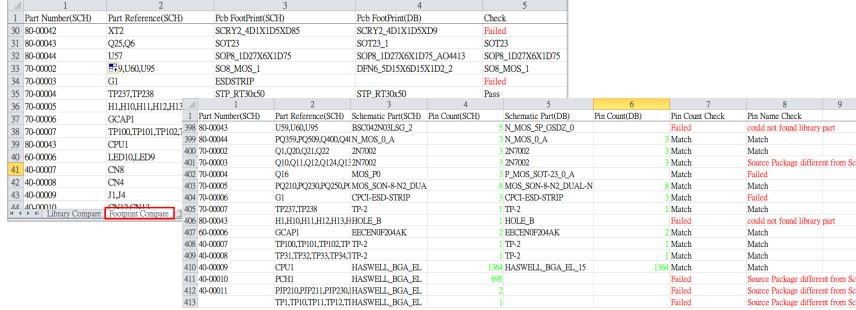

## **Part Library Check Utility**

- Schematic Symbol & Footprint Check With Library (Database)

- Library Symbol Pin Check

- Footprint Name Check

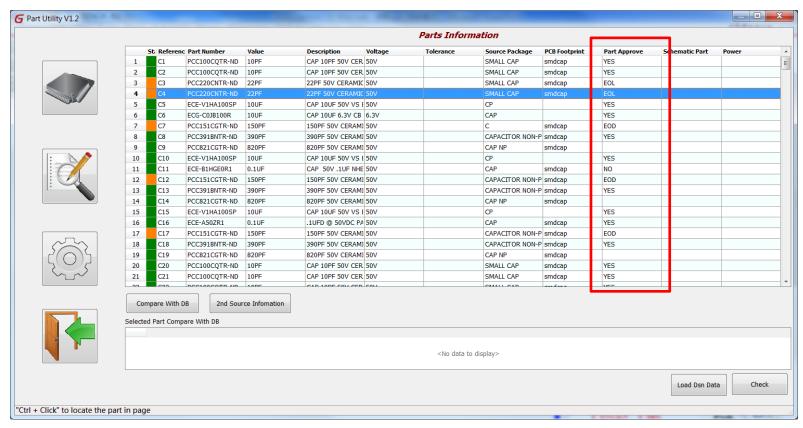

## **Design Part Check Utility**

- How to know Design Part

- Life cycle

- End of life

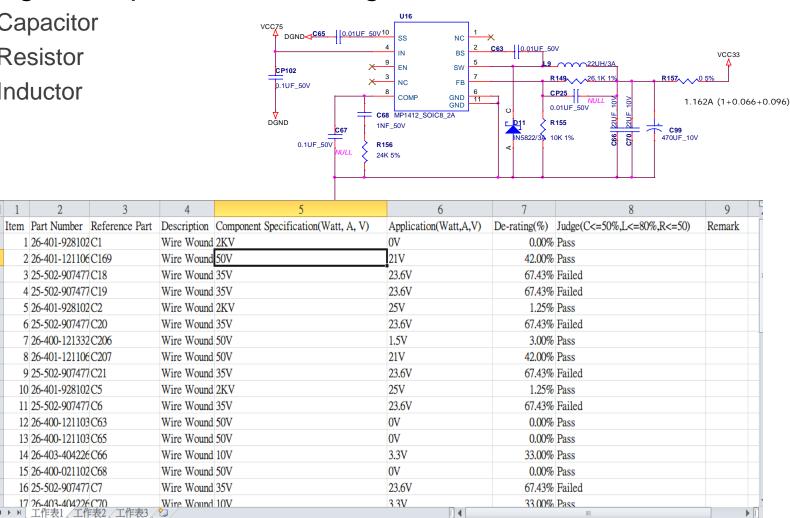

# Components De-rating Check Utility

#### Design Component De-Rating Check

- Capacitor

- Resistor

- Inductor

1 26-401-928102 C1

2 26-401-121106 C169

3 25-502-907477 C18

4 25-502-907477 C19

5 26-401-928102 C2

6 25-502-907477 C20

7 26-400-121332 C206

8 26-401-121106 C207

9 25-502-907477 C21

10 26-401-928102 C5

11 25-502-907477 C6 12 26-400-121103 C63

13 26-400-121103 C65

14 26-403-404226 C66

15 26-400-021102 C68

16 25-502-907477 C7

18 17 26-403-404226 C70 工作表1 工作表2

# Circuit Simulation Requirement & PSpice Simulation Solution

# Circuit Simulation Requirement & PSpice Simulation Solution

#### Why PSpice

The Circuit Design Verification Challenge

#### PSpice Solution

- Cadence OrCAD Design Solution Integration

- Mixed-Signal, Mixed Language and Mixed Domain Integrative Simulator

- PSpice Modeling Application

- Quality & Speed Performance

# Why PSpice

# The Circuit Design Verification Challenge

#### Design Trends

- Miniaturization

- Complexity

- Visualization Interfaces

- Interconnected Systems

# The Circuit Design Verification Challenge

Design Verification Challenges

Power Management

- Embedded Software

- Digital Control Systems

- Mixed Signal Designs

- Use red when emphasizing words

- High Speed & Performance

- Quality

What's EDA TOOL supporting it?

# **PSpice Solution**

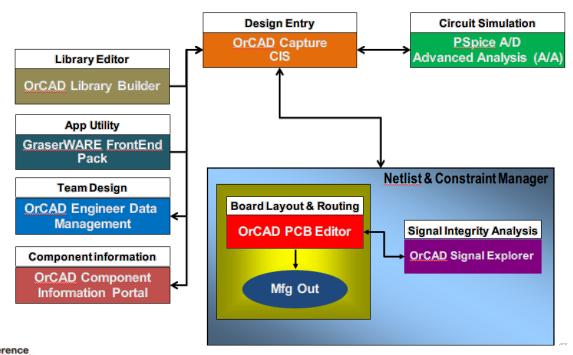

# Cadence OrCAD Design Solution Integration

- Powerful and Widely Used Design Solution

- Fast and intuitive schematic design entry, OrCAD Capture

- Powerful component data management, OrCAD Capture CIS

- Full-featured Mixed-Mode simulator, PSpice

- Comprehensive PCB solution, OrCAD PCB Designer

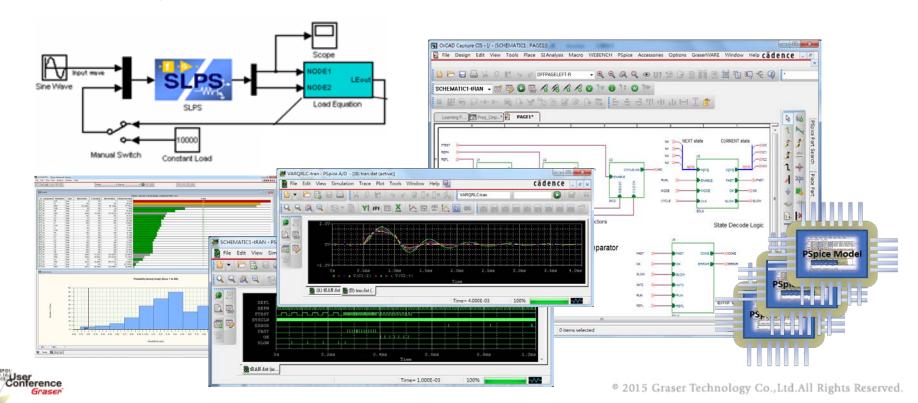

# Mixed-Signal, Mixed Language and Mixed Domain Integrative Simulator

#### PSpice

- Integrates seamlessly with OrCAD Capture/ OrCAD Capture CIS

- Fast, accurate analysis of analog and mixed-signal designs

- Advanced analysis to increase performance and productive yield

- Numerous PSpice model libraries

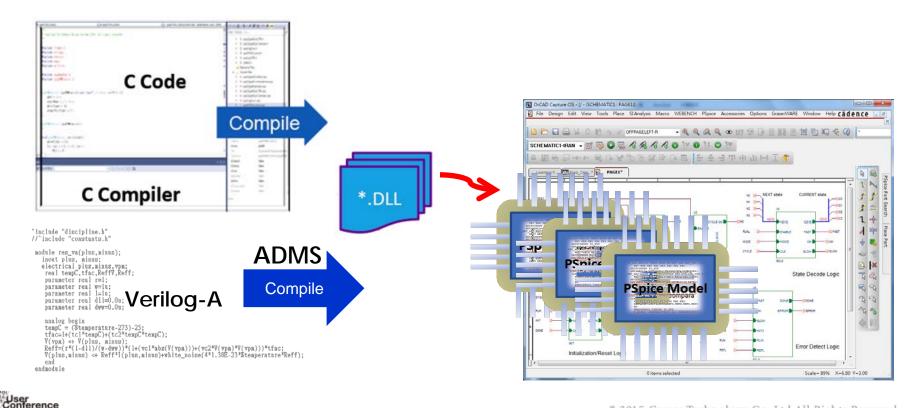

- Supports C/C++, SystemC and Verilog-A

# Mixed-Signal, Mixed Language and Mixed Domain Integrative Simulator

- PSpice Mixed Language Circuit Simulation

- Hardware/Software Co-Simulation

- Supports C/C++, SystemC and Verilog-A

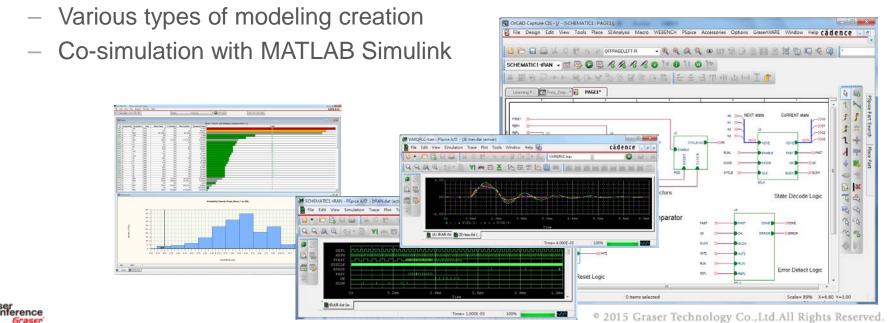

# Mixed-Signal, Mixed Language and Mixed Domain Integrative Simulator

- PSpice Mixed Domain Integration

- Systems Simulation

- Integration with MATLAB Simulink brings two industry-leading simulation tools, electromechanical & electrical systems in a co-simulation environment.

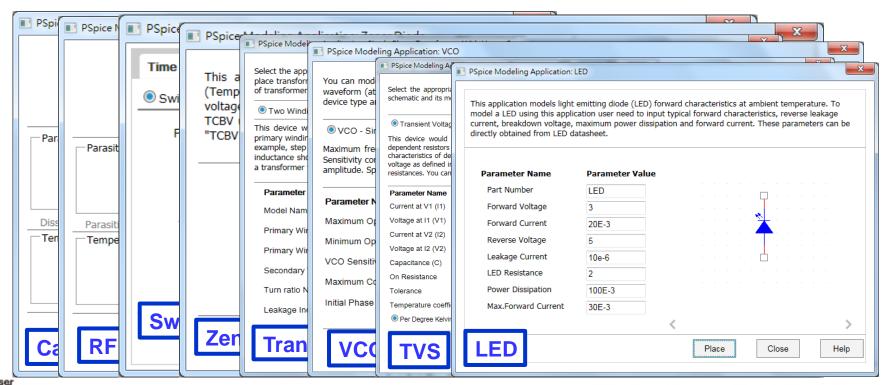

- Quick & Easy methods to create and edit PSpice models

- No Library Setup required in OrCAD Capture/Capture CIS schematic

- Using parametric extraction algorithms

- Edit existing PSpice instance properties

- Device Type, Capacitor/Inductor/Transformer/Zener/Switch/TVS/VCO/LED

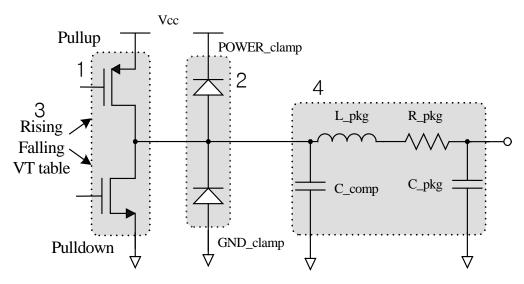

- PSpice Sub-circuit Generation from IBIS Models

- New IBIS Import supports for V-I curves and V-T curves.

- PSpice existing model library models

- Offers more than 30,000 analog and mixed-signal models.

- PSpice library includes parameterized models such as BJTs, JFETs,

MOSFETs, IGBTs, SCRs, discretes, operational amplifiers, optocouplers,

regulators, PWM controllers, and multipliers.

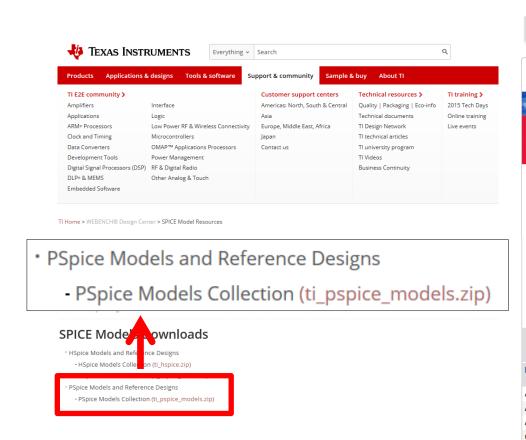

Get PSpice Models from device vendors / manufacturers

#### OrCAD Capture Marketplace

#### PSpice modeling service company Milliage

- Supply every PSpice model

- Passive components, capacitor, inductor, resister, transformer, connector, cable, FPC Line, and so on.

#### Power MOSFET Model Comparison Modech SPICE Model MODECH Model Datasheet Free Model Modeling experts of MoDeCH provide customers with our unique SPICE r assistance for extraction, selection of an optimum device model, parame customers' needs. Moreover, to improve simulation accuracy at most, we offers highest accuracy SPICE parameters suitable for the customers' ne SPICE model Drain to Source Voltage **On-wafer Devices** We provide a customized 1E+1 comprehensive solution for on wafer device modeling from TEG design assistance, on wafer measurement, optimal vg [E+0] model selection to accurate MODECH Model device parameter extraction. Datasheet Free Model

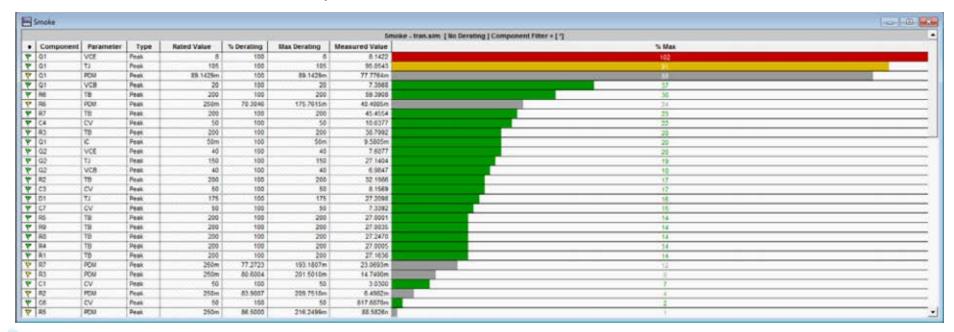

## **PSpice Advanced Analysis**

- Increase design performance, yield, and reliability

- Sensitivity identifies critical circuit components.

- Optimizer optimizes key circuit components.

- Parametric Plotter examines solution space through nested sweeps.

- Monte Carlo analyzes statistical circuit behavior and yield .

- Smoke detects component stress.

## **PSpice Summary**

#### Powerful and Widely Used Simulator

- Integrates seamlessly with Cadence OrCAD Design Solution.

- Full-featured mixed-Mode simulator

- Extensive OrCAD PSpice model libraries & various types of modeling creation.

- Be aware of pre-layout design risk & improve design performance, yield, and reliability.

### **PSpice Hands-On Workshop**

- PSpice Hands-on Workshop

- Date, 20/Nov/2015

#### **Full-featured Mixed-Mode PSpice simulation**