# Cadence/Sigrity Stage 2 Single-Stop SI/PI Solution for Chip-Package-Board

**An-Yu Kuo, PhD,** Engineering Group Director, Sigrity R&D US CDNLive August 2014

cādence<sup>®</sup>

# Agenda

- Leading-edge analysis technology integrated with Allegro

- Industry-renowned workflow

- Complete SI/PI/EMI solutions

- ✓ Hybrid solver

- 3D EM field solver

- 3D thermal solver

- ✓ 3D adaptive meshing

- Impulse response generator

- ✓ Fast channel simulation

- Parallel computing

- Transistor-to-behavior model generator

- S-parameter  $\rightarrow$  SPICE macro model

- Multi-physics simulation

- Thermal-RC extraction

....

# cādence®

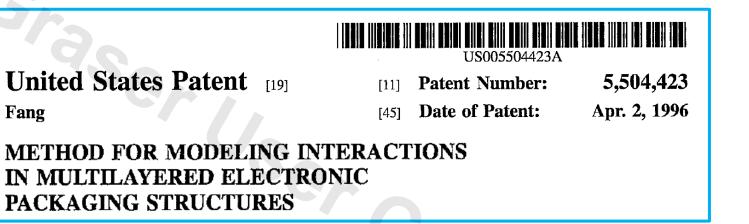

## Leading-edge analysis technology integrated with Allegro Hybrid solver

- The patented mode decomposition algorithm allows users to solve large package and board designs with good accuracy and performance

- Good for both time- and frequency- domain simulations

# cādence<sup>®</sup>

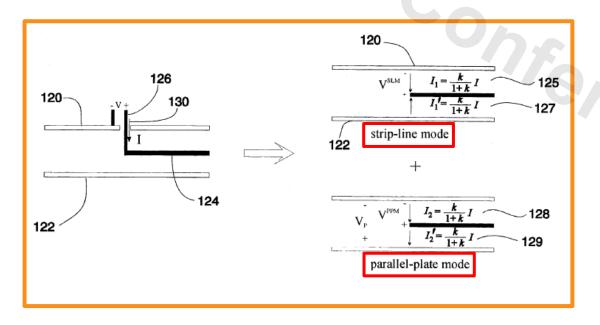

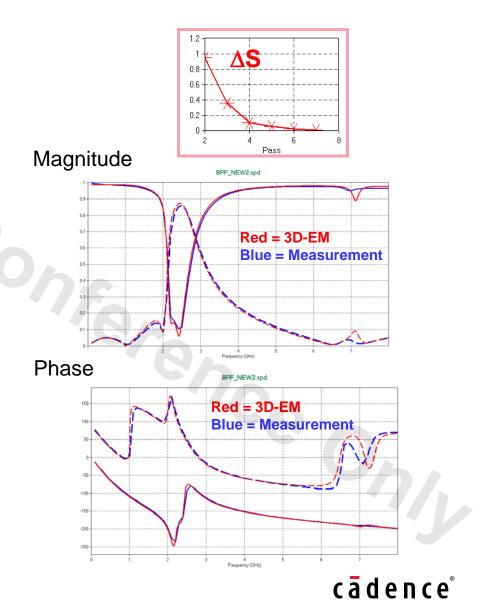

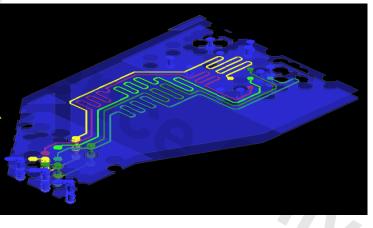

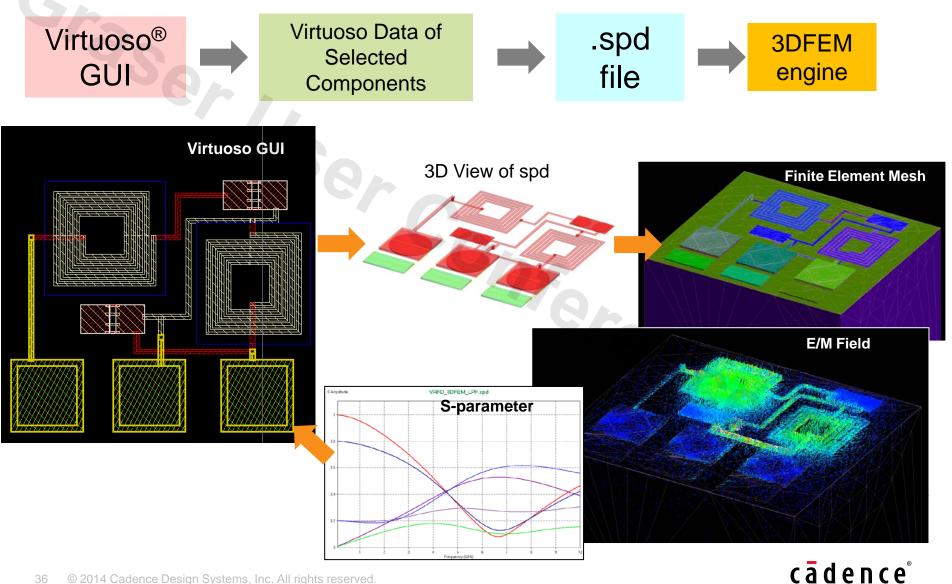

## Leading-edge analysis technology integrated with Allegro 3D EM field solvers

- Explicit FEM solvers for FW, QS, and S for different application needs

- Low-frequency stabilizer in FW engine

- Latest Krylov model order reduction for fast and accurate frequency sweep

- Super memory-efficient matrix solver

- Latest multi-grid technologies to handle huge models

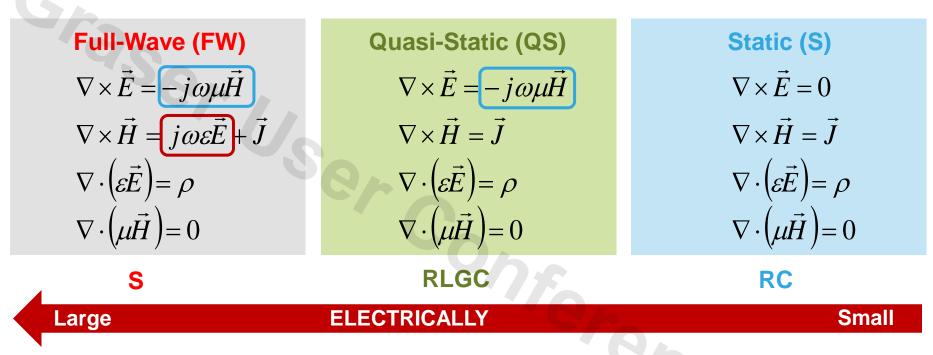

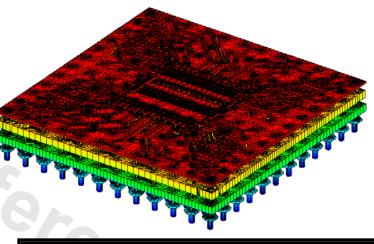

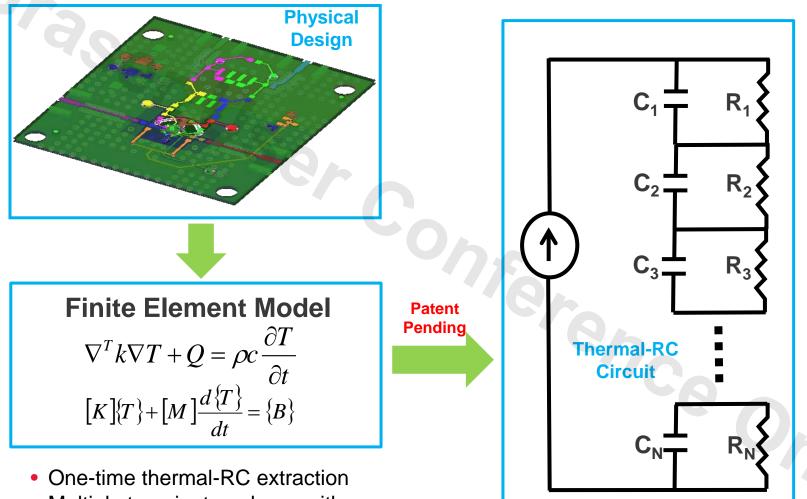

## Leading-edge analysis technology integrated with Allegro 3D thermal solver

$$\frac{\partial}{\partial x} \left( k_x \frac{\partial T}{\partial x} \right) + \frac{\partial}{\partial y} \left( k_y \frac{\partial T}{\partial y} \right) + \frac{\partial}{\partial z} \left( k_z \frac{\partial T}{\partial z} \right) + Q = \rho c \frac{\partial T}{\partial t}$$

- Steady-state and transient heat conduction with convection and radiation BCs

- Finite element method with adaptive meshing, model order reduction, and multi-grid method solver

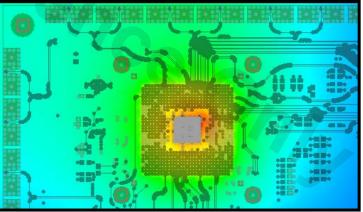

### Leading-edge analysis technology integrated with Allegro 3D adaptive meshing for consistent accuracy

**RFIC Band Pass Filter 2** spiral inductors 13 mim caps

- Refine mesh based on solutions from previous mesh

- Elements with higher solution errors are refined

- Used in EM and thermal solvers

# Leading-edge analysis technology integrated with Allegro

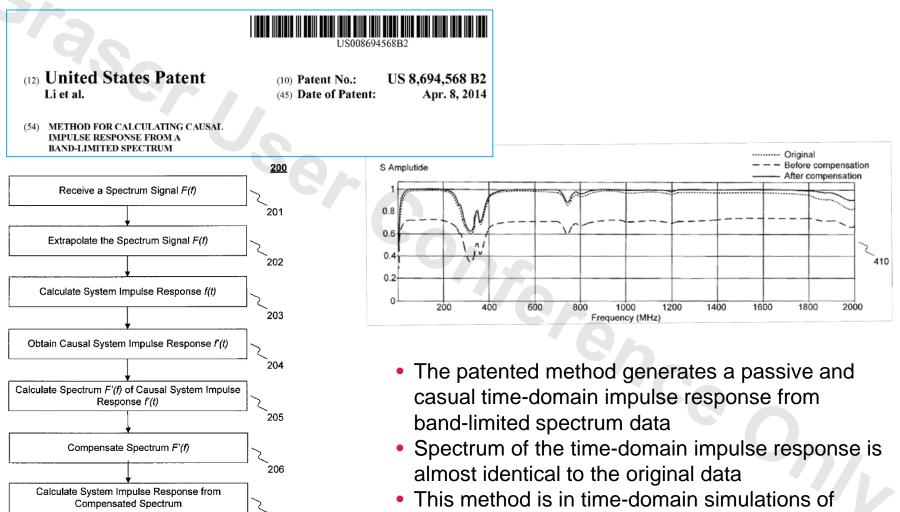

Patented impulse response generation

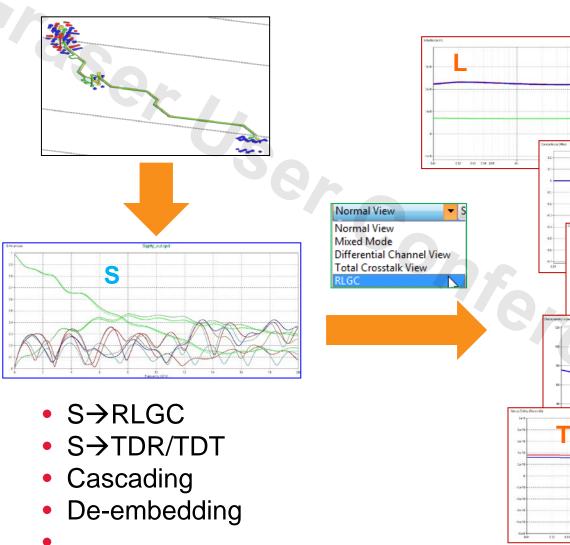

S-parameters in Sigrity<sup>®</sup> tools

# cādence°

207

### Leading-edge analysis technology integrated with Allegro East channel simulation for DDR4

- Ability to run millions of bits

- Jitter and noise injection

- AMI modeling for adaptive equalization

- Bathtub curve and eye generation

- DQ mask and BER measurement and report

4.2.2 Worst Case Summary

| Measurement             | Vcent_DQ<br>(V) | DQ<br>Compliance<br>Mask | Min<br>Jitter_margin<br>(ps) | Min<br>Noise_margin<br>(mv) | Max<br>tDQ\$2DQ<br>(ps) | Max <br>tDQS2DQ_BC<br>(ps) | Max<br>tDQ2DQ<br>(ps) | Min<br>VIHL_AC<br>(mV) | Min<br>TdIPW<br>(ps) | Min<br>SlewRate_Mask<br>(V/ns) | Max<br>SlewRate_Mask<br>(V/ns) | Min<br>SlewRate_AC_Swing<br>(V/ns) | Max<br>SlewRate_AC_Swing<br>(V/ns) |

|-------------------------|-----------------|--------------------------|------------------------------|-----------------------------|-------------------------|----------------------------|-----------------------|------------------------|----------------------|--------------------------------|--------------------------------|------------------------------------|------------------------------------|

| Worst Value             |                 |                          | 134.923                      | 166.916                     | -33.1392                | 6.60106                    | 13.2021               | <mark>469.832</mark>   | 396.02               | 3.20676                        | 4.32314                        | 3.05877                            | 4.2416                             |

| Rx Signal<br>(Waveform) |                 |                          | DQ6                          | DQ4                         | <u>DQ7</u>              | DQ3                        | <u>All Signals</u>    | <u>DQ4</u>             | DQ6                  | DQ6                            | DQ4                            | DQ6                                | DQ4                                |

# cādence<sup>®</sup>

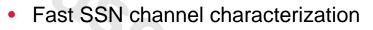

## Leading-edge analysis technology integrated with Allegro Parallel computing

Master Thread

# Leading-edge analysis technology integrated with Allegro

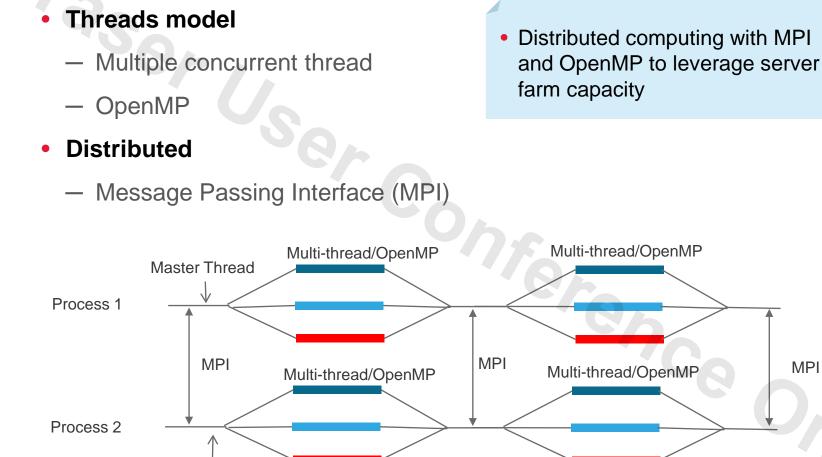

Transistor models  $\rightarrow$  behavior model

- Industry's most advanced tool for converting transistor models to power-aware IBIS

- Convenient GUI verifies conversion accuracy

- Simulation speed-up makes full bus simulations practical; this would otherwise take weeks

- Optional IBIS plus model provides additional level of accuracy

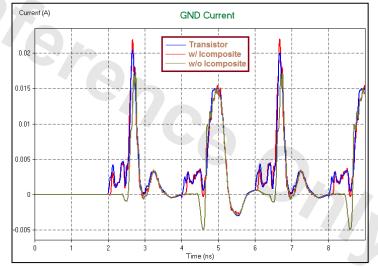

# Built-in simulation check compares transistor to IBIS

Impact of pre-driver current

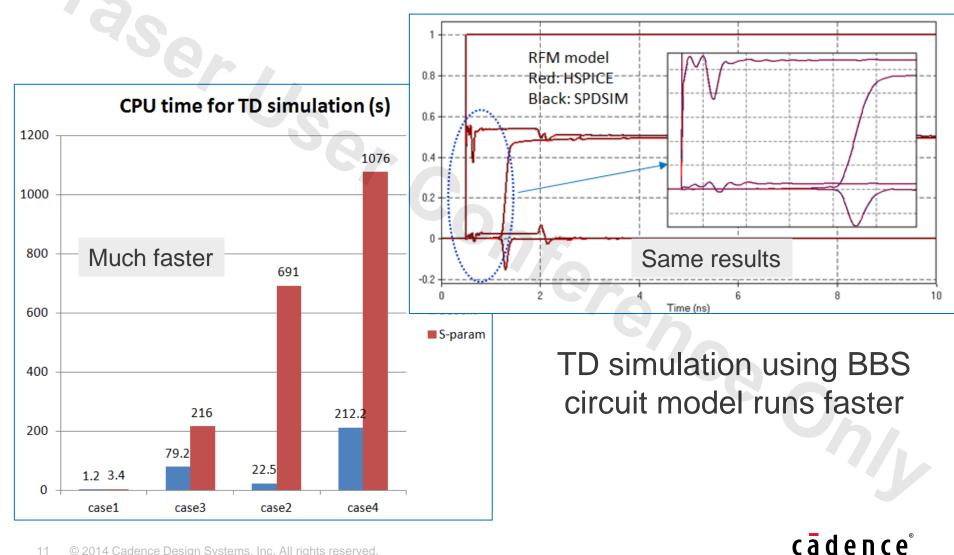

# Leading-edge analysis technology integrated with Allegro S-parameter → SPICE macro model

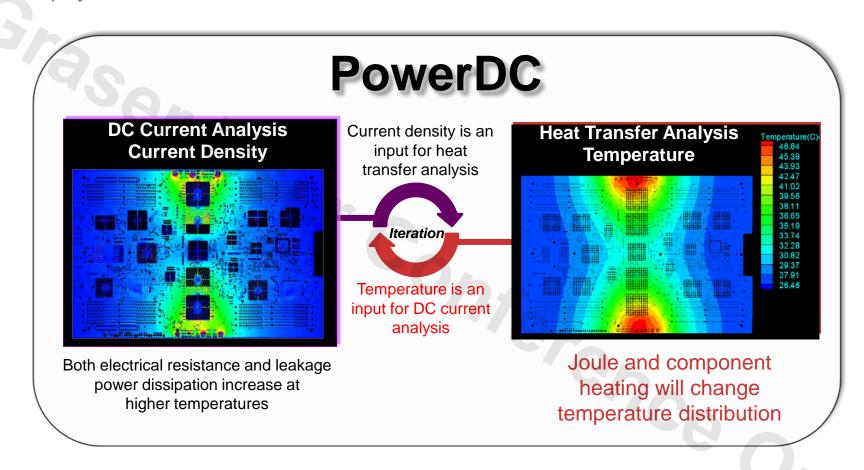

### Leading-edge analysis technology integrated with Allegro Multi-physics simulations

The first integrated and automated electrical/thermal co-simulation tool to help designers meet the new design challenge

## cādence<sup>®</sup>

## Leading-edge analysis technology integrated with Allegro Thermal-RC extraction

Multiple transient analyses with a circuit simulator

# Agenda

Leading-edge analysis technology integrated with Allegro

Industry-renowned workflow

Complete SI/PI/EMI solutions

- Industry-leading workflows

- Direct interface with Allegro®/APD/SiP

- Many useful model setup wizards

- Many SI/PI utilities

- Automated signoff report generation

...

# cādence<sup>®</sup>

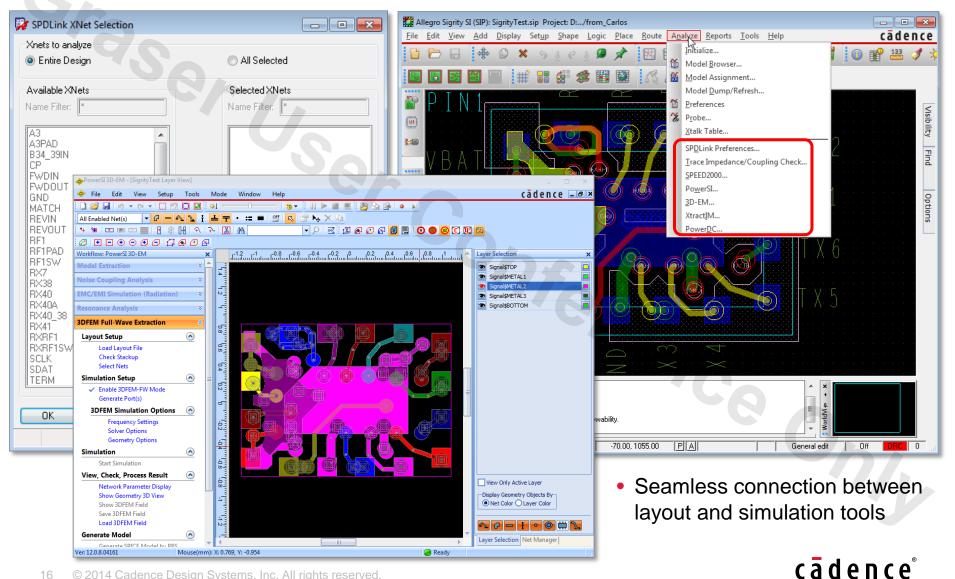

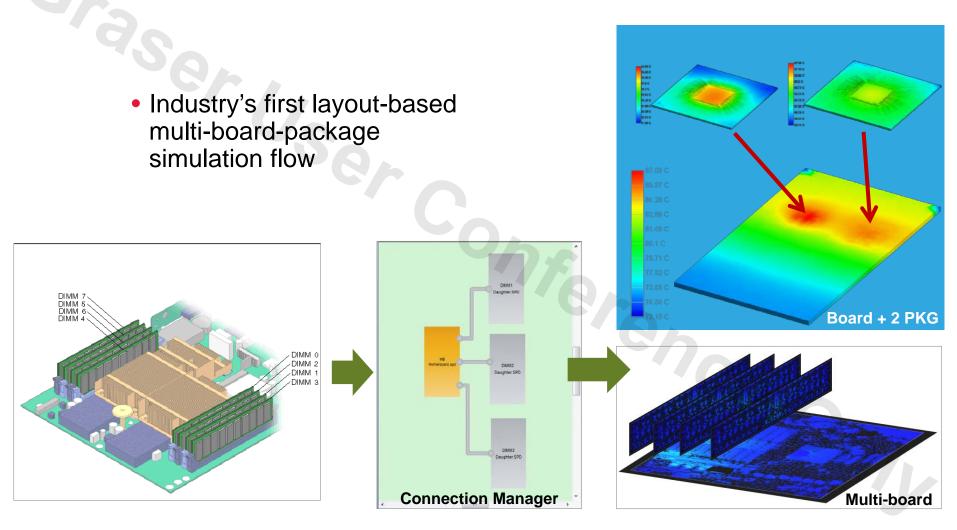

# Meticulous implementation Industry-leading workflows

| Multi-Board/Package E/T Co-Simulation                                                                   |                         |

|---------------------------------------------------------------------------------------------------------|-------------------------|

| Workspace                                                                                               | $\bigcirc$              |

| Create New Multi-Board/Package Works                                                                    |                         |

| Load Existing Multi-Board/Package Wor<br>Simulation Mode                                                | kspace                  |

| Enable E/T Co-Simulation Mode                                                                           |                         |

| Layout Blocks                                                                                           |                         |

| Add a Block on Schematic View<br>Select a Block on Schematic View<br>Attach a Layout for Selected Block |                         |

| Initial Setup for Loaded Block                                                                          | $\bigcirc$              |

| Analysis Setup for Loaded Block                                                                         |                         |

| Electrical                                                                                              | $\bigcirc$              |

| Thermal                                                                                                 | $\bigcirc$              |

| Constraints Setup for Loaded Block                                                                      | $\overline{\mathbf{v}}$ |

| Save Setup for Loaded Block                                                                             | $\overline{\mathbf{v}}$ |

| Connections between Blocks                                                                              |                         |

| Select two Blocks on Schematic View<br>Add a Connection                                                 |                         |

| Simulation                                                                                              | $\bigcirc$              |

| Results and Report                                                                                      | $\overline{\mathbf{v}}$ |

| Workflow: PowerSI                                                     | x           |

|-----------------------------------------------------------------------|-------------|

| Model Extraction                                                      | ×           |

| Noise Coupling Analysis                                               | ×           |

| EMC/EMI Simulation (Radiation)                                        | ×           |

| Resonance Analysis                                                    | ×           |

| 3DFEM Full-Wave Extraction                                            | ۵           |

| Layout Setup                                                          | <u>&gt;</u> |

| Load Layout File<br>Check Stackup<br>Select Nets                      |             |

| Simulation Setup                                                      | •           |

| <ul> <li>Enable 3DFEM-FW Mode<br/>Generate Port(s)</li> </ul>         |             |

| 3DFEM Simulation Options                                              | •           |

| Frequency Setting<br>Solver Option<br>Mesh Control<br>Solver Solution |             |

| Simulation                                                            | <u>&gt;</u> |

| Start Simulation                                                      |             |

| View Result                                                           | <u>&gt;</u> |

| Network Parameter Display<br>Show Geometry 3D View                    |             |

| Generate Model (                                                      | <u>&gt;</u> |

| Generate SPICE Model by BBS                                           |             |

| Customize Workflow                                                    | X           |

Various applicationspecific workflows for easy learning and usage

# **Meticulous implementation** Direct interface with Allegro/APD/SiP

© 2014 Cadence Design Systems, Inc. All rights reserved.

# Meticulous implementation Many useful model setup wizards

- Port wizard for automated port setup

- Wizard for PCB fiber weaving and RFIC deeptrenched isolation patterns

- Sweeping manager for parametric sweep

- Automated model cutting by polygon

- Cut-stitch wizard for long signal lines

- VRM setup wizard

- ..

# Meticulous implementation Many useful SI/PI utilities

R G Td 030 1.14 8.05 63 2+ 85 35 6

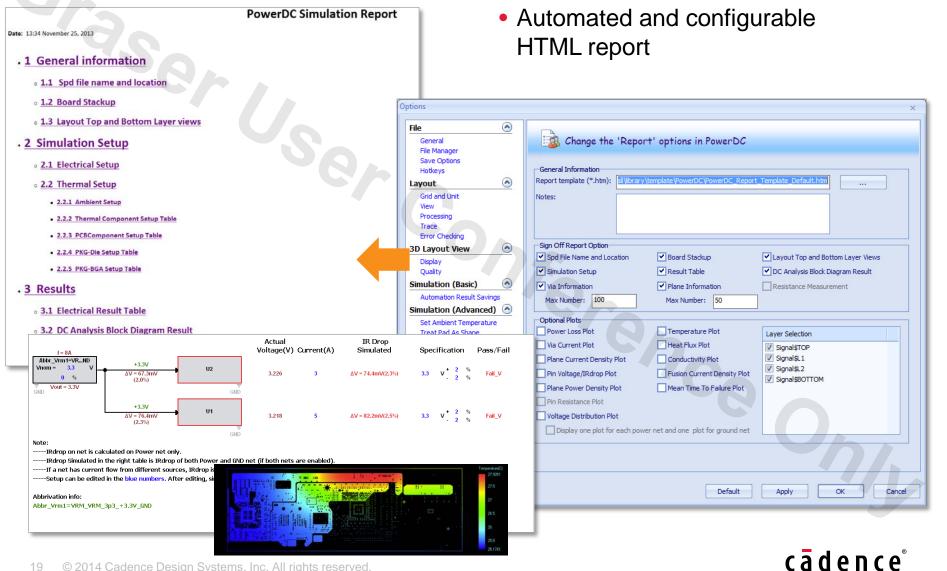

# Meticulous implementation Signoff report generation

© 2014 Cadence Design Systems, Inc. All rights reserved.

# Agenda

- Leading-edge analysis technology integrated with Allegro

- Industry-renowned workflow

- Complete SI/PI/EMI solutions

- Layout checks

- Model-based high-speed bus simulation

- Layout-based time-domain simulation

- Layout-based frequency-domain simulation

- Decap placement optimization

- High-speed bus simulation

- Multi-board-package simulation

- IOSSO

$\checkmark$

- Chip-pkg-board co-simulation

- **EMI/EMC** simulation

- Electrical/thermal co-simulation

- Package thermal parameters extraction

- RFIC passive component extraction

- ✓ Different levels for different needs

# Cover broad SI/PI/EMI needs

- Layout PDN design DC/AC check

- DC check

- AC check

- Layout SI check

- Geometry-based physical check

- Simulation-based electrical check

### PDN simulation

- DC simulation and signoff

- Electrical/thermal co-simulation

- AC frequency domain simulation and optimization

- Chip/PKG/PCB co-simulation

### Power-aware SI simulations

- High-speed serial link simulation

- Parallel bus simulation

- Chip/PKG/board IOSSO co-simulation

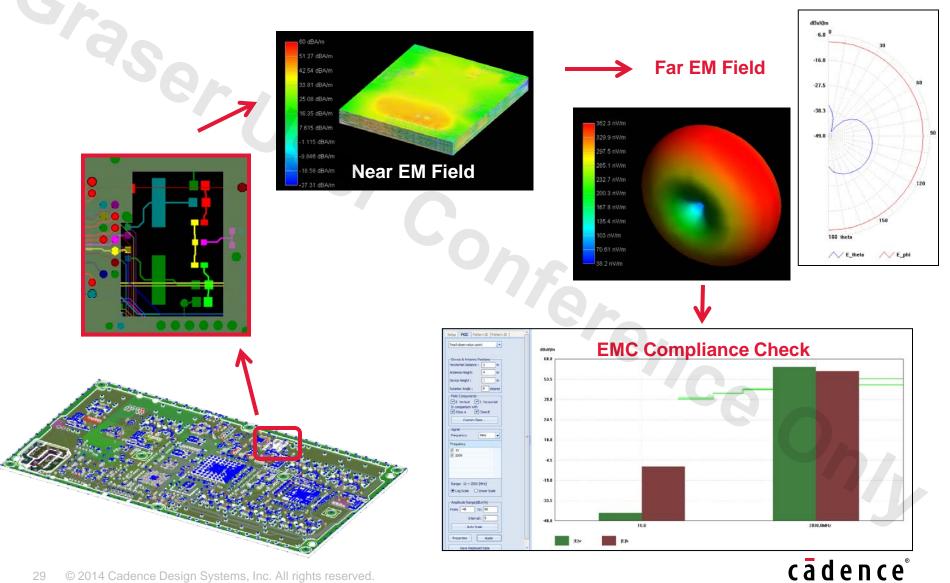

- EMI simulation

- Conductive EMI

- Radiative EMI

- EMC compliance check

- SI/PI/TI modeling

- RFIC passive component extraction

- Package thermal parameters extraction

- Electrical/thermal

- IBIS

# cādence<sup>®</sup>

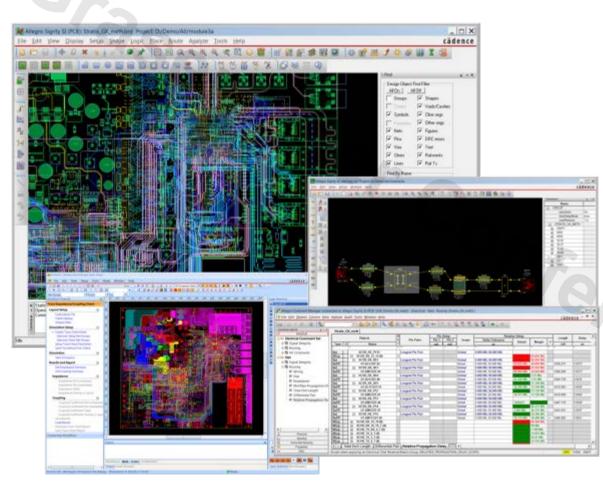

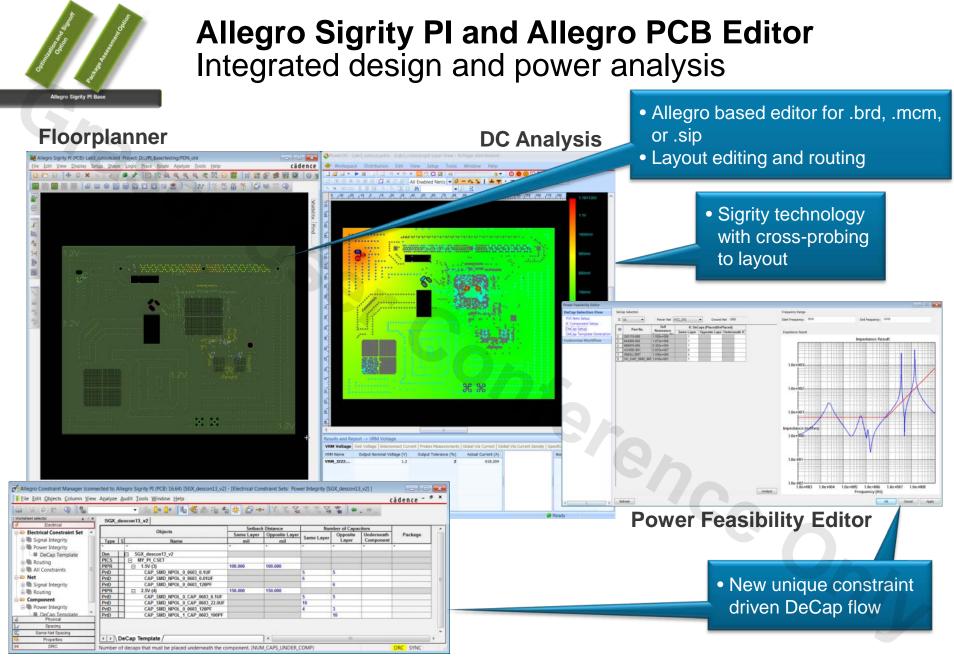

# Allegro Sigrity SI and Allegro PCB Editor Integrated high-speed design and analysis

#### Allegro Sigrity SI

No manual translation is required to analyze selected signals from the physical board or extract them into the SigXplorer module. Analysis results are reported in the same constraint manager used by Allegro PCB Editor. Coupled differential pairs and nets extended through discrete components (x-nets) are automatically identified, analyzed, and/or extracted.

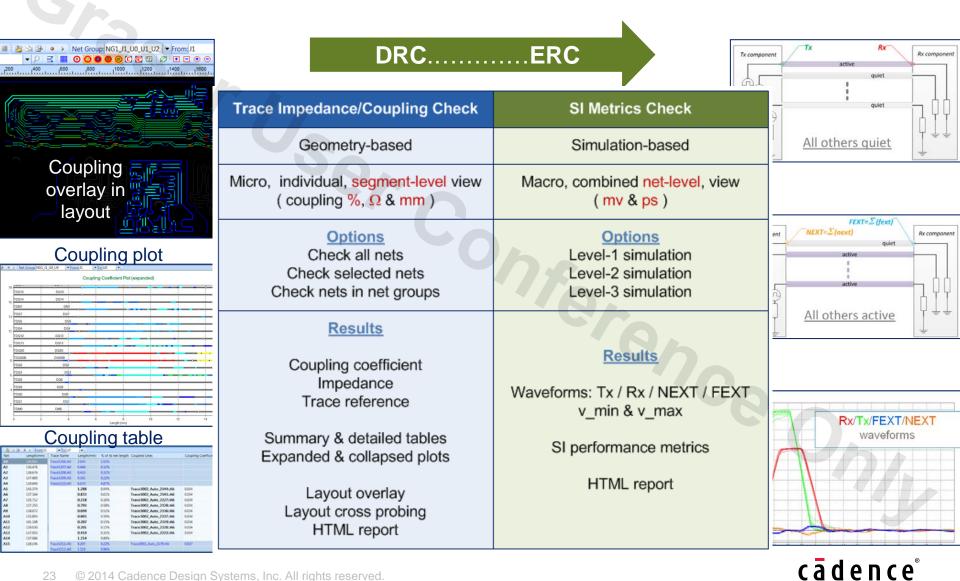

# Complete solutions

Geometry-based and simulation-based layout checks

#### 23 © 2014 Cadence Design Systems, Inc. All rights reserved.

# Complete solutions Layout-based time-domain SI/PI simulation

- SPEED2000<sup>™</sup> is industry's only layout-based time-domain SI/PI tool

- Five major workflows available for SI/PI analysis at level-1 to level-3

| <u>Workflow 1</u><br>General SI<br>Simulation                                                         | <u>Workflow 2</u><br>Trace Impedance/<br>Coupling Check                                                                                                                              | <u>Workflow 3</u><br>SI Performance<br>Metrics Check                                                                                                                      | Workflow 4<br>DDR Simulation                                                                                                                              | <u>Workflow 5</u><br>Time-domain PDN<br>Simulation                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mainstream SI<br>L1/L2 for fast sim<br>Easy to setup;<br>Sim runs fast<br>Waveforms &<br>measurements | Geometry based<br>Trace impedance,<br>coupling &<br>reference check<br>for entire board or<br>net groups<br>Results tables;<br>Results plots;<br>Layout overlay;<br>Layout x-probing | Simulation based<br>L1/L2 for fast sim<br>L3 for non-ideal PDN<br>Loss, reflection,<br>xtalk check,<br>typically by net<br>groups<br>Waveforms;<br>Xtalk v_max &<br>v_min | Layout-based<br>DDR simulation<br>L1/L2 for fast sim<br>L3 for SSO<br>No s-parameter<br>model needed for<br>on-board DRAMs<br>Waveforms &<br>measurements | Layout-based TD<br>PDN sim<br>PDN chip-pkg-<br>board co-sim with<br>-Voltus die mode<br>- XcitePI IO model<br>with die grid<br>Voltage / current<br>distributions;<br>dynamic noise<br>propagation |

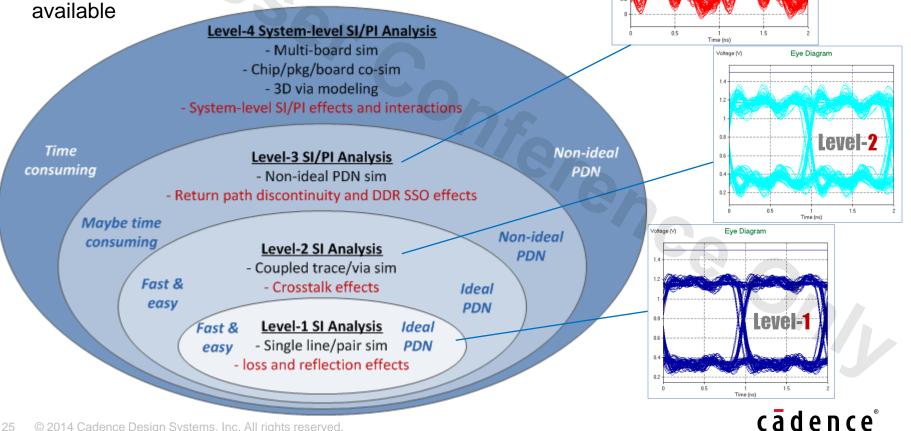

# Complete solutions Different levels for different SI/PI/EMI needs

- Using Sigrity technology, SI/PI simulations can be done at 4 levels based on considerations of trace/via couplings and non-ideal PDN

- Both layout-based and model-based solutions are available

Voltage (V)

0.6

Eye Diagram

evel-

© 2014 Cadence Design Systems, Inc. All rights reserved. 25

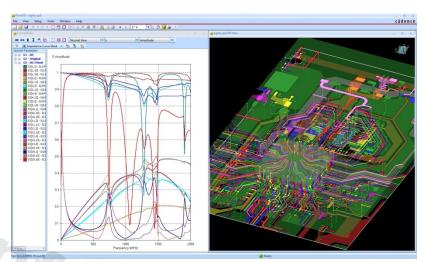

# **Complete solutions**

Layout-based frequency-domain SI/PI simulation

- Market leader and product of choice where power and signal integrity analysis is essential

- Highly accurate modeling of IC package and PCB structures

- Single-ended and mixed-mode results and post-processing

- Adaptive frequency sampling and intelligent result storage

- Supports component / circuit models with unlimited terminals

- Unique capability for ensuring accuracy down to DC with integrated PowerDC analysis

- Targeted workflows to streamline setup operations

- Integration with full wave 3D EM solver

## Frequency domain SI, PI and EMC

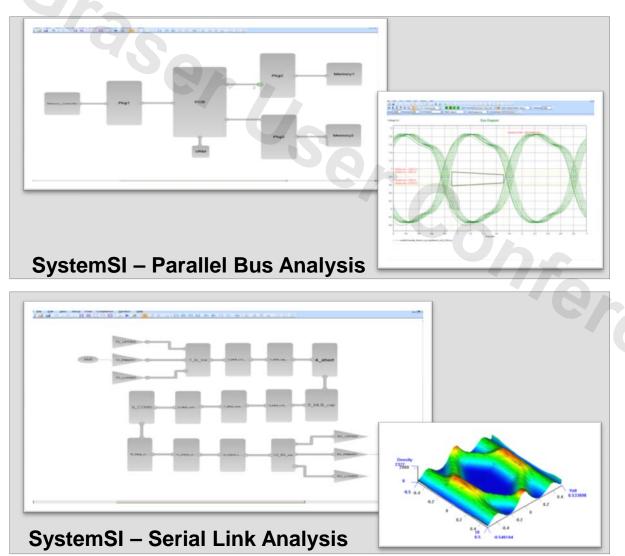

# Complete solutions High-speed bus simulation

- Simplified model connections with Model Connection Protocol (MCP) and block-wise editor

- IBIS and SPICE-based poweraware system-level modeling

- Concurrent, comprehensive simulation of both SI and PI effects

- Highly automated JEDEC-based measurement, reporting, and crossprobing capabilities for DDR interfaces

- Advanced channel simulation engine for high-capacity serial link simulation and BER analysis

- Comprehensive, parameterized AMI model library for modeling of advanced SerDes equalization

# cādence°

27 © 2014 Cadence Design Systems, Inc. All rights reserved.

# Complete solutions

# Complete solutions

# Allegro Sigrity SI Options

#### Power Aware SI Option

- SIGR011 Broadband SPICE®

- SIGR021 T2B™

- SIGR031 CAD Translators

- SIGR301 PowerSI™

- SIGR311 3D-EM

- SIGR401 SPEED2000™

- SIGR556 SystemSI<sup>™</sup> PBA II

#### **Serial Link SI Option**

- SIGR011 Broadband SPICE

- SIGR021 T2B

- SIGR031 CAD Translators

- SIGR301 PowerSI

- SIGR311 3D-EM

- SIGR506 SystemSI SLA II

#### Package Assessment and Model Extraction Option

- SIGR031 CAD Translators

- SIGR201 PowerDC™

- SIGR311 3D-EM

- SIGR801 XtractIM™

Note: Each option is a single user license. Only one of the products listed in each option can be run at a time.

#### **Constraint Manager**

cādence<sup>®</sup>

31 © 2014 Cadence Design Systems, Inc. All rights reserved.

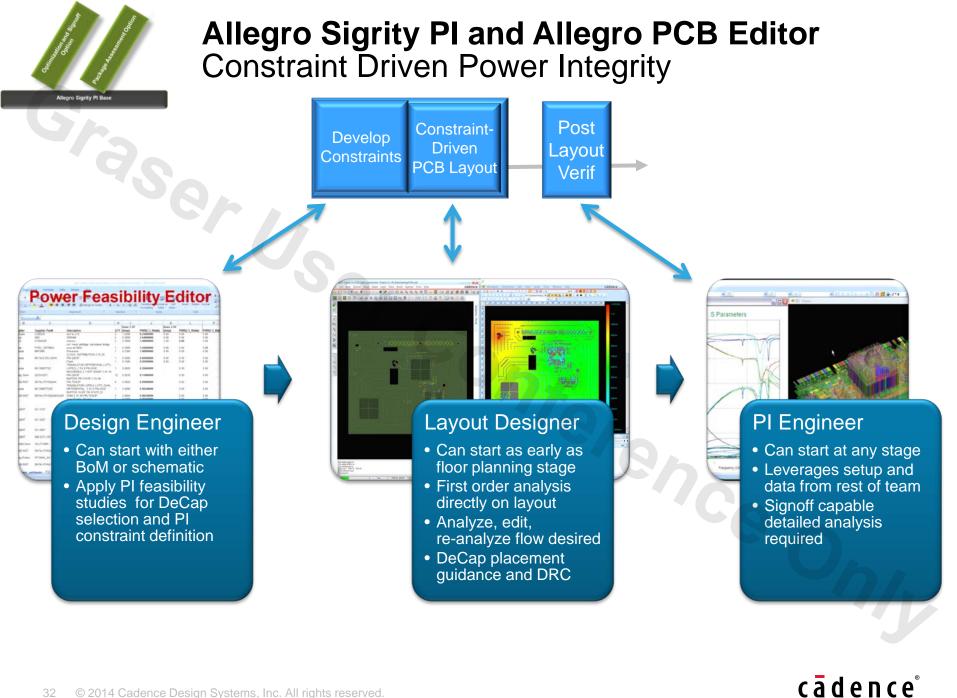

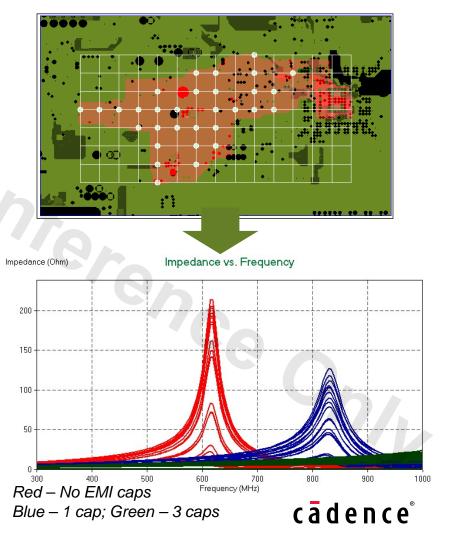

# Complete solutions Decoupling capacitor optimization

- Automated DeCap optimization of placement and value selection

- Multiple objectives: performance, cost, area, number

- Device impedance and EMI resonance checking

- DeCap loop inductance analysis to identify poorly mounted caps

- Device per-pin inductance checking and display

#### Automated positioning and selection of EMI decoupling capacitors

# Complete solutions Multi-board-package SI/PI simulations

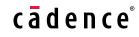

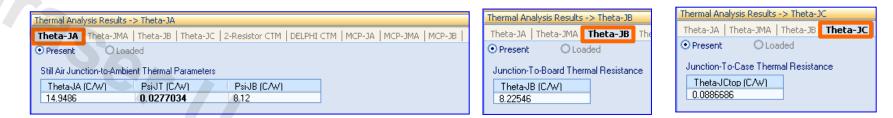

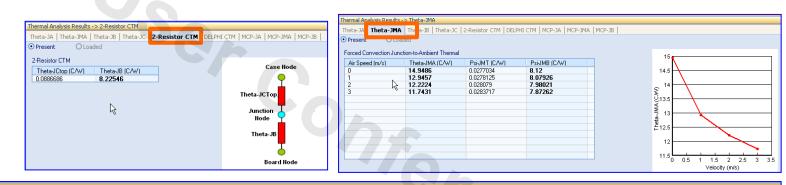

# Complete solutions Extraction of package thermal parameters

#### Thermal Analysis Results -> DELPHI CTM

Theta-JA | Theta-JMA | Theta-JB | Theta-JC | 2-Resistor CTM | DELPHI CTM | MCP-JA | MCP-JMA | MCP-JB |

#### O Loaded

#### DELPHI Compact Thermal Model

Optimum values of thermal links (C/W)

| Junction | Top Inner                            | Top Outer                                                                                                                         | Side                                                                                                                                                                                                                                               | Bottom Outer                                                                                                                                                                                                                                                                                                                    | Bottom Inner                                                                                                                                                                                                                                                                                                                                        |

|----------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N/A      | 0.100001                             | N/A                                                                                                                               | N/A                                                                                                                                                                                                                                                | N/A                                                                                                                                                                                                                                                                                                                             | 8.59441                                                                                                                                                                                                                                                                                                                                             |

| 0.100001 | N/A                                  | N/A                                                                                                                               | N/A                                                                                                                                                                                                                                                | N/A                                                                                                                                                                                                                                                                                                                             | N/A                                                                                                                                                                                                                                                                                                                                                 |

| N/A      | N/A                                  | N/A                                                                                                                               | 0.100576                                                                                                                                                                                                                                           | 0.101073                                                                                                                                                                                                                                                                                                                        | 7.80477                                                                                                                                                                                                                                                                                                                                             |

| N/A      | N/A                                  | 0.100576                                                                                                                          | N/A                                                                                                                                                                                                                                                | 0.100854                                                                                                                                                                                                                                                                                                                        | N/A                                                                                                                                                                                                                                                                                                                                                 |

| N/A      | N/A                                  | 0.101073                                                                                                                          | 0.100854                                                                                                                                                                                                                                           | N/A                                                                                                                                                                                                                                                                                                                             | N/A                                                                                                                                                                                                                                                                                                                                                 |

| 8.59441  | N/A                                  | 7.80477                                                                                                                           | N/A                                                                                                                                                                                                                                                | N/A                                                                                                                                                                                                                                                                                                                             | N/A                                                                                                                                                                                                                                                                                                                                                 |

|          | N/A<br>0.100001<br>N/A<br>N/A<br>N/A | N/A         0.100001           0.100001         N/A           N/A         N/A           N/A         N/A           N/A         N/A | N/A         0.100001         N/A           0.100001         N/A         N/A           N/A         N/A         N/A           N/A         N/A         0.100576           N/A         N/A         0.100576           N/A         N/A         0.100576 | N/A         0.100001         N/A         N/A           0.100001         N/A         N/A         N/A           N/A         N/A         N/A         0.100576           N/A         N/A         0.100576         N/A           N/A         N/A         0.100576         N/A           N/A         N/A         0.100576         N/A | N/A         0.100001         N/A         N/A         N/A           0.100001         N/A         N/A         N/A         N/A           N/A         N/A         N/A         0.100576         0.101073           N/A         N/A         0.100576         N/A         0.100854           N/A         N/A         0.101073         0.100854         N/A |

## cadence®

# **Complete solutions RFIC** passive component extraction

# Allegro Sigrity PI Options

Allegro Sigrity PI Base

Power Integrity Signoff and Optimization Option

- SIGR031 CAD Translators

- SIGR051 OptimizePI

- SIGR201 PowerDC

- SIGR301 PowerSI

- SIGR311 3D-EM

#### Package Assessment and Model Extraction Option

- SIGR031 CAD Translators

- SIGR201 PowerDC

- SIGR311 3D-EM

- SIGR801 XtractIM

Note: Each option is a single user license. Only one of the products listed in each option can be run at a time.

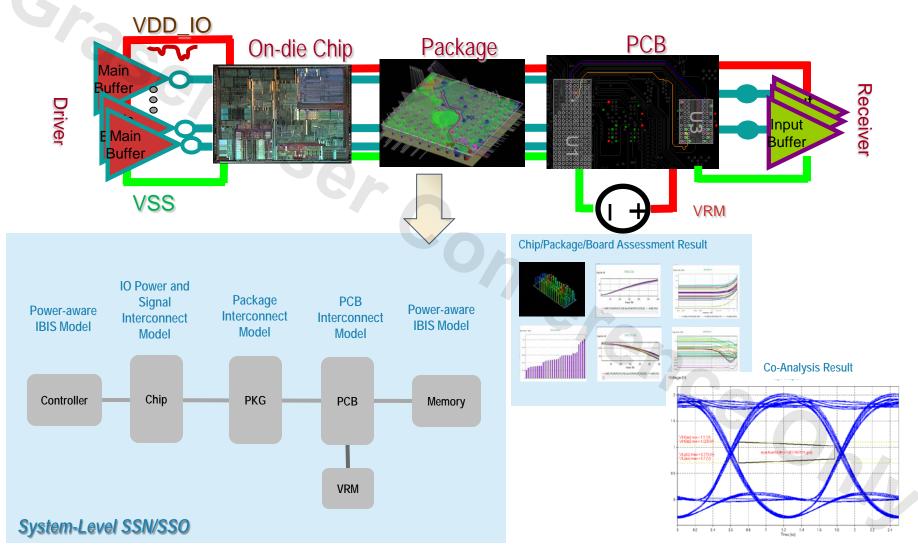

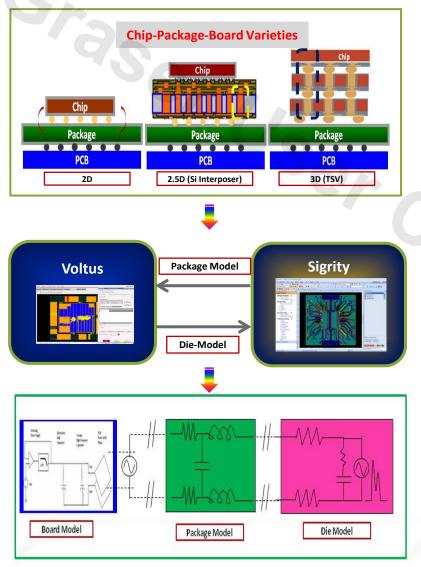

# Complete solutions Chip/package/board co-analysis

- A XtractIM<sup>™</sup> broadband SPICE format

- PowerSI<sup>®</sup> S-parameter format

#### Voltus<sup>™</sup> die model generation

- Broadband SPICE format

- Frequency and time domains

- Single-port and N-port (up to 100s)

### • Sigrity MCP interface

- Model connection protocol

- Name- or location-based

### Complete power integrity solutions

- Chip: Voltus solution + package model

- System: PowerDC<sup>™</sup> technology + die model

# cādence<sup>®</sup>

0 2014 Cadence Design Systems, Inc. All rights reserved.

Sigrity package model generation

# Complete solutions

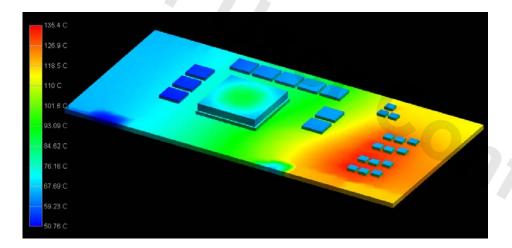

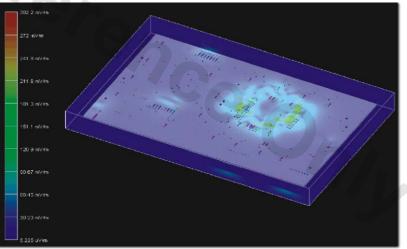

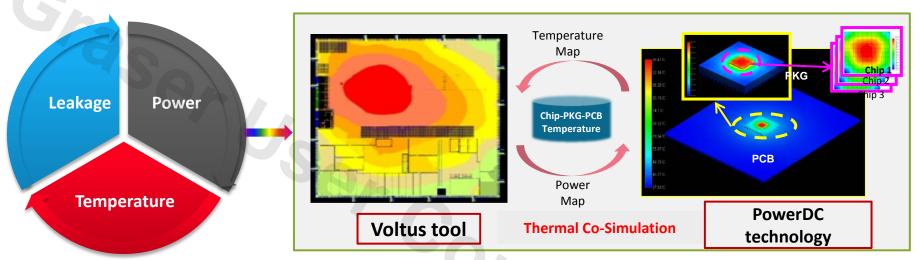

Electrical/thermal co-analysis

# Thermal runaway

- Positive feedback among chip's temperature, leakage, and power dissipation

- Temperature-dependent IR-drop and EM

- Thermal simulation in "Voltus tool + PowerDC technology"

- Voltus output: temperature and location-dependent "power map" file

- PowerDC technology computes detailed temperature distribution for chip-PKG-PCB (T vs. time)

- Voltus tool reads back "temperature map" file for EMIR convergence

- Thermal view available in 2D/3D

# cādence<sup>°</sup>

# Complete solutions

# A success story

40 © 2014 Cadence Design Systems, Inc. All rights reserved.

# Summary

Geometry-based layout check Level-3 simulation-based layout check From to Mainstream level-1 SI simulation Level-3 power-aware SI simulation From to Parallel bus simulation Serial link simulation to From PDN DC simulation PDN AC simulation Decap optimization From to to Electrical simulation Electrical / Thermal co-simulation to From SI simulation PI simulation SI/PI/EMI co-simulation to to From IOSSO / PDN PCB level simulation Chip/Pkg/Board co-simulation From to Pkg electrical model generation Thermal pkg parameters generation to From BBS model extraction RFIC passive component extraction From to IBIS model generation AMI model generation to From

# Cadence/Sigrity is your single stop SI/PI/EMI solutions for chip-package-board analysis

# Single-stop SI/PI solution for chippackage-board

cādence

© 2014 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, Allegro, PowerDC, Sigrity, and Virtuoso are registered trademarks and PowerSI, Speed2000, Voltus and XtractIM are trademarks of Cadence Design Systems, Inc. All other trademarks and logos are the property of their respective holders.