#### 2.5D/3D Design Solution

## Eric Chen & Scott Liu 31/Oct/2014

Roadmap data is provided for informational purposes only and does not represent a commitment to deliver any of the features or functionality discussed

#### Graser

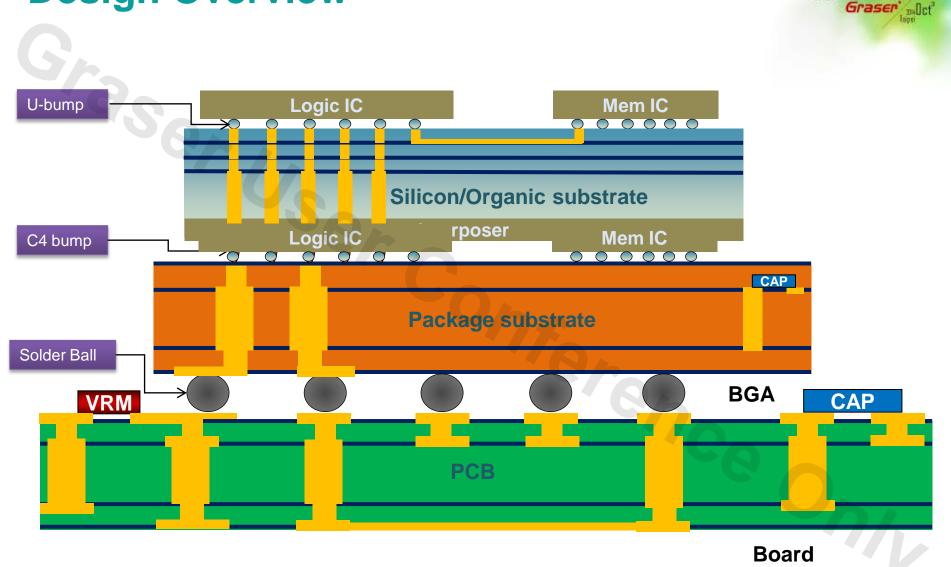

#### **Design Overview**

CONFEREN

Courtesy of TSMC

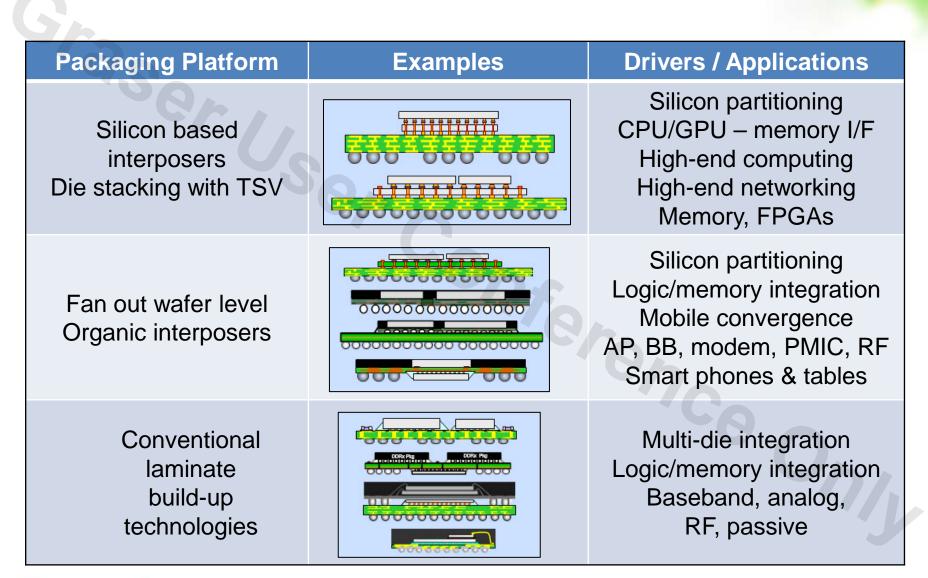

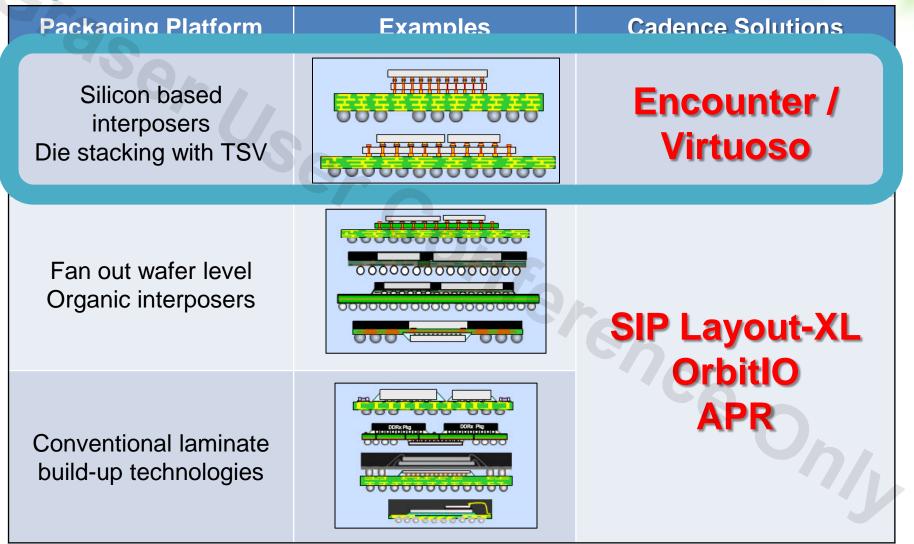

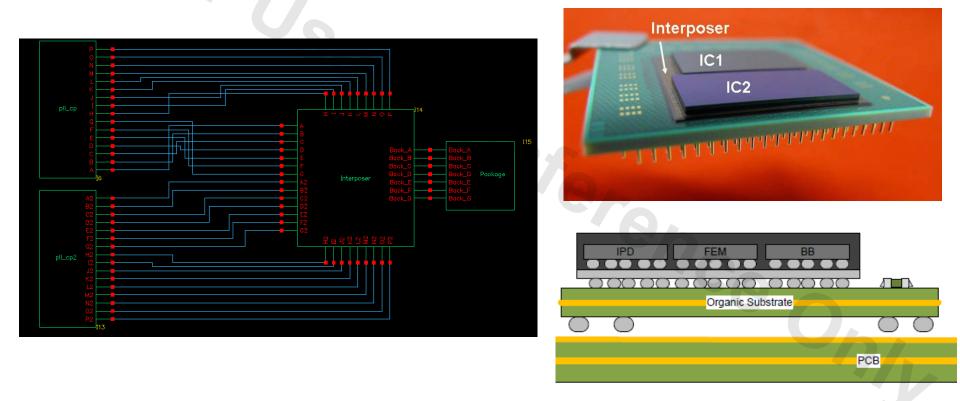

#### Multiple Pathways to 2.5D/3D Integration

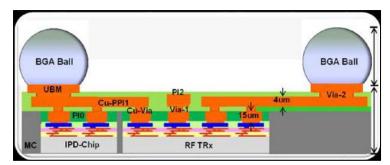

#### Fan Out Wafer Level Package (FO-WLP)

Impact on the packaging eco-system

- FO-WLP is the fastest growing packaging segment

- Benefits of cost, performance, thinner profile, & silicon partitioning

- Technology of choice for HEC

Graser

TSMC's InFo WLP

- Lower risk/cost roadmap to 3D integration for some applications

- Emergence of traditional IC fabs into the packaging space

- TSMC, Intel, Global Foundries, and others

- FO-WLP is considered a "middle-end" technology

- Front-end IC fabs extending capabilities down into packaging space

- Back-end OSATs extending capabilities up into wafer level space

- <u>Both</u> are aggressively moving to support FO-WLP

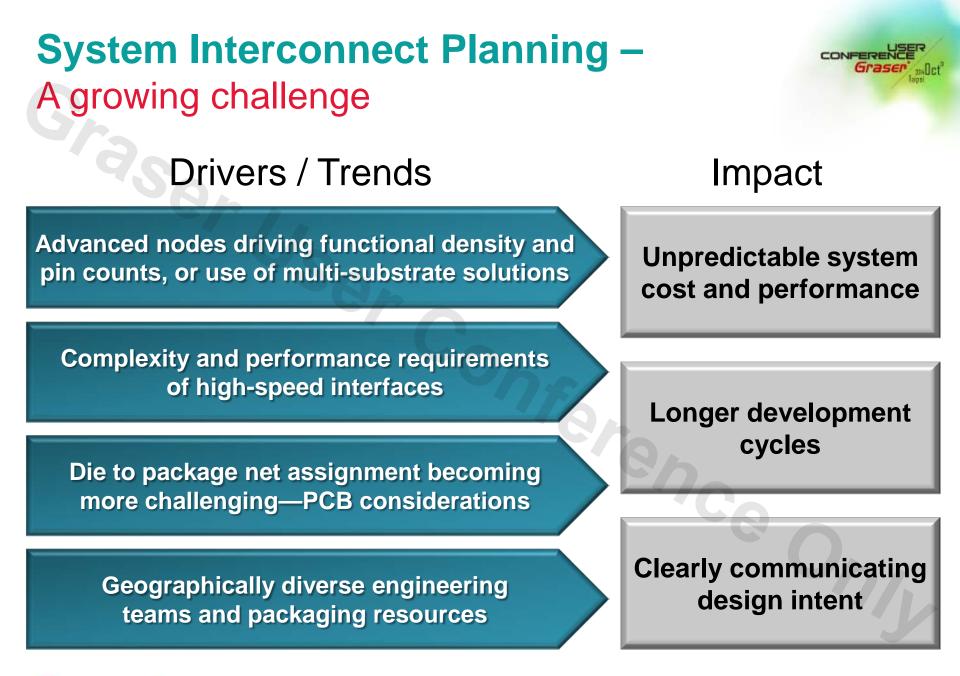

#### The Impact of Advanced Packaging Technologies

Driving new design requirements and functionality

- Co-design across multiple die, interposers and packages

- Coordination of IOpads, bumps, RDL, ball pads, TMVs, etc...

- Support from early planning through implementation

- Increasing complexity of high performance interfaces

- DDR3, DDR4, PCI Express Gen 3, USB 3.0, etc...

- Constraints, routing, and optimization

- Support for embedded die within the substrate

- For both traditional laminate and FO-WLP technologies

- Potential for 'silicon-like' design rules and requirements

- Via structures, metal density, routing, end-caps, etc...

- Foundry supported PDKs & flows, GDSII manufacturing hand-off

- Multi-die implementation

- Side-by-side, single-stack, and multi-stack

- Cu Pillar

Graser

## Advanced Technology Planning & Implementation

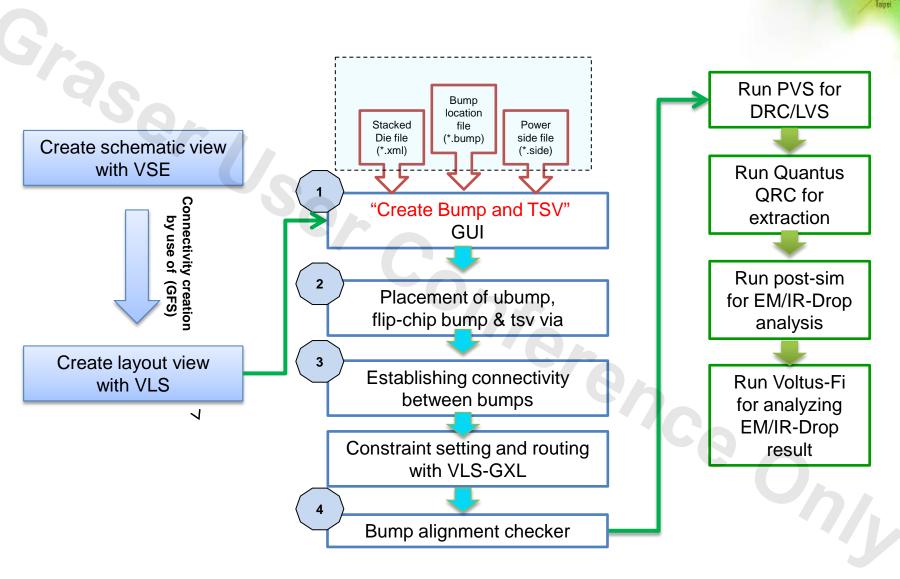

#### **Custom 3D-IC Design Flow**

Graser

CONFER

#### Note: $1+2+3+4 \rightarrow 3D-IC$ features

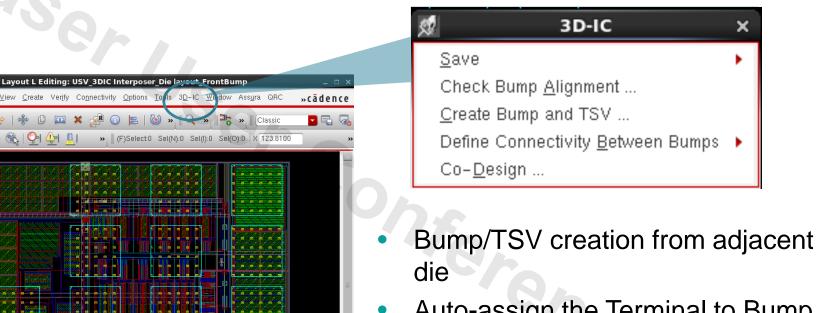

#### What's Available in Virtuoso Specifics

Auto-assign the Terminal to Bump

×

- Utilities to help resolve bump missalignment

- Export the Pad Locations/Bump Mapping File for performing the IR drop analysis

## Virtuoso 6.1.6/ ICADV12.1

Graser

#### **Wrapper Schematic**

Creating Wrapper in VSE

Graser

- Top schematic storing connectivity from die to die/interposer.

CONFE

#### **Creating Bump and TSV from VLS**

- Create bumps by using a bump location file to transfer bump information from one die to the adjacent die.

- Create bump arrays on dies such as silicon interposers. You need to assign these bump instances to their respective terminals.

|                                                                                                                 | 🕺 3D-IC 🛛 🗙                                                                                          |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Virtuoso ® Layout Suite L Editing: USV_3DIC Interposer_Die layout_FrontBump * _                                 | Save •                                                                                               |

| ch Elle Edit View Create Verify Cognectivity Options Tools 3D-IC Window Assura ORC Optimize Help câdence        | Check Bump <u>A</u> lignment                                                                         |

| □    9                                                                                                          | Create Bump and TSV                                                                                  |

|                                                                                                                 | Define Connectivity <u>B</u> etween Bumps 🕨                                                          |

| Used Routing                                                                                                    | Co- <u>D</u> esign                                                                                   |

|                                                                                                                 |                                                                                                      |

| avers tetter                                                                                                    | Create Bump and TSV X                                                                                |

|                                                                                                                 | From Bump Location File     From Bump Array Specifications     Wrapper     Bump Array Specifications |

|                                                                                                                 | Library 301C X origin 0<br>Cell Top. Die Y origin 0                                                  |

|                                                                                                                 | View schenatic Horizontol Pitch 0                                                                    |

|                                                                                                                 | Config Files<br>Stacked Die File e/Stack die.xnl No. of Rows 0                                       |

|                                                                                                                 | Bump Location File ile/pll_cp.bmp No. of Columns 0                                                   |

|                                                                                                                 | Power Side File File/Power.file                                                                      |

|                                                                                                                 | Current CellView Instance Name Oreate TSV                                                            |

|                                                                                                                 | Bump Create TSV Via Definition M1 PO                                                                 |

|                                                                                                                 | Library USV_SOIC                                                                                     |

|                                                                                                                 | Cell tBump_Chm_Sized X Offset 0                                                                      |

| se L: mouseSingleSelectPt()_leiLMBPress() M: hiZoomAbsoluteScale(hiGetCurrentWindow() 0.9) R: _b/HiMousePopUp() |                                                                                                      |

| Create Instance X: 68.140 Y: 108.250 (FS)Select: 0 CAE: OFF dX: -58.900 dY: 77.005 Dist: 96.9483 Cmd:           | QK Cancel Defaults Apply Help                                                                        |

Graser

#### Establishing Connectivity Between Bumps

- After creating bumps and TSVs, you establish connectivity between bumps.

- Assigning Bump Instances to Terminals

- Moving PinFig Objects to Bumps

- Creating Bump Labels

| Assign Bumps To Terminals 💷 🗔 🔀 | Annotation Browser ? 3 🛛 📄 🥱 🦿 🖗 🗘 💷 💥 🖓 🖓 👘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - Current CellView              | 🔯 🕶 🔀 1 🔶 🕹 1 ¥ 🐽 🕺 🕥 🤐 😽 🕌 🍓 🍰 🕂 🍕 🖉 🖓 👰 🥼 📙 💷 🦉 👘 (F)Select:0Sel(N):0Sel(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LibInterposer                   | v Scope: Current Cellview Only Q Secret - Connectivity (57/57) Constraints (0/0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Cell Name Interposer            | Type/Nets B III A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| /iew Name layout                | Be-Anlg_agnd (2)     Be-Anlg_ath_m (2)     Be-Be-Anlg_ath_m (2)     Be-Be-Be-Be-Be-Be-Be-Be-Be-Be-Be-Be-Be-B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bump And TSV Instances          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 🖲 All Bumps 🤍 Selected Bumps    | the Anlg_avdd (2)     the Anlg_avdd (2)     the Anlg_avdd_h (2)     the Anlg_avdd_h (2)     the Anlg_avdd_h (2)     the Anlg_and h (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Assign Dangling Terminals       | x ⊕ Anig_en (2)<br>→ Anig_qout (2)<br>⊕ Anig_qout (2)<br>⊕ Anig_up1 (2)<br>⊕ |

| • All                           | u 🖶 Anlg_up2 (2) 🔊 📮 🔤 🖉 👘 👘 👘 👘 👘 👘 👘 👘 👘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Selected                        | Image: Anig_vcocalen (2)       Image: Anig_vcocalen (2)         Image: Berty Anig_adg.m (1)       Image: Berty Anig_adg.m (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OK Cancel Apply Help            | #     #     EXT_Anlg_dn (1)       #     #       #     EXT_Anlg_en (1)       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #     #       #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

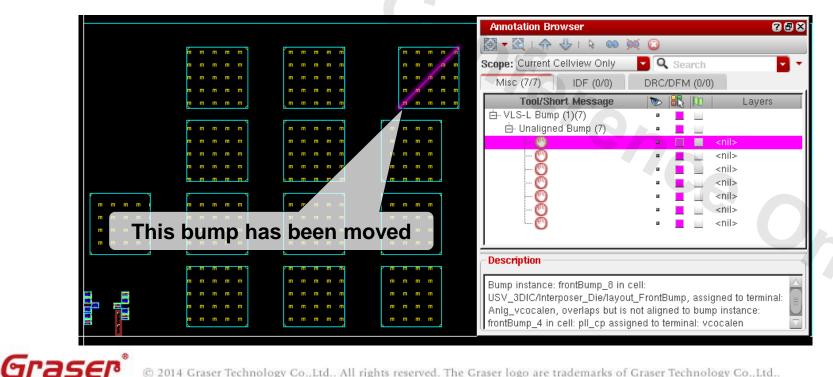

#### **Bump Alignment Checker**

- When making manual adjustments to the design, you may accidently move or delete a bump.

- This is integrated with Annotation Browser. So, you can see the list of misaligned bumps there with all relevant info.

- Using the "Check Bump alignment" to prevents this error condition from occurring.

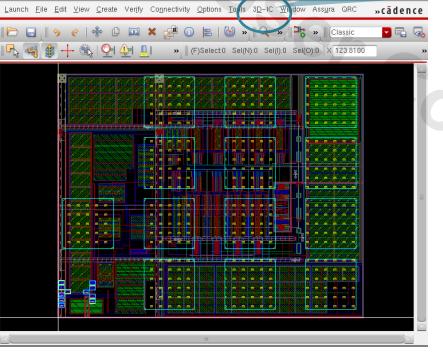

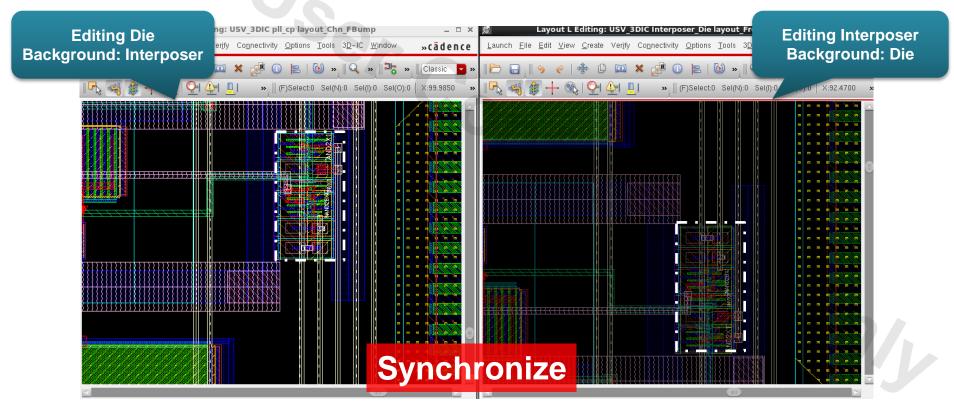

#### **Using Co-Design**

This allows designer to see one die over another at the same time.

For example, you can work on the Interposer actively in one window, with the die visible dimly in the background. And in the second window, it is reverse, i.e. the die is active with Interposer in background.

# Saving Pad Location and Bump Mapping

- Pad Locations

- This file serves as an input for performing the IR drop analysis.

- Bump Mapping

Graser

- This file will serve as an input for performing the IR drop analysis.

| Save Bump Mapping  | ×                              |

|--------------------|--------------------------------|

| Wrapper            |                                |

| Library            |                                |

| Cell               |                                |

| View               | Save Pad Location ×            |

| Config File        | Pad Location                   |

| Stacked Die File   | Pad Location File              |

| Power              | Only pad connected to this net |

| Power Side File    | Net Name                       |

| Bump Location      | Only pad of this master        |

| Rump Location File | Cell Name                      |

|                    | OK Cancel Defaults Apply Help  |

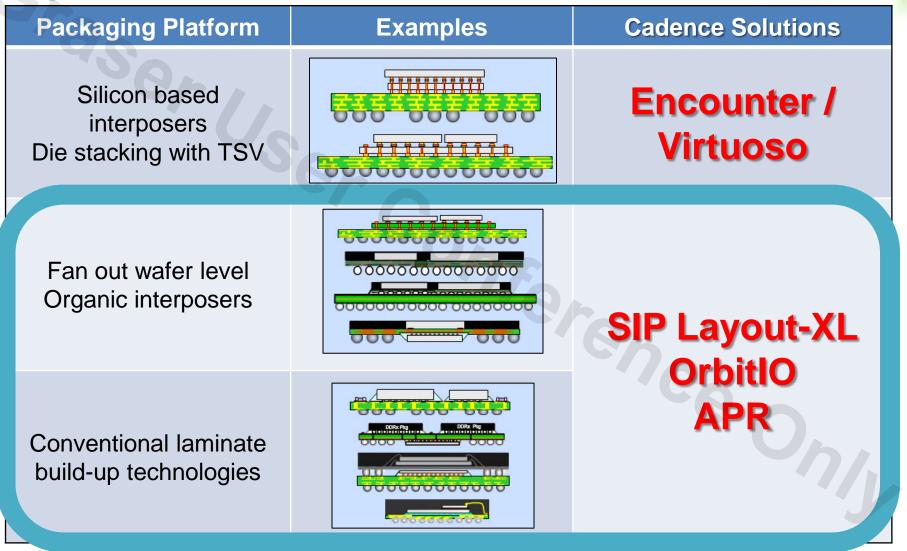

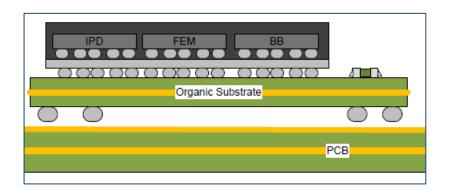

## Advanced Technology Planning & Implementation

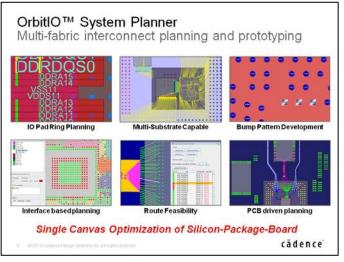

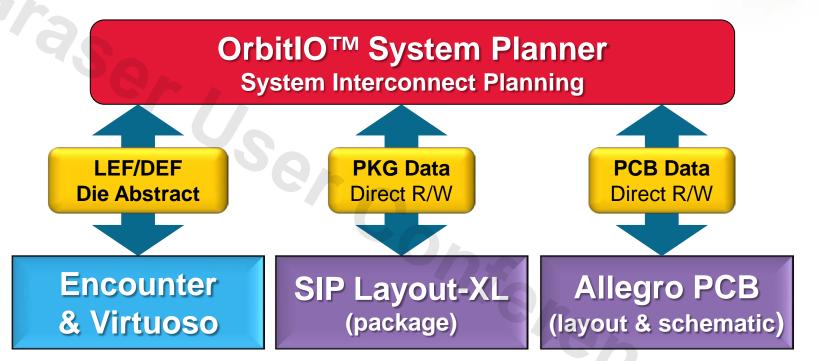

#### **Technology Enablement – SPB 16.6** Multi-Fabric Planning and Prototyping (Co-Design)

# Multi-Fabric Interoperability (Co-Design) System interconnect planning and refinement System SI™ (pre-layout co-simulation) InCyte™ OrbitlO™ System Planner (die/package/PCB) Encounter SiP Layout -XL Allegro® PCB Refinement Refinement System SI (signoff co-simulation) System SI (signoff co-simulation)

- Comprehensive co-design delivering interoperability across IC, interposer, package, and pcb

- Rapid convergences across all fabrics

- Delivering value and efficiency from early planning through implementation

- OrbitIO provides multi-fabric interconnect planning in a single-canvas environment

- Dynamic full system view and data access

- Top-down or bottom-up connectivity planning

- Easily plan and communicate design intent (including a route plan) between engineering groups or external design sources

#### **Technology Enablement – SPB 16.6** Interconnect planning for advanced technologies

- Efficient planning of the multi-fabric elements between die, package, interposer, and PCB all within a single canvas

- Objective: produce well qualified design definitions ready for implementation

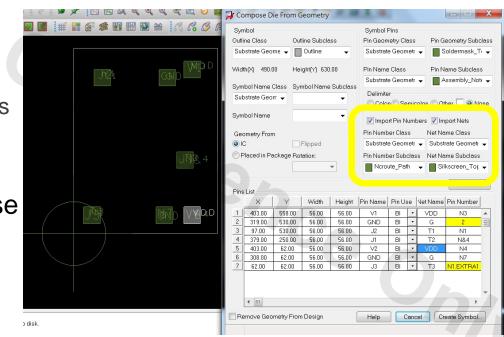

#### **Technology Enablement – SPB 16.6** Wafer/Chip Scale Package Enhancements

Updates to *Compose Die from Geometry* combined with several productized beta features expedite the creation and management of die symbols from external data sources like DXF or GDSII.

- Compose Die from Geometry updated to use additional information.

- Added mapping for Pin Numbers and Net Names

- Cross-probe highlight

- Productized commands to ease conversion of geometries into formal packaging content

- Shape to cline

- Shape to padstack

- Shape to via

Graser

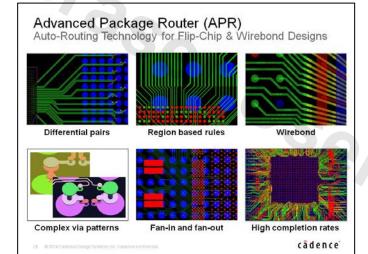

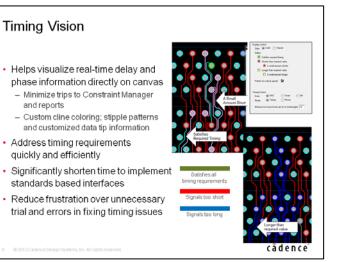

#### **Technology Enablement – SPB 16.6** High performance routing and optimization

Advanced Package Router (APR)

- Sigrity technology to reduce design cycle-time of complex packages

- High-speed constraint-aware, autorouting of flip-chip and wirebond designs

- Auto-interactive routing technologies to plan, implement, and optimize high-performance interfaces

- AiDT auto-interactive delay tuning

- AiPT auto-interactive phase tuning

- AiBT auto-interactive breakout

- Timing vision

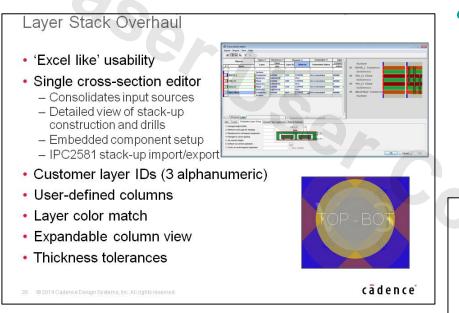

#### Technology Enablement – 2015 and beyonder Overhaul of Layer Stack-Up and Pad Stacks

Enhanced support for embedded die, Cu Pillar and complex via structures  New editing environments for layer stack-up and pad stack definitions

#### Pad Stack Overhaul

- New unified pad editing environment

- Expanded number of shape primitives

- Support complex mask schemes

- Enhanced DRC support related to pads

- Adjacent layer keep-outs

- Numerous other enhancements

25 © 2014 Cadence Design Systems, Inc. All rights reserv

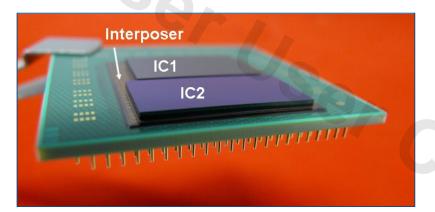

#### Technology Enablement – 2015 and Beyond Enhanced stacked application support

#### Interposer support

- New interposer design object

- View complete stack-up in one database with ability to edit the individual substrates

- Dual sided pins

- Pins on both sides of a die

- Support for 2.5D / 3D

- 3D Viewing enhancements

- Platform support

- STEP model creation support

Cadence focuses on making you success

IC1 IC2

Innovative features to address advanced technologies like interposers, FO-WLP, 2.5/3D

Enhance design efficiency through automation and interoperability

### PD FEM Organic

Future directions are influenced by your requirements