#### High-Speed Interface Driven PCB Design (Net Group, Aixx, Floorplanning...etc)

Mika Ho / Graser 31/Oct/2014

# **Topic – Chapter One**

An Interface Example – DDRx

- An Example: Timing Relationship for DDR3

- Case Description

- Routing condition

- Using features

Graser

- Before Interactive Routing

- You must define well

- You might need to define well

# **Topic – Chapter Two**

#### Net Groups

- CPU[0]\_BANK[0]

- CHNLA\_ADDR\_CMD

- CHNLB\_ADDR\_CMD

- CHNLA\_CLOCKS

- CHNLB\_CLOCKS

- CHNLA\_CTRL

- CHNLB\_CTRL

- CHNLA\_DATA

- CHNLB\_DATA

Graser

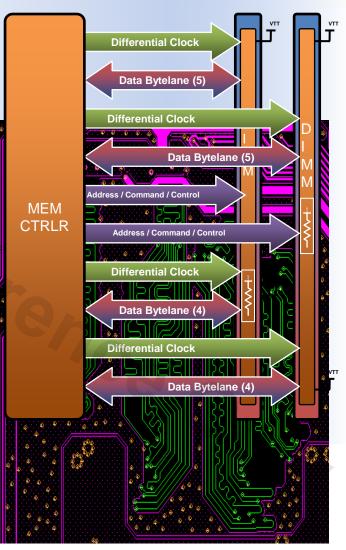

#### Plan

- 1<sup>st</sup> CLOCKS

- 2<sup>nd</sup> Target Pre-routing

- 3<sup>rd</sup> ADDR CMD & CLTR

- 4<sup>th</sup> DATA

- Routing Result

- Conclusion

- What Else?

# **Topic – Chapter Three**

#### Routing Flow

#### Optimize

Graser

- Timing vision

- Auto-interactive Delay Tune (AiDT)

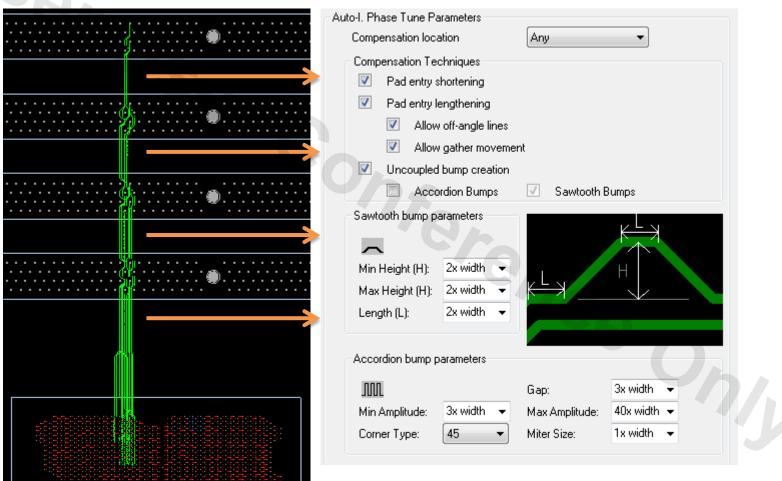

- Auto-interactive Phase Tune (AiPT)

- Auto-interactive Add Connect (AiAC)

- Auto-interactive Convert Corner (AiCC)

- Auto-interactive Breakout (AiBT)

- Auto-interactive Trunk Routing (AiTR)

# Graser User Chapter One

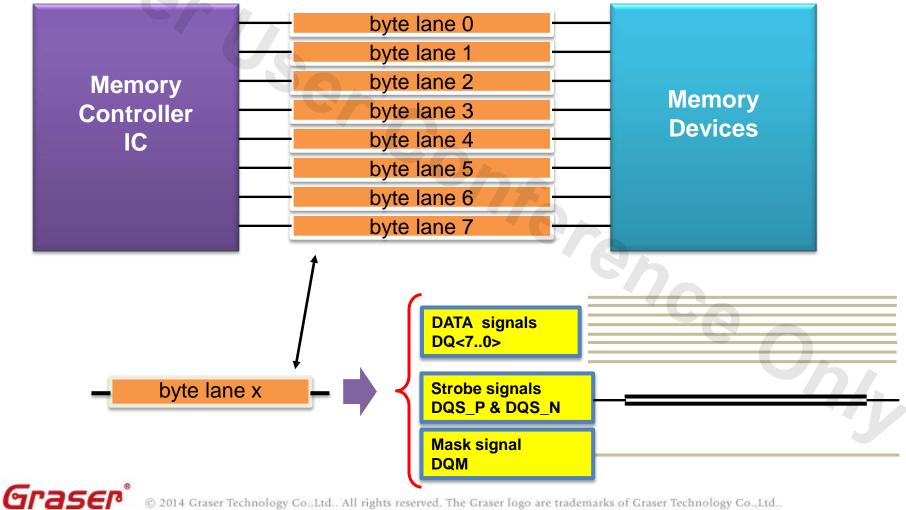

# **An Interface Example - DDRx**

- PCB designers need to connect interfaces quickly and easily

- Today's interfaces cannot be modeled in single-level hierarchy

#### Timing closure on advanced highspeed interfaces is iterative, frustrating, and time consuming

- Market demands products that are faster, have more bandwidth, and use less power

- Increasing use of standards-based interfaces

- DDR2 → DDR3 → DDR4

- PCI Express<sup>®</sup> Gen1 → Gen2 → Gen3

- − Supply voltage:  $1.8V \rightarrow 1.5V \rightarrow 1.2V$

- Increasingly sensitive signals

- Ripples through power supply

- Crosstalk

Graser

Complex set of electrical and layout implementation constraints

#### **An Example: Timing Relationship** CONFER for DDR3 550 600 1000 ADDR/CMD Data CONTROL **Strobe CLOCKS CLOCKS CLOCKS** Complex matching requirements CONTROL 4 sets of clocks, 8 sets of strobes Memory ADDR/CMD Match CLKs, strobes, and data Controller AND DATA Match CLKs, ADDR/CMD, and CONTROL

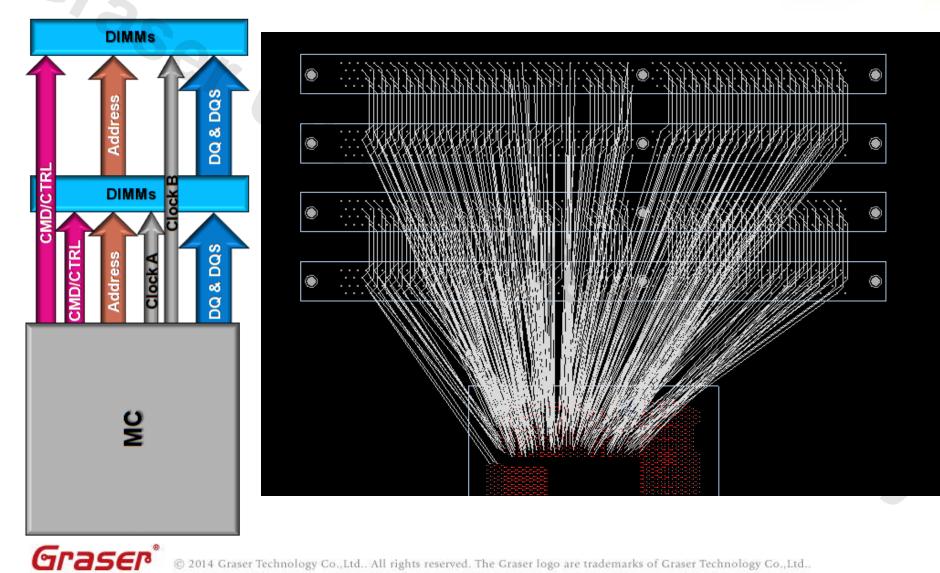

# **Case Description**

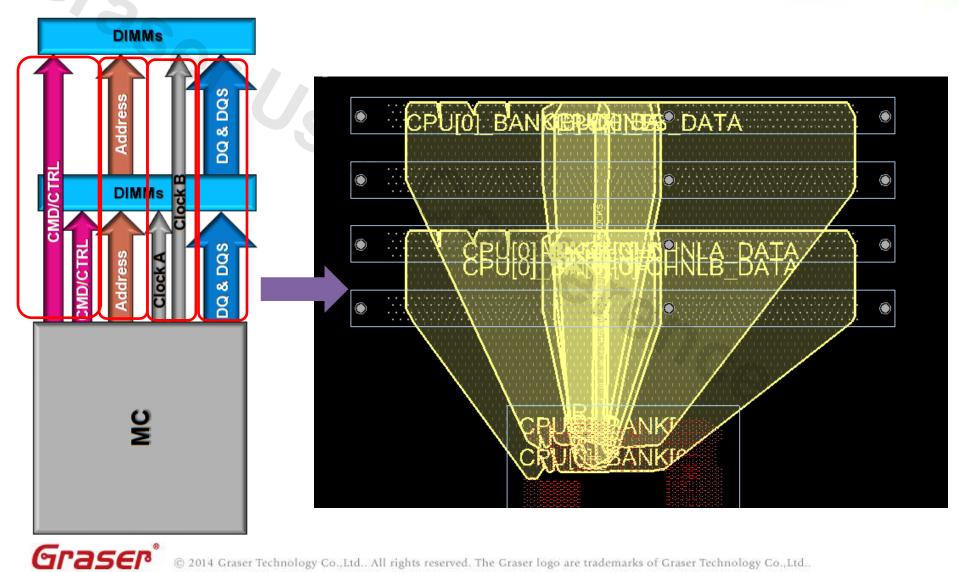

#### Routing Condition : DDR Portion

#### Area:

#### **Critical Signal:**

Net Group: CPU[0]\_BANK[0]-CHNLA\_ADDR\_CMD (24) CPU[0]\_BANK[0]-CHNLB\_ADDR\_CMD (24) CPU[0]\_BANK[0]-CHNLA\_CLOCKS (8) CPU[0]\_BANK[0]-CHNLB\_CLOCKS (8) CPU[0]\_BANK[0]-CHNLA\_CTRL (16) CPU[0]\_BANK[0]-CHNLB\_CTRL (16) CPU[0]\_BANK[0]-CHNLB\_DATA (90) CPU[0]\_BANK[0]-CHNLB\_DATA (90)

Total: 276 nets

#### Stackup: 12 layers

# **Case Description**

#### Using features

- Allegro PCB Designer v16.6 s034

- Design Planning Option

- High-Speed Option

|                                                                                                                                                | cādence°                          |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Allegro®                                                                                                                                       |                                   |

| Allegro PCB Designer                                                                                                                           |                                   |

|                                                                                                                                                | version 16.6                      |

| Copyright © 2012 Cadence Design Systems, Inc<br>Cadence, the Cadence logo and Allegro are registe<br>Systems, Inc. All others are the property | ered trademarks of Cadence Design |

| Allegro PCB Designer (was P                                                                                                                    | Performance L)                    |

| High-Speed,Design Pl                                                                                                                           | anning                            |

| 16.6 S034 (v16-6-112CQ) [8/18/20                                                                                                               | 014] Windows 32                   |

CONFER

# **Before Interactive Routing**

#### You must define well

- Constraints

- Regions

- Keep in/out areas

- Fanout

- Routing layer

- You might need to define well

- Cooper in power plane layers

# Graser User Chapter Two

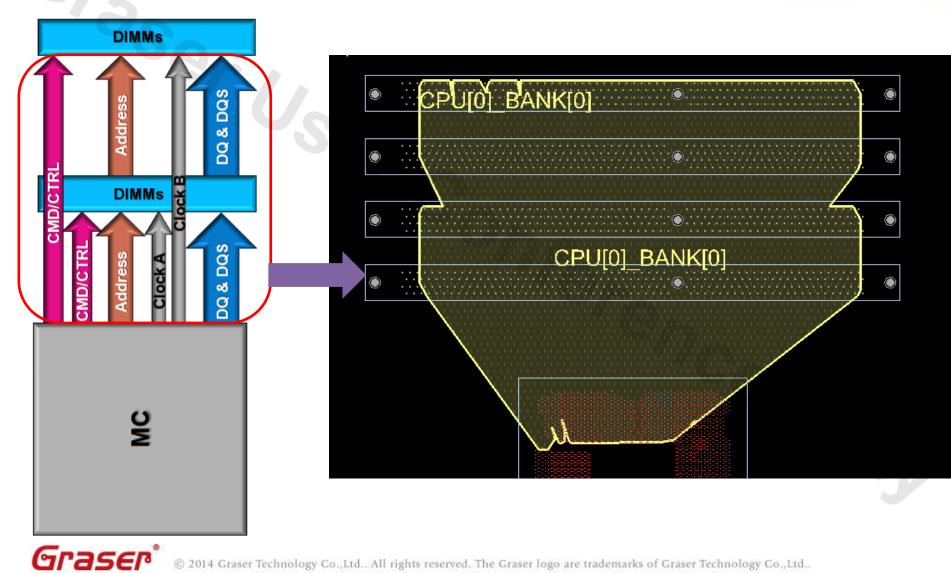

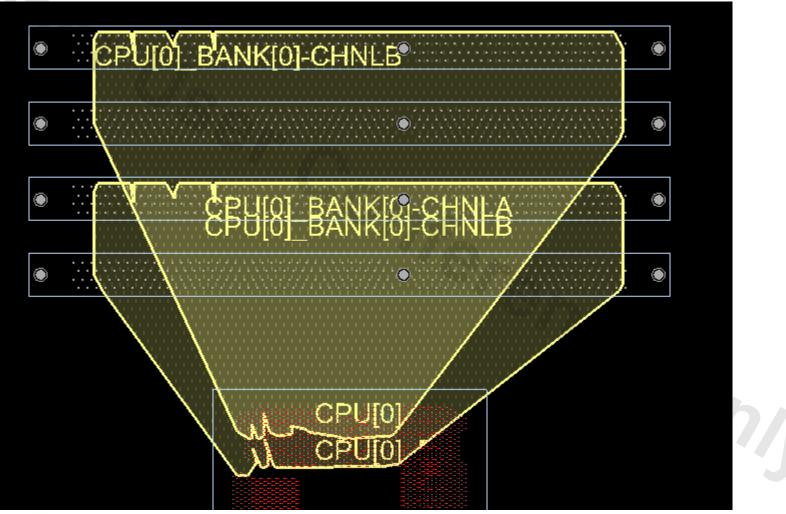

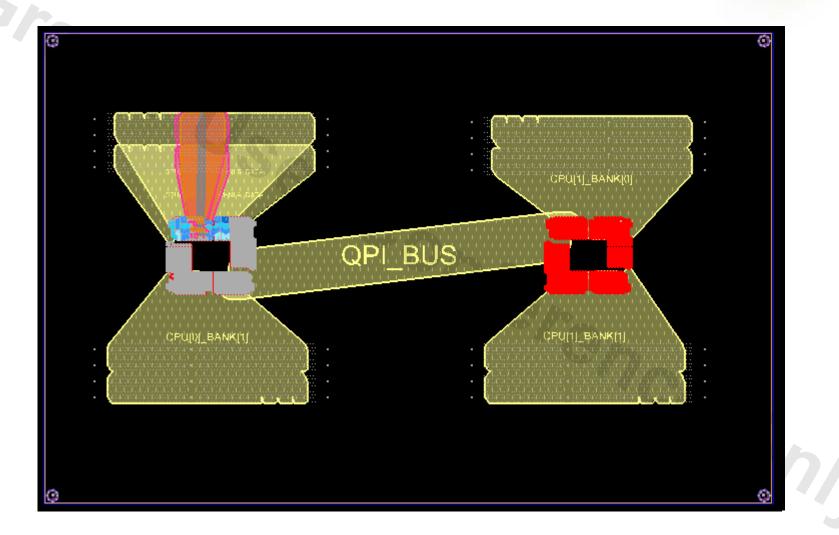

#### **Net Groups (Enhanced by QIR#5)** CONFER CPU[0]\_BANK[0]

#### Net Groups CPU[0]\_BANK[0]

CONFERE

Graser Blot

# **Net Groups** CPU[0]\_BANK[0] – Hierarchy : Top Level

CONFE

## **Net Groups** CPU[0]\_BANK[0] – Down Hierarchy

CONFER

Graser

# **Net Groups** CPU[0]\_BANK[0] – Down Hierarchy : Mid Level

CONFER

# **Net Groups** CPU[0]\_BANK[0] – Hierarchy : Bottom Level

CONFER

Graser muct

## Net Groups CPU[0]\_BANK[0]-CHNLA\_ADDR\_CMD

CPUID BANK PRUDPIERS DATA O DATA O CPUID BANK PRUDPIERS DATA O CEPUID BANK PRUDPIERS DATA

Graser

| Objects |   |       |                                    |

|---------|---|-------|------------------------------------|

| Туре    | S |       | Name                               |

| •       |   | •     | 1                                  |

| NGrp    |   | =     | CPU[0]_BANK[0]-CHNLA_ADDR_CMD (24) |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_BA0               |

| Net     |   | +     | CPU0_BANK0-CHNLA_BA1               |

| Net     |   | +     | CPU0_BANK0-CHNLA_BA2               |

| Net     |   | +     | CPU0_BANK0-CHNLA_CAS_N             |

| Net     |   | +     | CPU0_BANK0-CHNLA_MA_PAR            |

| Net     |   | +     | CPU0_BANK0-CHNLA_MA0               |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA1               |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA2               |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA3               |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA4               |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA5               |

| Net     |   | ±     | CPU0_BANK0-CHNLA_MA6               |

| Net     |   | E     | CPU0_BANK0-CHNLA_MA7               |

| Net     |   | Œ     | CPU0_BANK0-CHNLA_MA8               |

| Net     |   | Ð     | CPU0_BANK0-CHNLA_MA9               |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_MA10              |

| Net     |   | +     | CPU0_BANK0-CHNLA_MA11              |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA12              |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA13              |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA14              |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_MA15              |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_PAR_ERR_N         |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_RAS_N             |

| Net     |   | +     | CPU0_BANK0-CHNLA_WE_N              |

CONFER

## Net Groups CPU[0]\_BANK[0]-CHNLB\_ADDR\_CMD

CPUID BANK BANK BANK BATA

CPUID BANK BANK BATA

CPUID BANK BANK BATA

CEPUID BANK BATA

Graser

| Objects |   |                                    |  |

|---------|---|------------------------------------|--|

| Туре    | S | Name                               |  |

| •       |   | •                                  |  |

| NGrp    |   | CPU[0]_BANK[0]-CHNLB_ADDR_CMD (24) |  |

| Net     |   | CPU0_BANK0-CHNLB_BA0               |  |

| Net     |   | CPU0_BANK0-CHNLB_BA1               |  |

| Net     |   | CPU0_BANK0-CHNLB_BA2               |  |

| Net     |   | CPU0_BANK0-CHNLB_CAS_N             |  |

| Net     |   | CPU0_BANK0-CHNLB_MA_PAR            |  |

| Net     |   | CPU0_BANK0-CHNLB_MA0               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA1               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA2               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA3               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA4               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA5               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA6               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA7               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA8               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA9               |  |

| Net     |   | CPU0_BANK0-CHNLB_MA10              |  |

| Net     |   | CPU0_BANK0-CHNLB_MA11              |  |

| Net     |   | CPU0_BANK0-CHNLB_MA12              |  |

| Net     |   | CPU0_BANK0-CHNLB_MA13              |  |

| Net     |   | CPU0_BANK0-CHNLB_MA14              |  |

| Net     |   | CPU0_BANK0-CHNLB_MA15              |  |

| Net     |   | CPU0_BANK0-CHNLB_PAR_ERR_N         |  |

| Net     |   | CPU0_BANK0-CHNLB_RAS_N             |  |

| Net     |   | CPU0_BANK0-CHNLB_WE_N              |  |

CONFER

#### **Net Groups** CPU[0]\_BANK[0]-CHNLA\_CLOCKS

CPUID BANKERLUPING DATA ۲ ۲ ۲ ۲ ۲ ۲

|      | Objects |        |                                 |  |

|------|---------|--------|---------------------------------|--|

| Туре | S       | S Name |                                 |  |

| •    |         | •      |                                 |  |

| NGrp |         | Ξ      | CPU[0]_BANK[0]-CHNLA_CLOCKS (4) |  |

| DPr  |         | +      | CPU0_BANK0-CHNLA_CK_0           |  |

| DPr  |         | +      | CPU0_BANK0-CHNLA_CK_1           |  |

| DPr  |         | +      | CPU0_BANK0-CHNLA_CK_2           |  |

| DPr  |         | Ŧ      | CPU0_BANK0-CHNLA_CK_3           |  |

CONFER

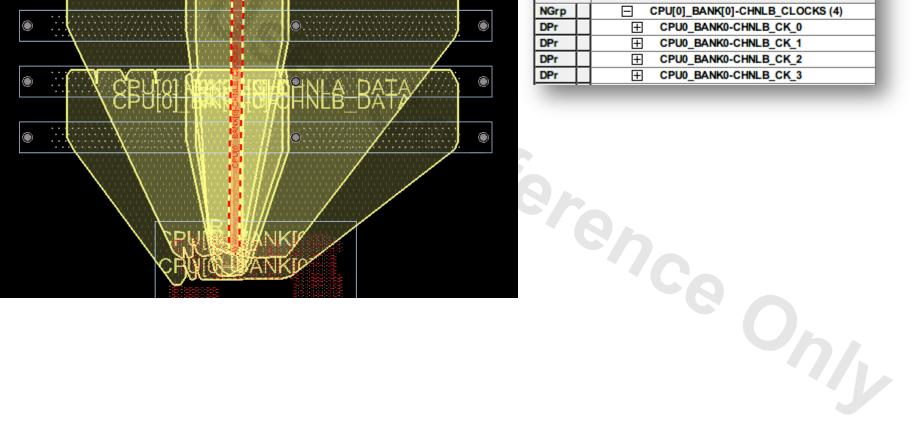

#### Net Groups CPU[0]\_BANK[0]-CHNLB\_CLOCKS

B DAT

CPUIO BANKERU DING

۲

Graser

Objects S Type Name CPU[0]\_BANK[0]-CHNLB\_CLOCKS (4) NGrp Ξ DPr +CPU0\_BANK0-CHNLB\_CK\_0 DPr +CPU0\_BANK0-CHNLB\_CK\_1 DPr +CPU0 BANK0-CHNLB CK 2 DPr **H** CPU0 BANK0-CHNLB CK 3

### Net Groups CPU[0]\_BANK[0]-CHNLA\_CTRL

| Objects |   |       |                                |

|---------|---|-------|--------------------------------|

| Туре    | S |       | Name                           |

| •       |   | *     |                                |

| NGrp    |   | Ξ     | CPU[0]_BANK[0]-CHNLA_CTRL (16) |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_CKE0          |

| Net     |   | +     | CPU0_BANK0-CHNLA_CKE1          |

| Net     |   | +     | CPU0_BANK0-CHNLA_CKE2          |

| Net     |   | +     | CPU0_BANK0-CHNLA_CKE3          |

| Net     |   | +     | CPU0_BANK0-CHNLA_CS_N0         |

| Net     |   | ±     | CPU0_BANK0-CHNLA_CS_N1         |

| Net     |   | ±     | CPU0_BANK0-CHNLA_CS_N2         |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_CS_N3         |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_CS_N4         |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_CS_N5         |

| Net     |   | $\pm$ | CPU0_BANK0-CHNLA_CS_N6         |

| Net     |   | +     | CPU0_BANK0-CHNLA_CS_N7         |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_ODT0          |

| Net     |   | E     | CPU0_BANK0-CHNLA_ODT1          |

| Net     |   | Ŧ     | CPU0_BANK0-CHNLA_ODT2          |

| Net     |   | Ð     | CPU0_BANK0-CHNLA_ODT3          |

CONFER

Grase

## Net Groups CPU[0]\_BANK[0]-CHNLB\_CTRL

| Objects |           |                                |  |

|---------|-----------|--------------------------------|--|

| Туре    | pe S Name |                                |  |

| *       |           | *                              |  |

| NGrp    |           | CPU[0]_BANK[0]-CHNLB_CTRL (16) |  |

| Net     |           | CPU0_BANK0-CHNLB_CKE0          |  |

| Net     |           | CPU0_BANK0-CHNLB_CKE1          |  |

| Net     |           | CPU0_BANK0-CHNLB_CKE2          |  |

| Net     |           | CPU0_BANK0-CHNLB_CKE3          |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N0         |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N1         |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N2         |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N3         |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N4         |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N5         |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N6         |  |

| Net     |           | CPU0_BANK0-CHNLB_CS_N7         |  |

| Net     |           | CPU0_BANK0-CHNLB_ODT0          |  |

| Net     |           | CPU0_BANK0-CHNLB_ODT1          |  |

| Net     |           | CPU0_BANK0-CHNLB_ODT2          |  |

| Net     |           | E CPU0_BANK0-CHNLB_ODT3        |  |

CONFER

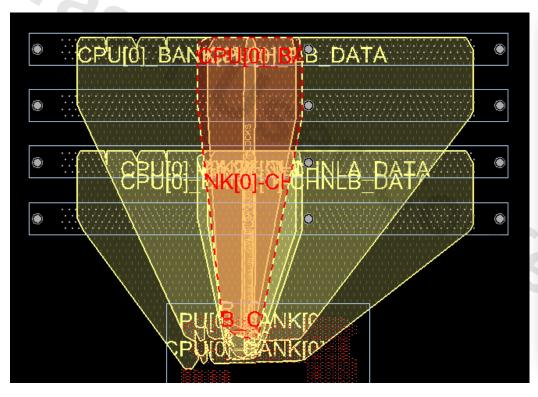

#### **Net Groups** CPU[0]\_BANK[0]-CHNLA\_DATA

|      | Objects |                                      |     |

|------|---------|--------------------------------------|-----|

| Туре | S       | Name                                 |     |

| •    |         | *                                    |     |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA (9)        |     |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[0] (1 | 10) |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[1] (1 | 10) |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[2] (1 | 10) |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[3] (1 | 10) |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[4] (1 | 10) |

| NGrp | $\Box$  | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[5] (* | 10) |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[6] (* | 10) |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-BYTE[7] (* | 10) |

| NGrp |         | CPU[0]_BANK[0]-CHNLA_DATA-ECC (10)   |     |

CONFER

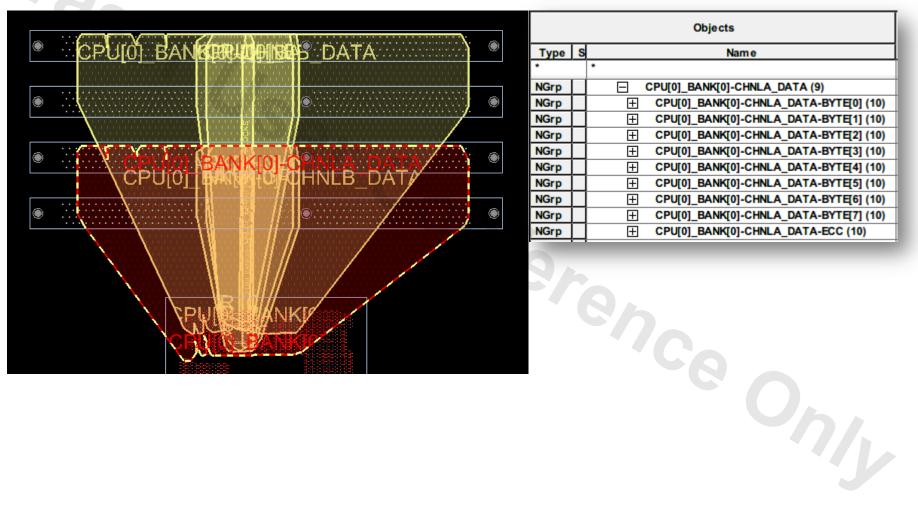

## **Net Groups** CPU[0]\_BANK[0]-CHNLB\_DATA

| Objects |   |   |                                        |

|---------|---|---|----------------------------------------|

| Туре    | S |   | Nam e                                  |

| •       |   | • |                                        |

| NGrp    |   | Ξ | CPU[0]_BANK[0]-CHNLB_DATA (9)          |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[0] (10) |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[1] (10) |

| NGrp    |   | + | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[2] (10) |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[3] (10) |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[4] (10) |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[5] (10) |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[6] (10) |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-BYTE[7] (10) |

| NGrp    |   | Ŧ | CPU[0]_BANK[0]-CHNLB_DATA-ECC (10)     |

|         |   |   |                                        |

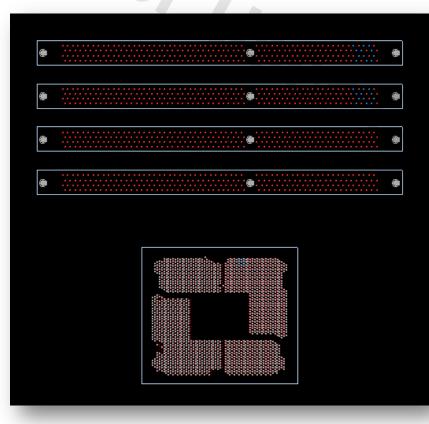

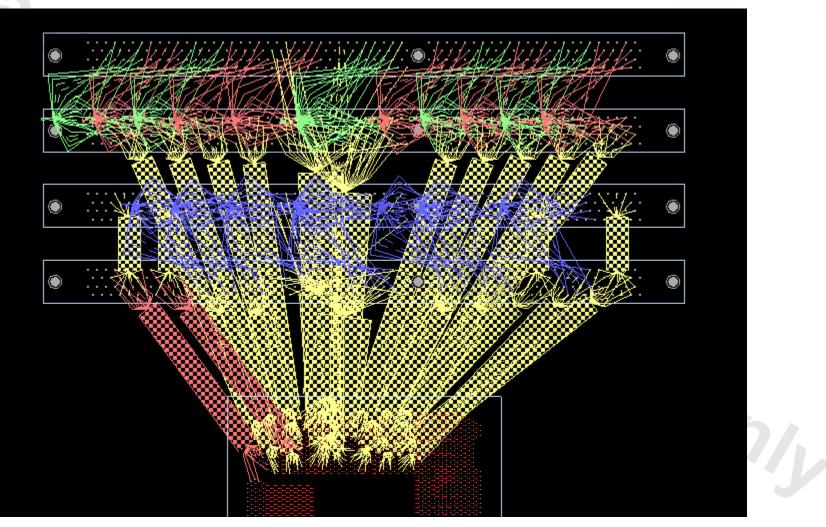

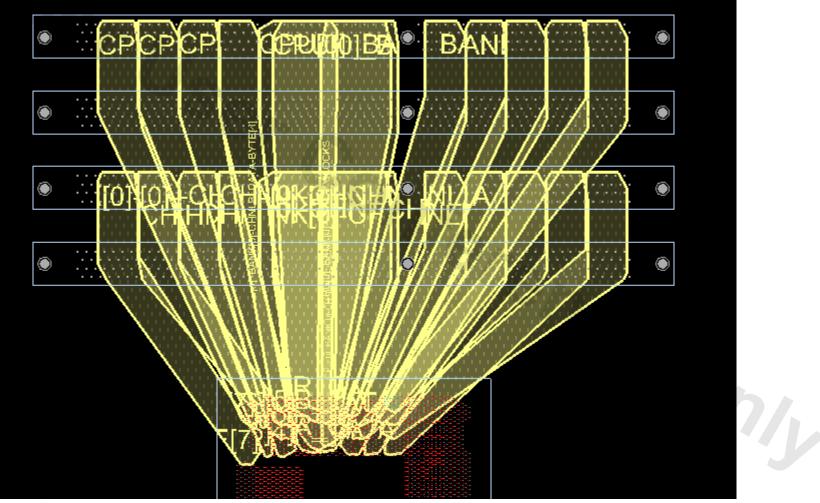

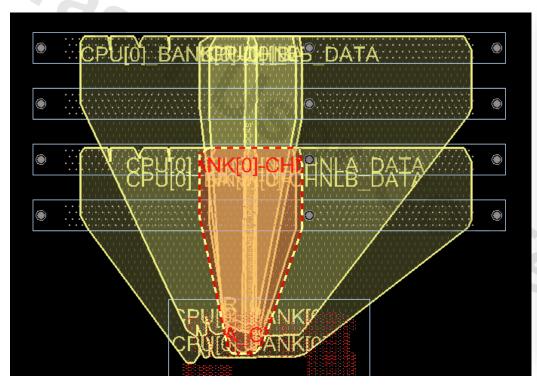

# Net Groups and Placement Quick and easy way to "verify" your placement

- The container gives you a way to visualize the overall "routing domain" of the interface

- Visual placement checks let you see parts "out-of-place"

- The polygon envelops ALL the pins of nets in the net group

#### 1<sup>st</sup> CLOCKS (Channel A & B)

|                                         | .}-                             |

|-----------------------------------------|---------------------------------|

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         | 4                               |

|                                         | $Z_1$                           |

|                                         | ·¥                              |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         | ,                               |

|                                         | <b>)</b>                        |

|                                         | <b>4</b> 1                      |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         | ky                              |

|                                         | ₩                               |

|                                         | ¥ <sup>-</sup>                  |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

| ſ                                       |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

|                                         |                                 |

| 100000000000000000000000000000000000000 |                                 |

| 2020-2-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0- |                                 |

| 65,626,666                              | <b>9</b> 2886666666666666666666 |

| 0.041-0.0640-064                        |                                 |

|                                         |                                 |

|                                         |                                 |

| INF0        | (SPGRE-16): | Status: Topological planning completed normally               |

|-------------|-------------|---------------------------------------------------------------|

| INF0        | (SPGRE-16): | Number of rats scheduled = 16                                 |

| INF0        | (SPGRE-16): | Number of spatial unroutes for scheduled rats = $0$           |

| INF0        | (SPGRE-16): | Number of topological unroutes for scheduled rats = 0         |

| INF0        | (SPGRE-16): | Number of crossings on scheduled rats = 0                     |

| INF0        | (SPGRE-16): | Number of clearance on scheduled rats = 0                     |

| INF0        | (SPGRE-16): | Number of electrical violations on sceduled rats = 27         |

| INF0        | (SPGRE-16): | Number of timing constraints on scheduled rats = 32           |

| INF0        | (SPGRE-16): | Number of timing constraint violations on scheduled rats = 15 |

| INF0        | (SPGRE-16): | DiffPair Uncoupled Plan Length = 1225.584 MIL                 |

| INFO        | (SPGRE-16): | DiffPair Gather Plan Length = 1203.927 MIL                    |

| <b>INFO</b> | (SPGRE-16): | DiffPair Phase Mismatch = 300.889 MIL                         |

| INF0        | (SPGRE-16): | Number of DiffPair Unroutes = 0                               |

| INF0        | (SPGRE-16): | Number of vias on scheduled rats = 16                         |

| INF0        | (SPGRE-16): | Routed length of scheduled rats = 42299.679 MIL               |

| INF0        | (SPGRE-16): | Percent complete on scheduled rats = 100.00%                  |

| INF0        | (SPGRE-16): | Execution time = $66$ seconds                                 |

| INF0        | (SPGRE-16): | Memory currently in use = 158804 KB                           |

|             |             |                                                               |

|             |             |                                                               |

CONFER

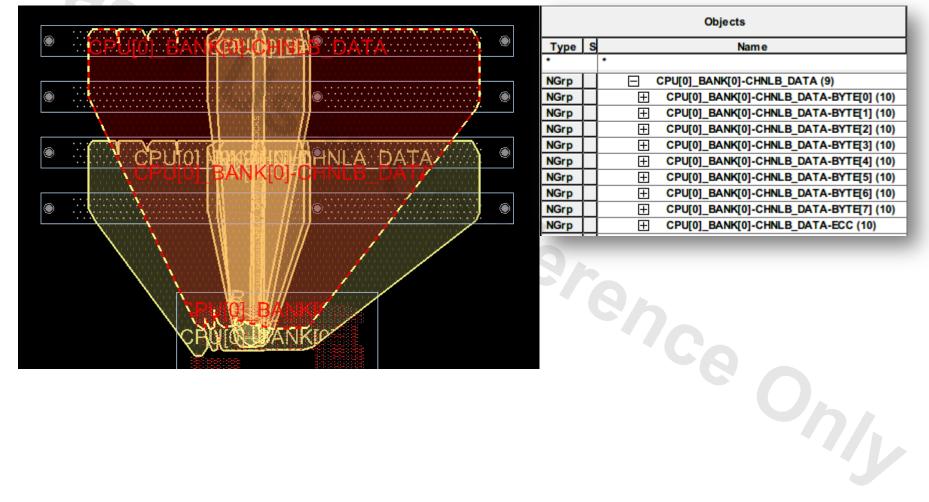

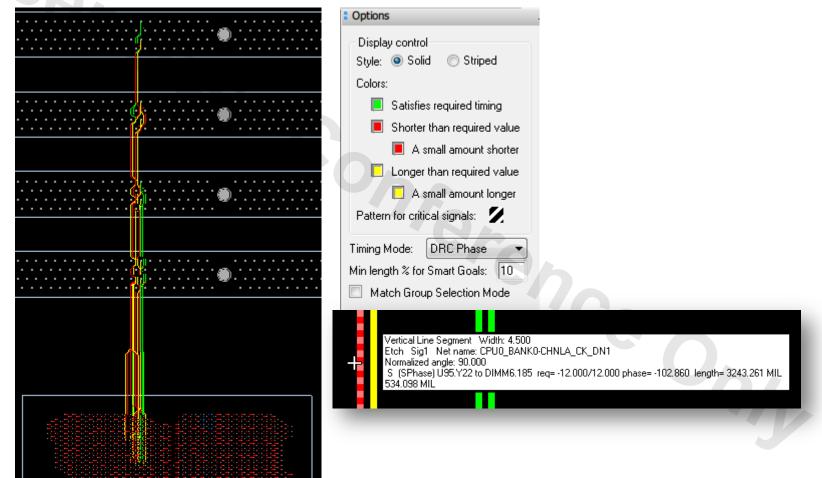

#### 1<sup>st</sup> CLOCKS (Channel A & B) - Timing vision (High-Speed option)

CONFER

#### 1<sup>st</sup> CLOCKS (Channel A & B) - AiPT (High-Speed option)

CONFER

#### Graser

#### 2<sup>nd</sup> Target pre-routing

CONFERE

Graser

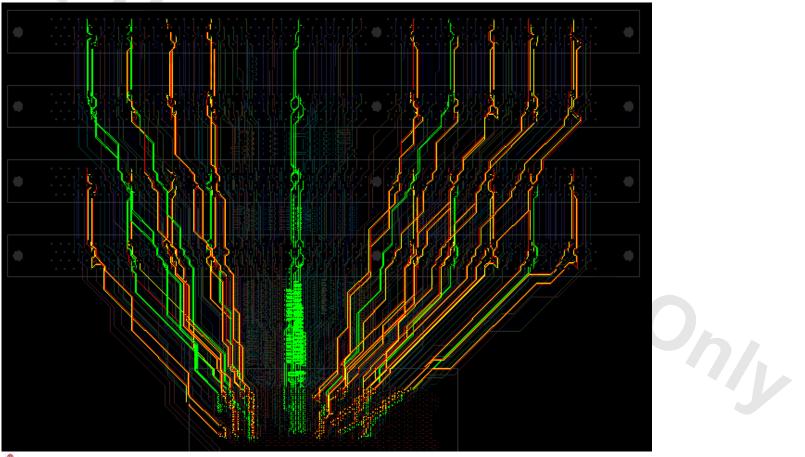

#### 3<sup>rd</sup> ADDR CMD & CTRL (Channel A & B)

#### 3<sup>rd</sup> ADDR CMD & CTRL (Channel A & B) - Timing vision (High-Speed option)

CONFER

# Plan (Design Planning Option)

Graser

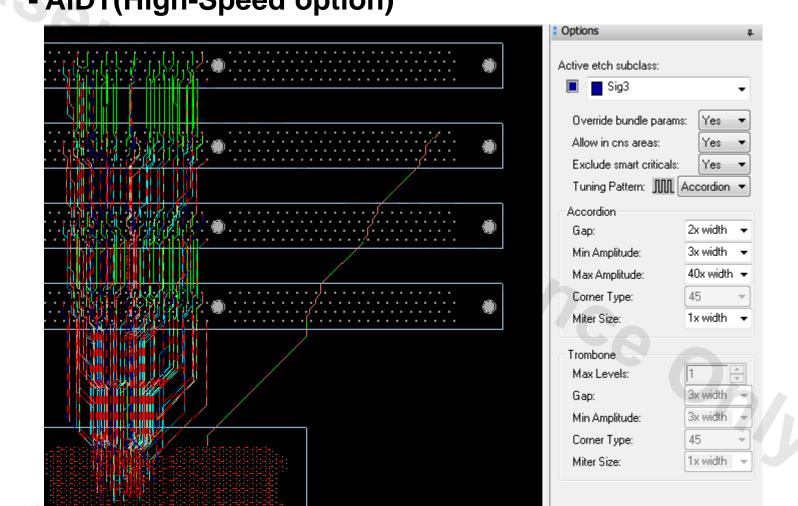

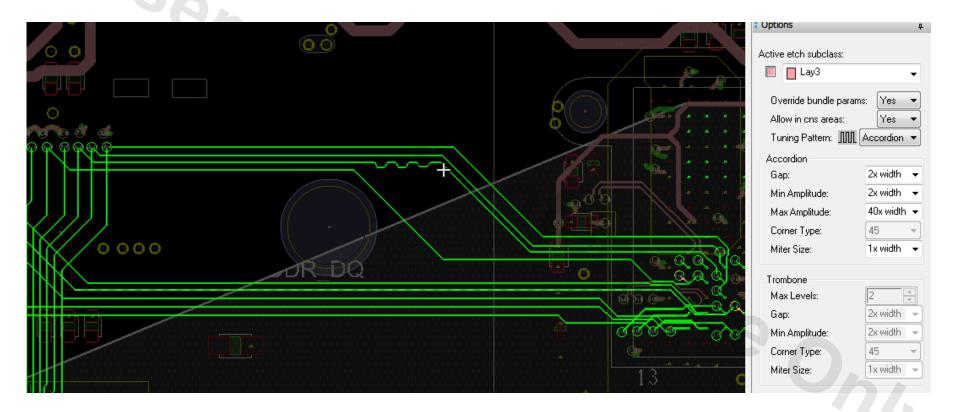

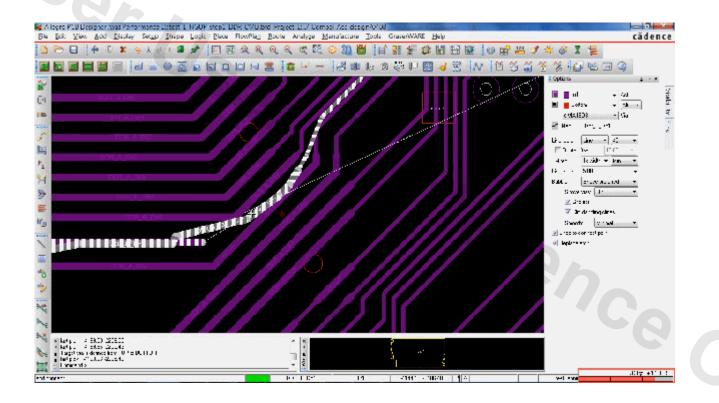

#### 3<sup>rd</sup> ADDR CMD & CTRL (Channel A & B) - AiDT(High-Speed option)

Graser

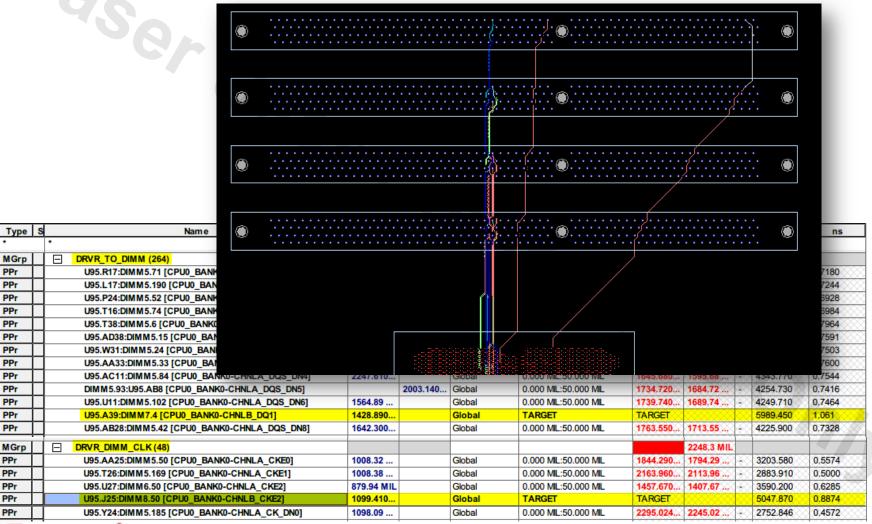

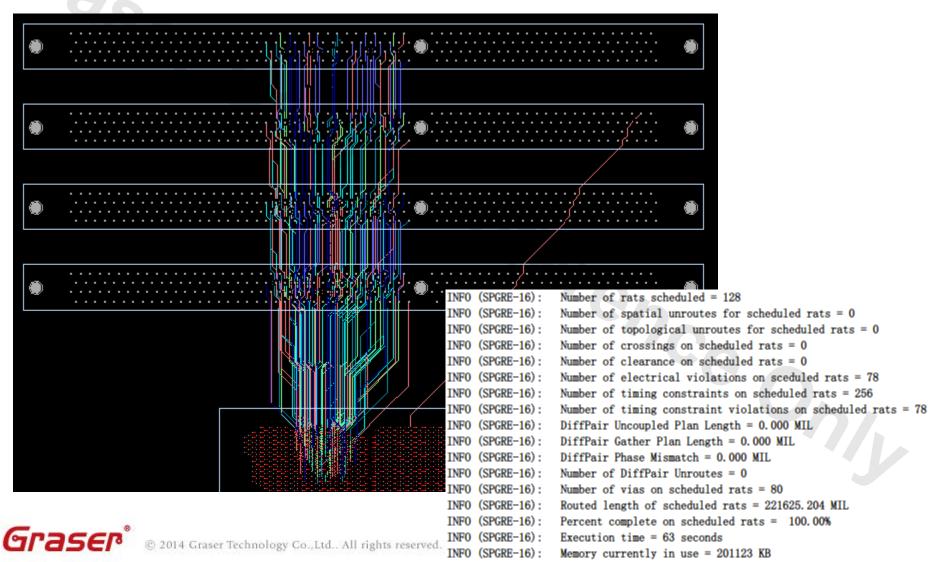

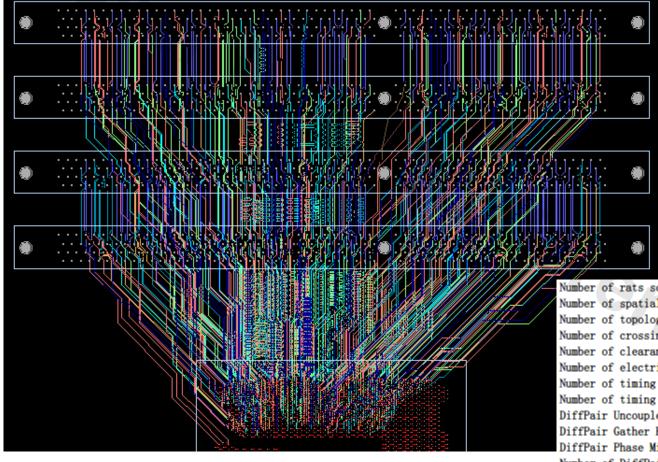

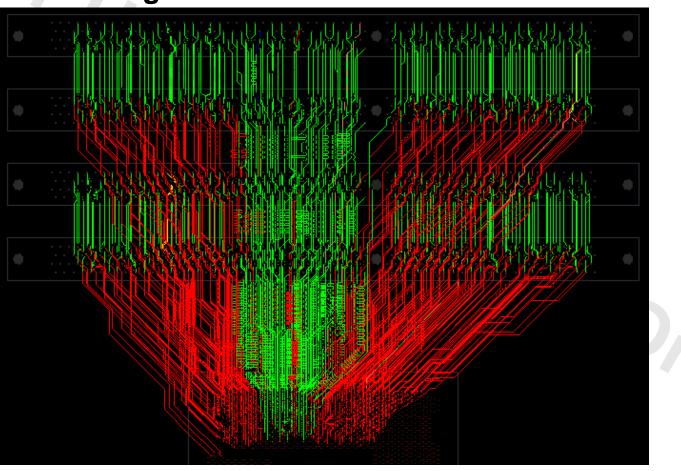

#### 4<sup>th</sup> DATA (Channel A & B)

Graser<sup>®</sup> © 2014 Graser Technology Co., Ltd., All rights reserved. The Graser logo are

Number of rats scheduled = 432 Number of spatial unroutes for scheduled rats = 0 Number of topological unroutes for scheduled rats = 2 Number of crossings on scheduled rats = 0 Number of clearance on scheduled rats = 0Number of electrical violations on sceduled rats = 336 Number of timing constraints on scheduled rats = 864 Number of timing constraint violations on scheduled rats = 277 DiffPair Uncoupled Plan Length = 16723.220 MIL DiffPair Gather Plan Length = 15385.325 MIL DiffPair Phase Mismatch = 1231.296 MIL Number of DiffPair Unroutes = 0 Number of vias on scheduled rats = 216 Routed length of scheduled rats = 722961.758 MIL Percent complete on scheduled rats = 99.54% Execution time = 676 seconds Memory currently in use = 217572 KB

## 4<sup>th</sup> DATA (Channel A & B) - Unplanning

•

CONFER

クレ

<u>, .</u>.....

#### 4<sup>th</sup> DATA (Channel A & B) - Manual add connection

## 4<sup>th</sup> DATA (Channel A & B)

- Timing vision (High-Speed option)

- DRC Phase view

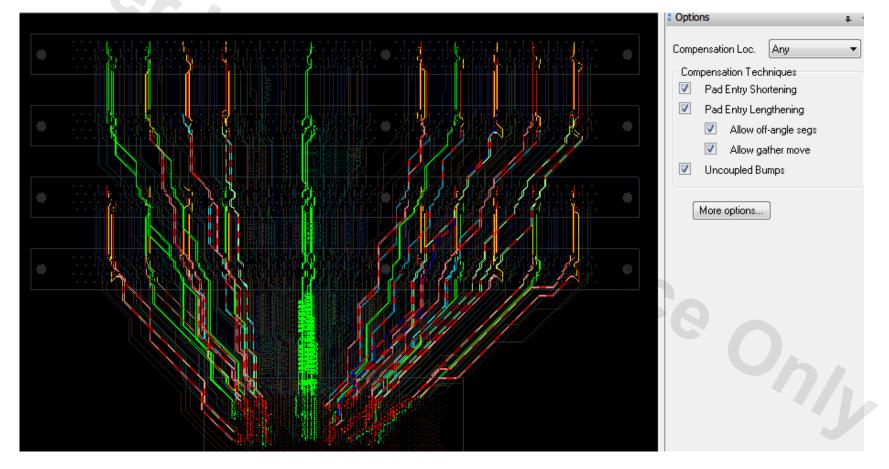

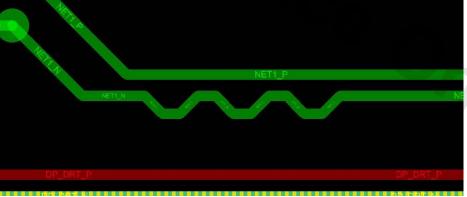

## 4<sup>th</sup> DATA (Channel A & B) - AiPT(High-Speed option)

CONFER

## 4<sup>th</sup> DATA (Channel A & B) - AiPT(High-Speed option)

## 4<sup>th</sup> DATA (Channel A & B) - Manual Phase Tuning

## 4<sup>th</sup> DATA (Channel A & B)

- Timing vision (High-Speed option)

- DRC Timing view

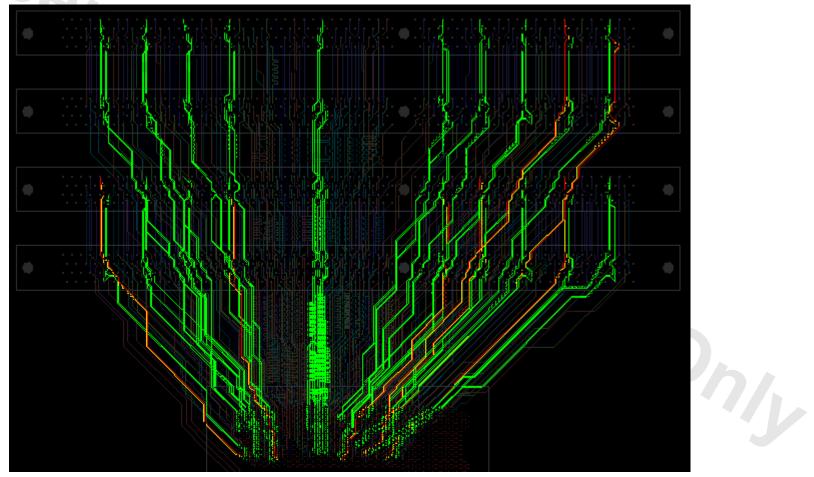

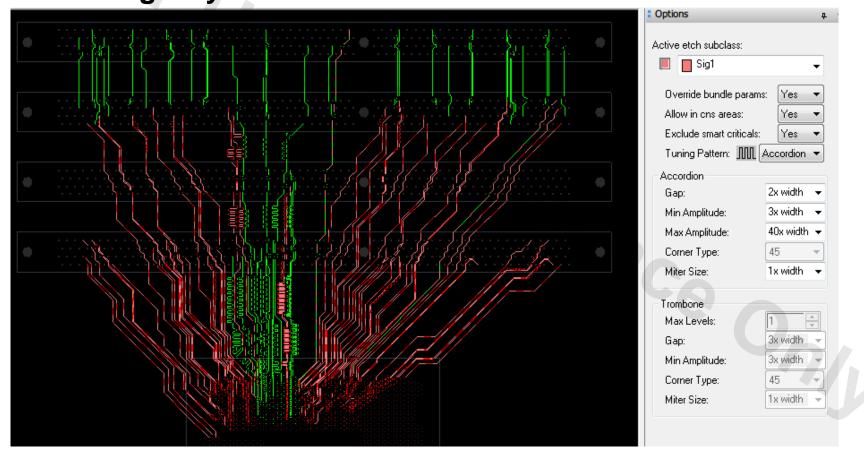

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig1 layer

CONFER

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig1 layer

© 2014 Graser Technology Co., Ltd.. All rights reserved. The Graser logo ar

Status: Auto Delay Tune completed normally Number of rats scheduled = 54Number of electrical violations on sceduled rats = 26 Number of timing constraints on scheduled rats = 108 Number of timing constraint violations on scheduled rats = 0 DiffPair Phase Mismatch = 384.141 MIL Routed length of scheduled rats = 190206.853 MIL Execution time = 493 seconds Memory currently in use = 279991 KB

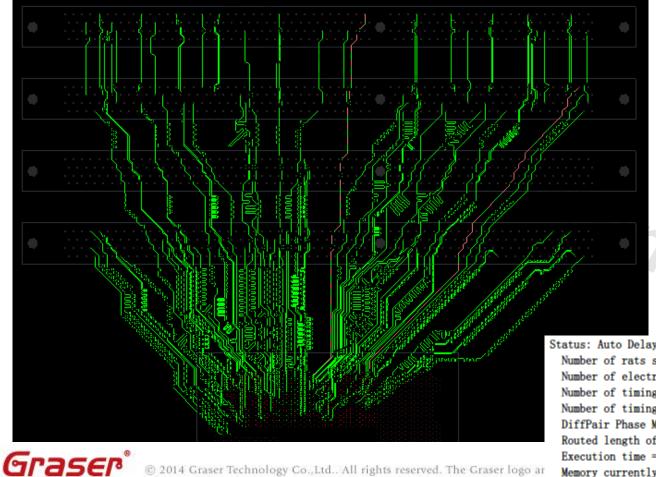

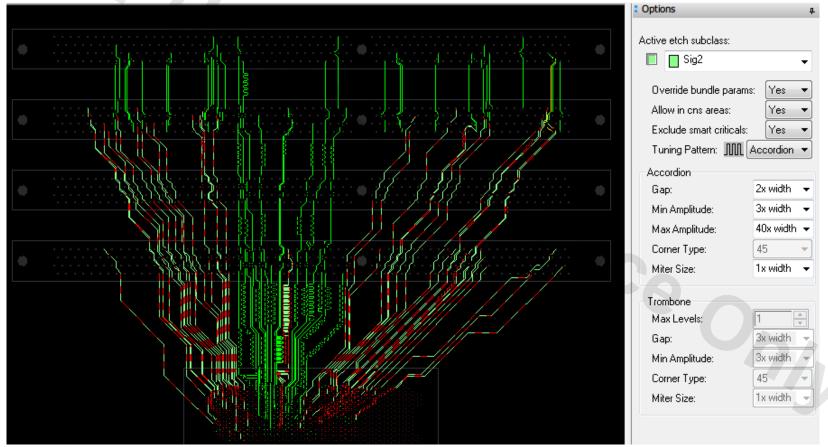

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig2 layer

CONFER

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig2 layer

© 2014 Graser Technology Co.,Ltd.. All rights reserved. The Graser logo ar

Status: Auto Delay Tune completed normally

Number of rats scheduled = 42

Number of electrical violations on sceduled rats = 12

Number of timing constraints on scheduled rats = 84

Number of timing constraint violations on scheduled rats = 0

DiffPair Phase Mismatch = 270.318 MIL

Routed length of scheduled rats = 154392.988 MIL

Execution time = 191 seconds

Memory currently in use = 280637 KB

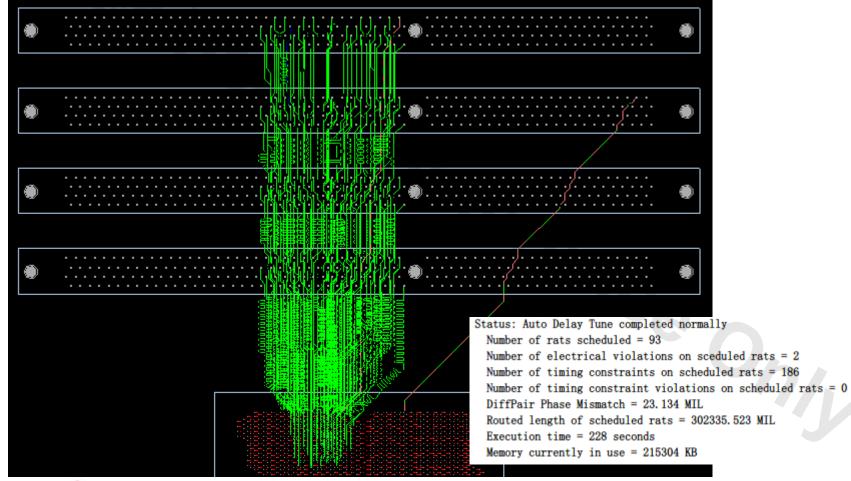

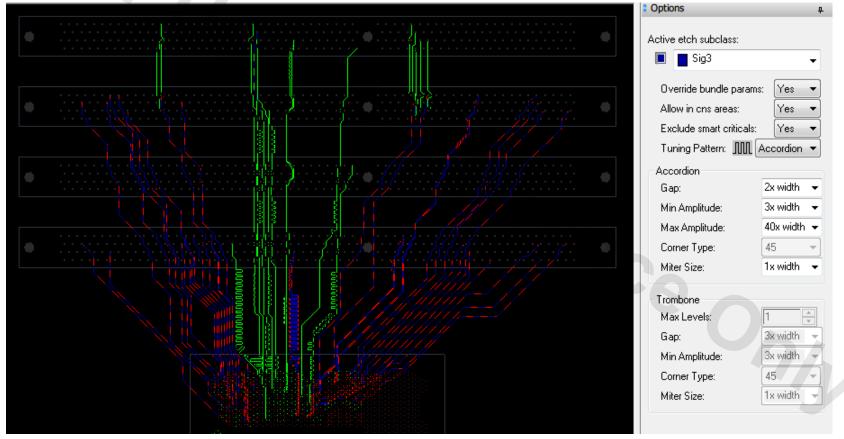

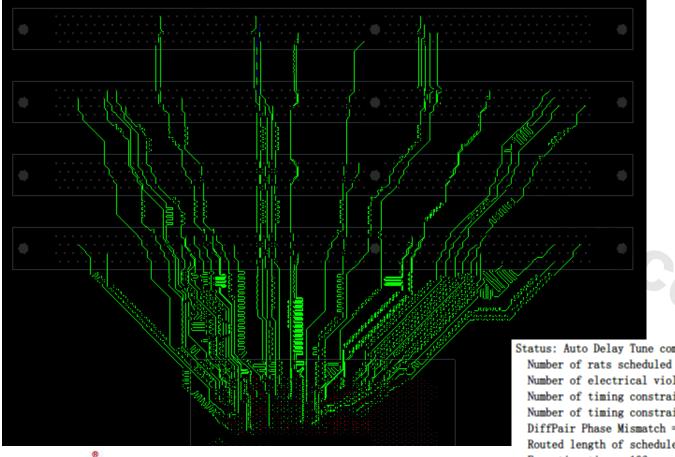

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig3 layer

CONFER

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig3 layer

Graser

© 2014 Graser Technology Co.,Ltd.. All rights reserved. The Graser logo at

Status: Auto Delay Tune completed normally

Number of rats scheduled = 34

Number of electrical violations on sceduled rats = 6

Number of timing constraints on scheduled rats = 68

Number of timing constraint violations on scheduled rats = 0

DiffPair Phase Mismatch = 18.444 MIL

Routed length of scheduled rats = 122215.163 MIL

Execution time = 106 seconds

Memory currently in use = 280823 KB

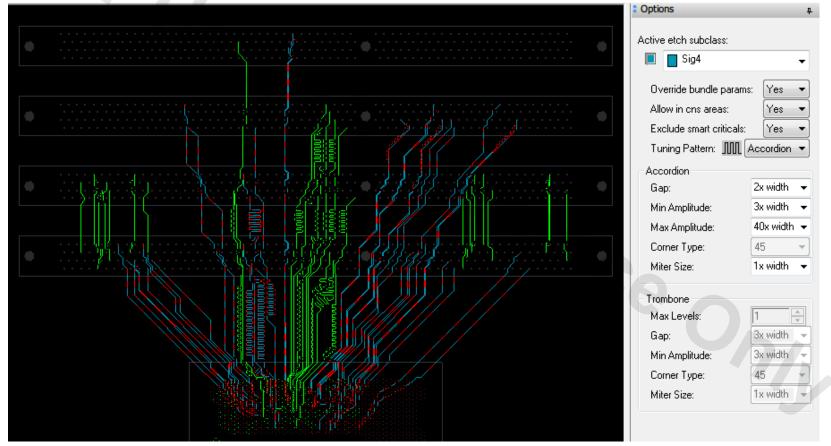

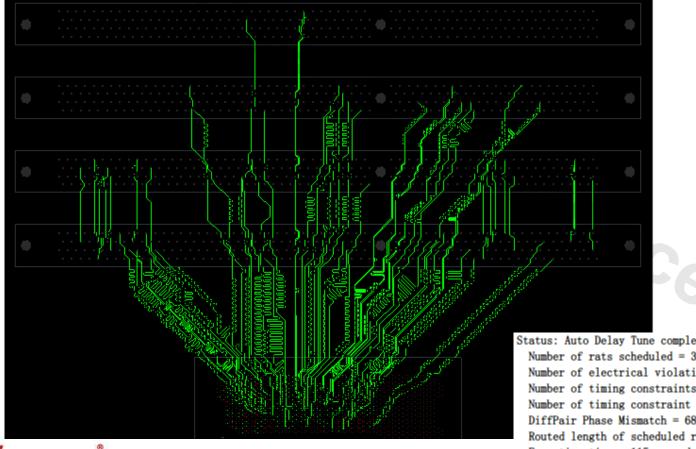

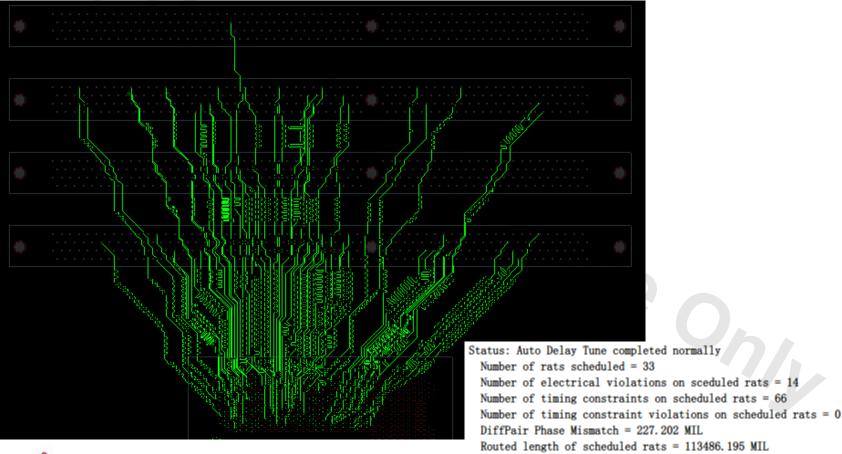

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option)

- Sig4 layer

CONFER

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig4 layer

Graser

© 2014 Graser Technology Co.,Ltd.. All rights reserved. The Graser logo a

Status: Auto Delay Tune completed normally

Number of rats scheduled = 34

Number of electrical violations on sceduled rats = 10

Number of timing constraints on scheduled rats = 68

Number of timing constraint violations on scheduled rats = 0

DiffPair Phase Mismatch = 68.032 MIL

Routed length of scheduled rats = 123287.731 MIL

Execution time = 115 seconds

Memory currently in use = 281217 KB

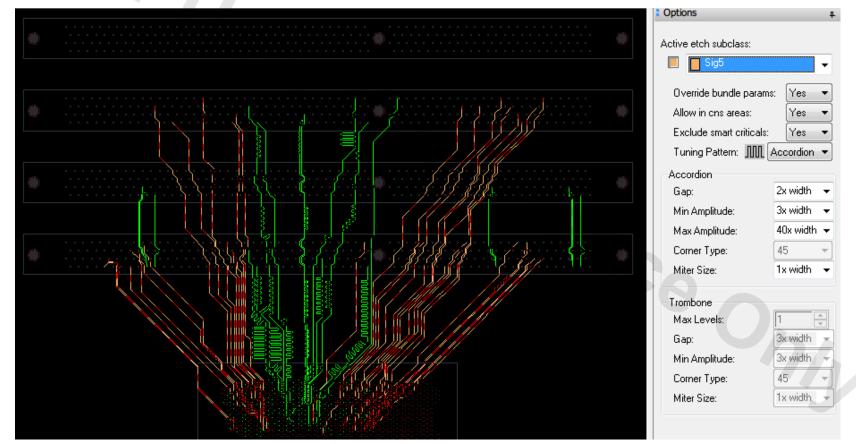

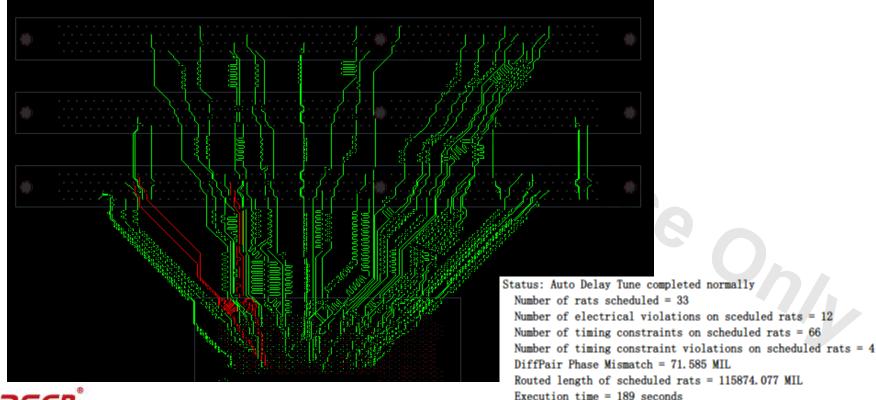

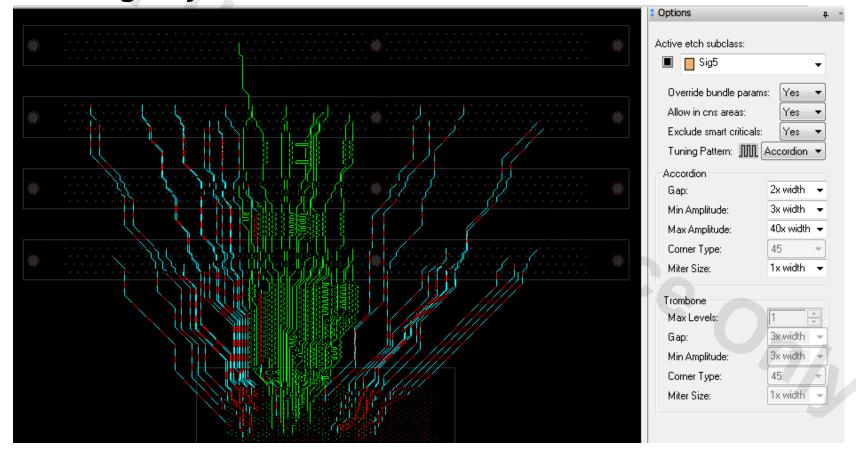

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig5 layer

CONFER

## Graser

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig5 layer

۰.....

Graser

© 2014 Graser Technology Co.,Ltd.. All rights reserved. The Graser logo an

Memory currently in use = 284152 KB

## 4<sup>th</sup> DATA (Channel A & B)

- Manual fine tuning + AiDT

- Sig5 layer

## 4<sup>th</sup> DATA (Channel A & B)

- Manual fine tuning + AiDT

- Sig5 layer

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig6 layer

CONFER

## 4<sup>th</sup> DATA (Channel A & B) - AiDT (High-Speed option) - Sig6 layer

Graser

© 2014 Graser Technology Co.,Ltd.. All rights reserved. The Graser logo an

Memory currently in use = 304297 KB

Execution time = 195 seconds

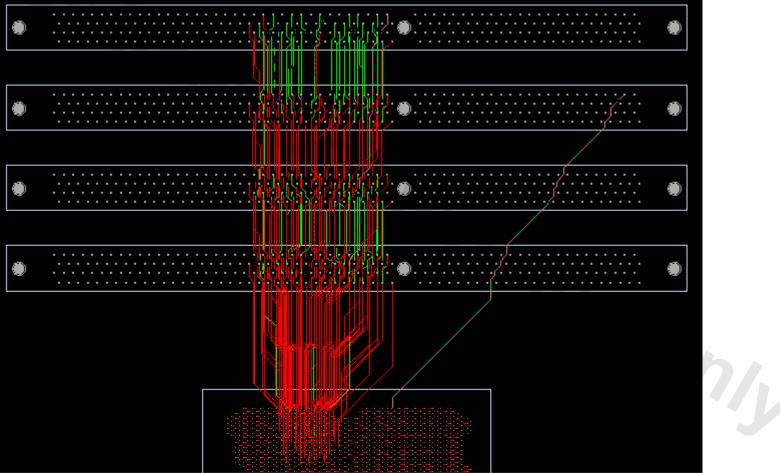

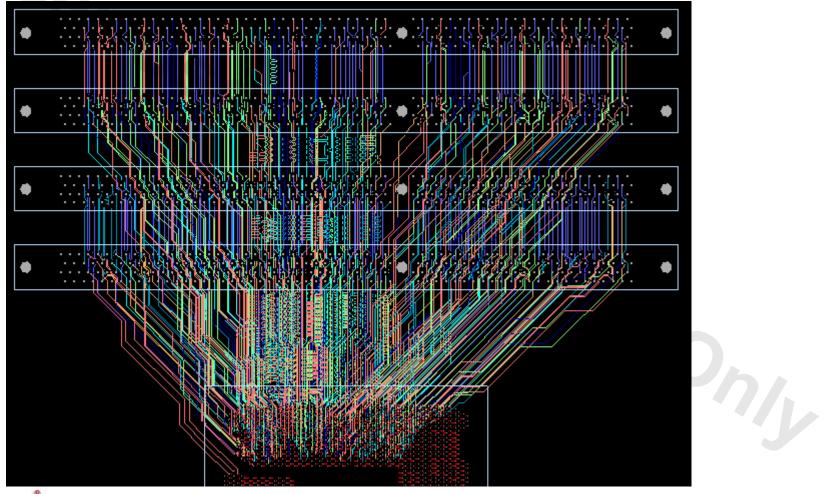

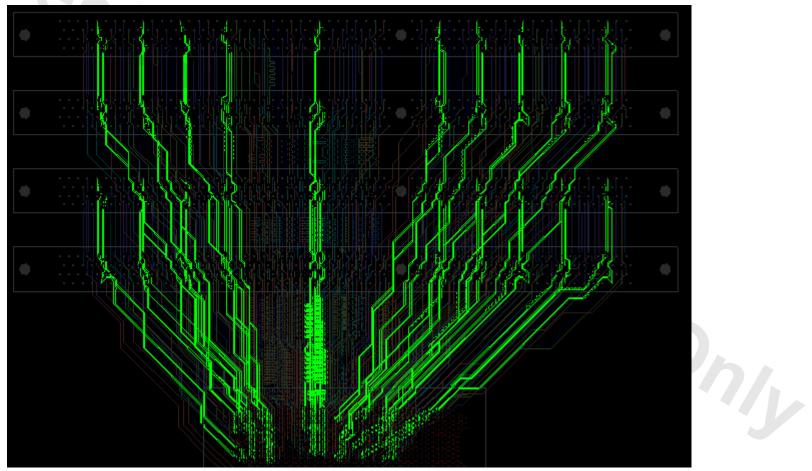

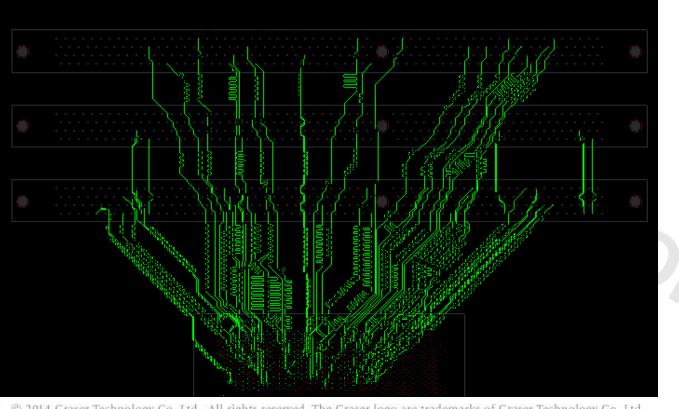

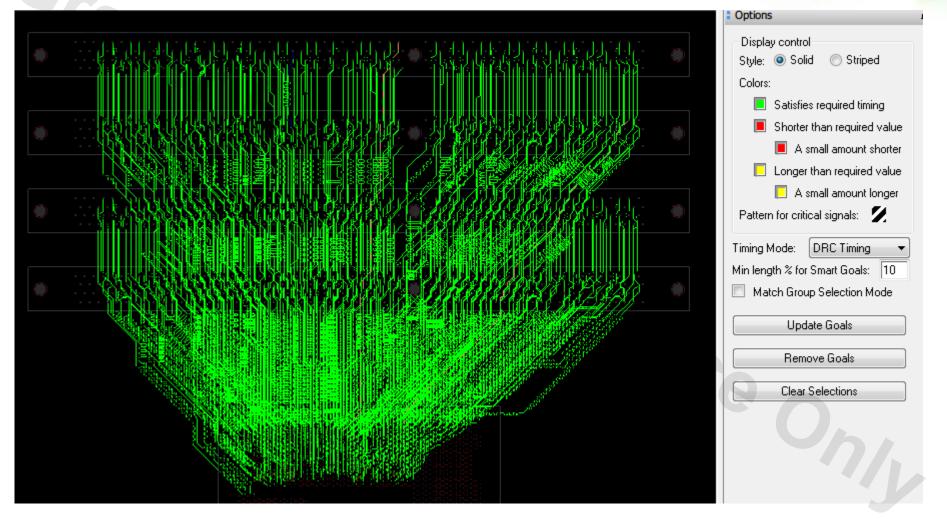

# **Routing Result**

## **Timing view**

CONFER

Graser muct

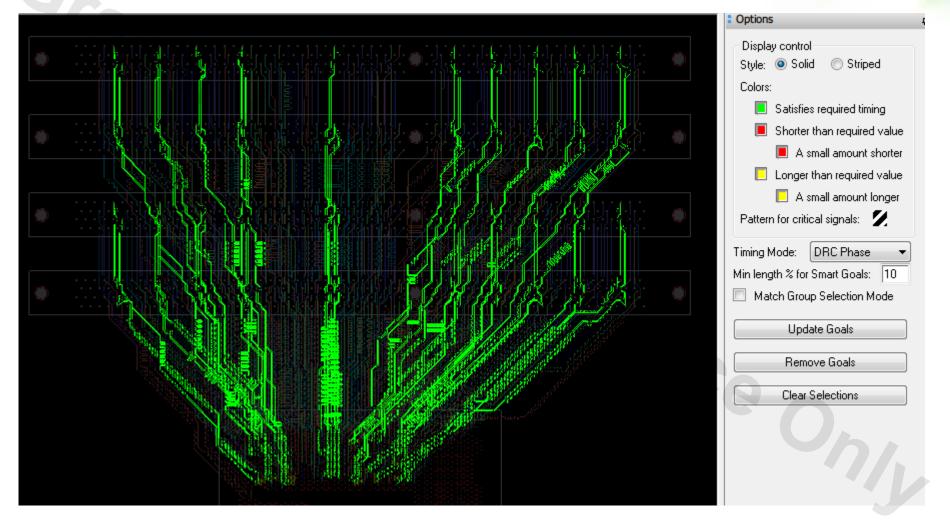

# **Routing Result**

## **Phase view**

CONFER

Graser muct

# Conclusion

## DDR (276 Nets)

- Setting Time: About 30 ~ 120 mins

- Automation Time : About 40 ~ 60 mins

- Manual Time: About 2 ~ 6 hrs

## This case : Took 5 hrs

## What else

# Graser User Chapter Three

# **Routing Flow** CONFER Grase Fan out Break out Route Optimize Plan Route

© 2014 Graser Technology Co., Ltd.. All rights reserved. The Graser logo are trademarks of Graser Technology Co., Ltd..

Graser

Graser

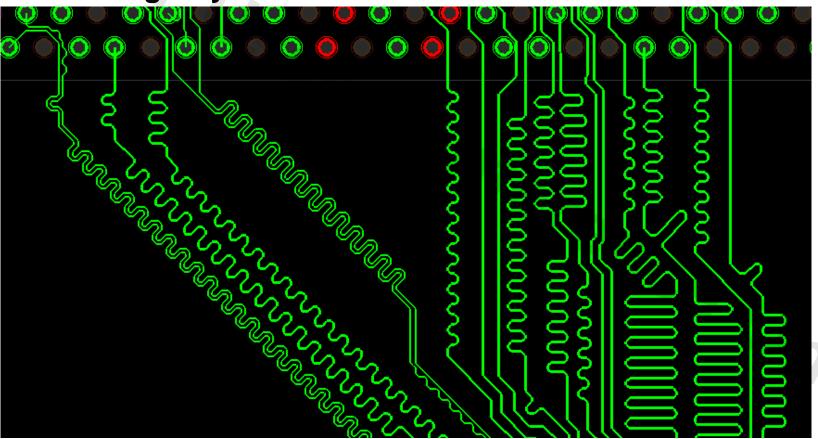

## Auto-interactive Delay Tune (AiDT – High Speed Option)

(Enhanced by QIR#4)

CONFER

Graser

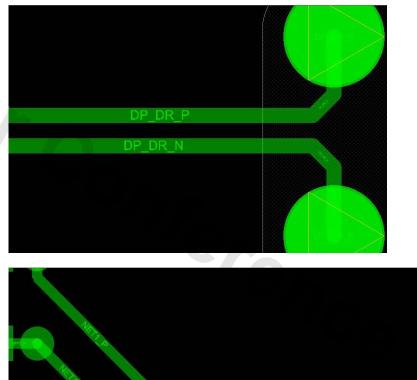

#### Auto-interactive Phase Tune (AiPT – High Speed Option) (Enhanced by QIR#4)

| Compensation Loc. Any  |       | • |

|------------------------|-------|---|

| Compensation Technique | s     |   |

| Pad Entry Shortening   | Yes   | • |

| Pad Entry Lengthening  | Yes   | • |

| Allow off-angle segs   | Yes   | • |

| Allow gather move      | Yes   | • |

| Allow Uncoupled Bumps  | No    | • |

| Height:                | 10.00 | Ŧ |

| Length:                | 10.00 | 7 |

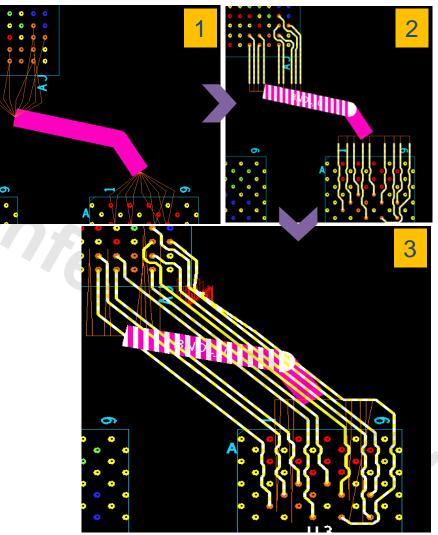

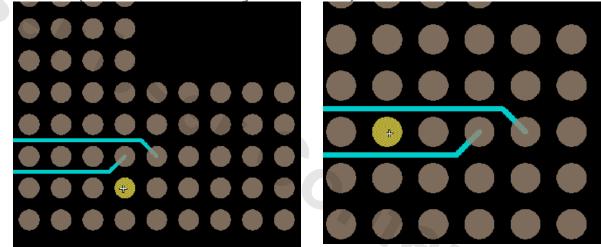

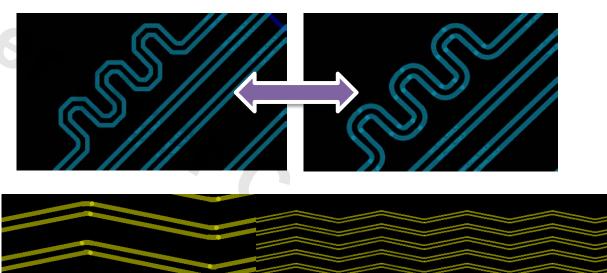

#### Auto-interactive Add Connect (AiAC – PCB Designer) Scribble Mode (Enhanced by QIR#7)

Off angle fit

Exact fit

CONFER

Univ

#### Auto-interactive Add Connect (AiAC – PCB Designer) Scribble Mode (Enhanced by QIR#7)

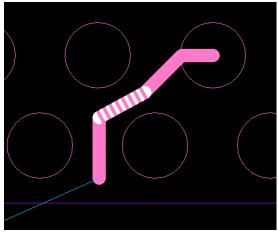

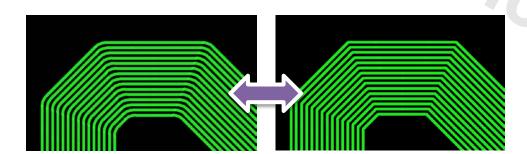

#### Auto-interactive Convert Corner (AiCC – PCB Designer)

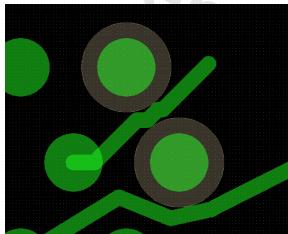

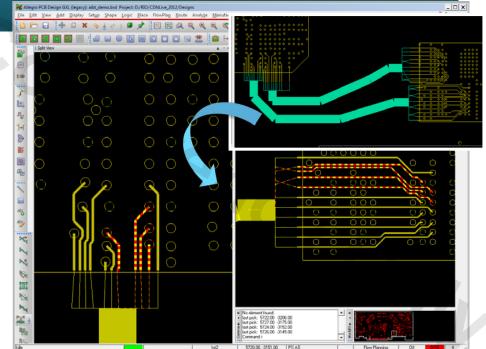

#### Auto-interactive Breakout (AiBT – Design Planning Option) (Enhanced by QIR#6)

For enterprise customers who design PCBs with high-speed interfaces such as DDR3, PCI Express 3.0, SATA, HDMI, USB 3, XAUI, SFP+

Helps you plan breakout of both components tied to an interface Reduce routing steps and improve efficiency

- Interface breakout (both ends) analysis

- Canvas-driven inputs for direction, distance, sequence

- Rat ordering and layering

Graser

## Split Views allows working on both ends of an interface zoomed-in

## Auto-interactive Trunk Routing (AiTR – Design Planning Option)

(Enhanced by QIR#7)

- New Auto-Interactive function designed to route the 'trunk' or main section of an interface

- Works with Auto-interactive **Breakout Tuning**

- Flow the Bundle

- Run Auto-Interactive Breakout on both ends

- Trunk Route follows bundle path (approximately)

- Accelerates time to breakout and route an interface