# OrCAD Sigrity ERC

Josh Moore – Product Management Director Cadence OrCAD Solutions

# Cadence Sigrity – Industry-leading SI / PI Solution

- Product of choice for power and signal integrity analysis

- Integration with full wave 3D EM solver

- Layout-based frequencydomain SI / PI simulation

- Highly accurate modeling of PCB structures

- Single-ended and mixed-mode results and post-processing

- Unique capability for ensuring accuracy down to DC

- Targeted workflows to streamline setup operations

#### Frequency domain SI, PI and EMC

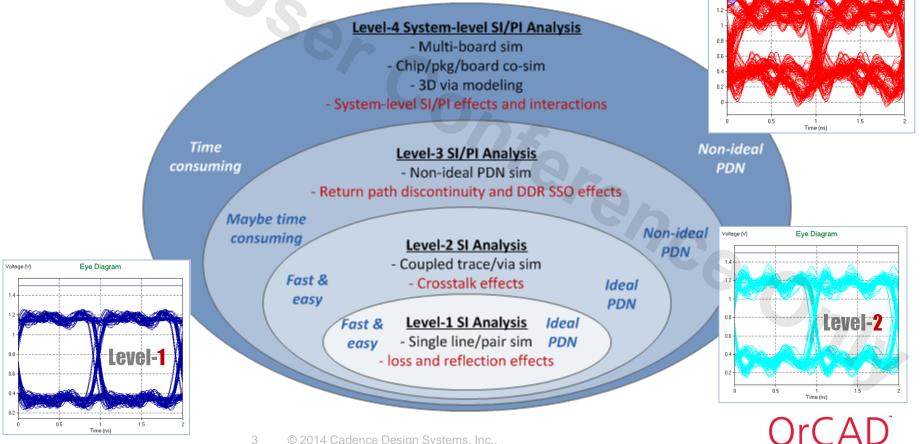

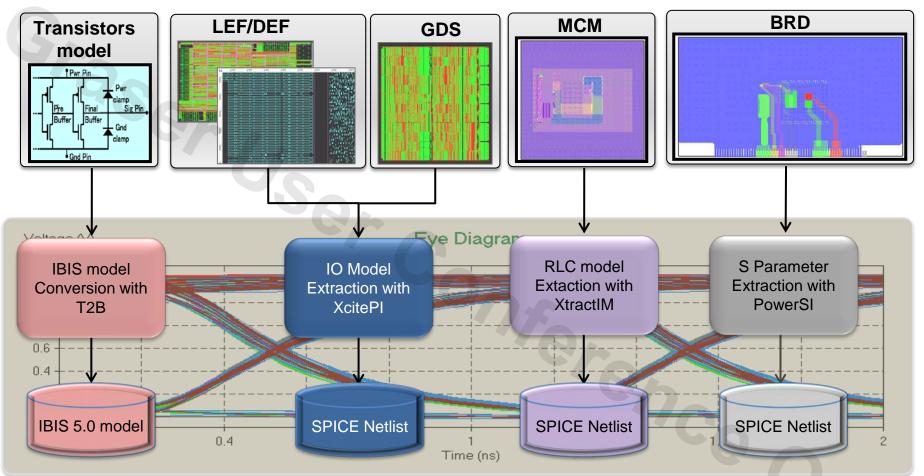

### Different SI / PI / EMI Levels for Different Needs

Voltage (V)

Eye Diagram

CADENCE PCR SOLUTION

evel.

- Simulations and analysis can be done at four levels

- Based on considerations of trace / via couplings, non-ideal PDN, etc.

- Both layout-based and model-based analysis

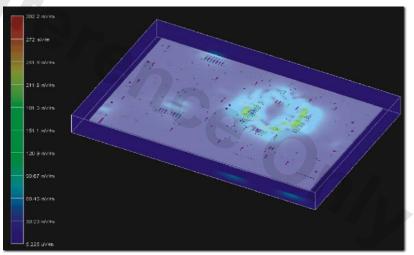

### Layout-based, Time-domain SI / PI Simulation

- SPEED200<sup>™</sup> is industry's only layout-based, timedomain SI / PI solution

- Five workflows for SI / PI analysis from level 1 to 3

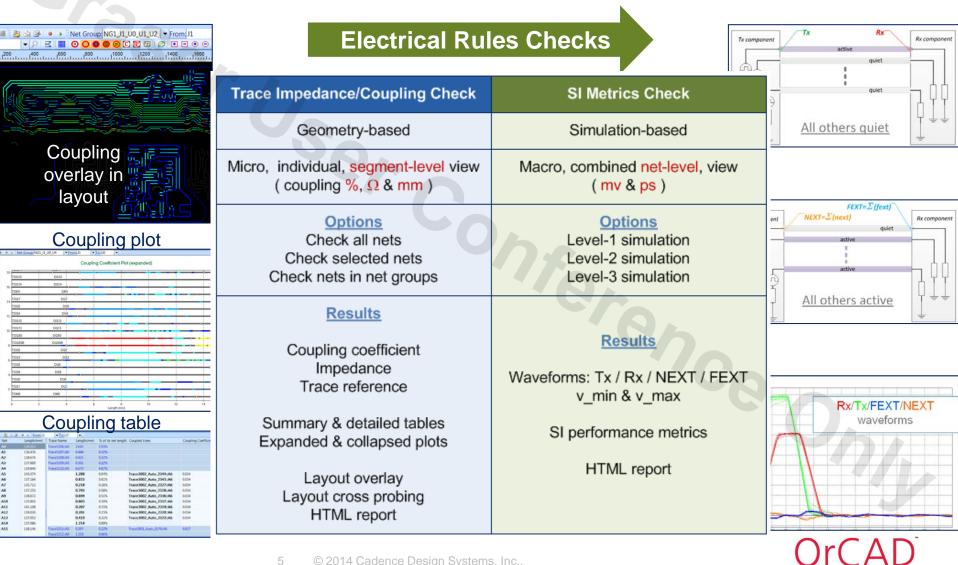

| <u>Workflow 1</u><br>General SI<br>Simulation                                                         | <u>Workflow 2</u><br>Trace Impedance/<br>Coupling Check                                                                                                                              | <u>Workflow 3</u><br>SI Performance<br>Metrics Check                                                                                                                      | <u>Workflow 4</u><br>DDR Simulation                                                                                                                       | <u>Workflow 5</u><br>Time-domain PDN<br>Simulation                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mainstream SI<br>L1/L2 for fast sim<br>Easy to setup;<br>Sim runs fast<br>Waveforms &<br>measurements | Geometry based<br>Trace impedance,<br>coupling &<br>reference check<br>for entire board or<br>net groups<br>Results tables;<br>Results plots;<br>Layout overlay;<br>Layout x-probing | Simulation based<br>L1/L2 for fast sim<br>L3 for non-ideal PDN<br>Loss, reflection,<br>xtalk check,<br>typically by net<br>groups<br>Waveforms;<br>Xtalk v_max &<br>v_min | Layout-based<br>DDR simulation<br>L1/L2 for fast sim<br>L3 for SSO<br>No s-parameter<br>model needed for<br>on-board DRAMs<br>Waveforms &<br>measurements | Layout-based TD<br>PDN sim<br>PDN chip-pkg-<br>board co-sim with<br>-Voltus die mode<br>- XcitePI IO model<br>with die grid<br>Voltage / current<br>distributions;<br>dynamic noise<br>propagation |

### Geometry- and Simulation-based Layout Checks

CADENCE PCB SOLUTION

# SI Barriers for PCB Designers

### **Complex Flow for Simulation and Verification**

Comprehensive SI / PI simulation and analysis relies on experienced, well trained engineers with sophisticated tools

### Common SI Analysis Needs to be Simple

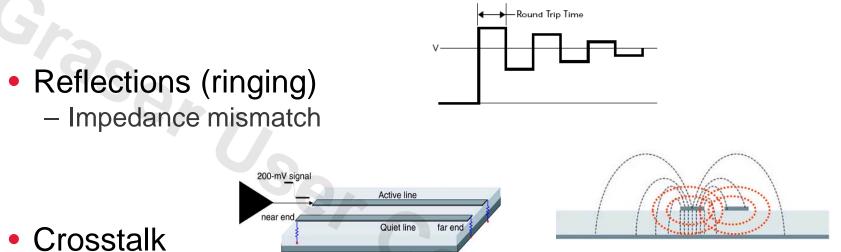

- - Electromagnetic coupling between adjacent signal lines

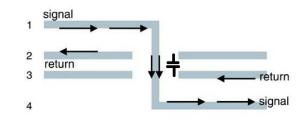

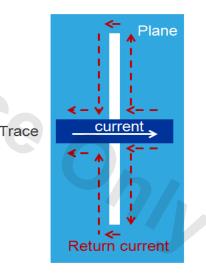

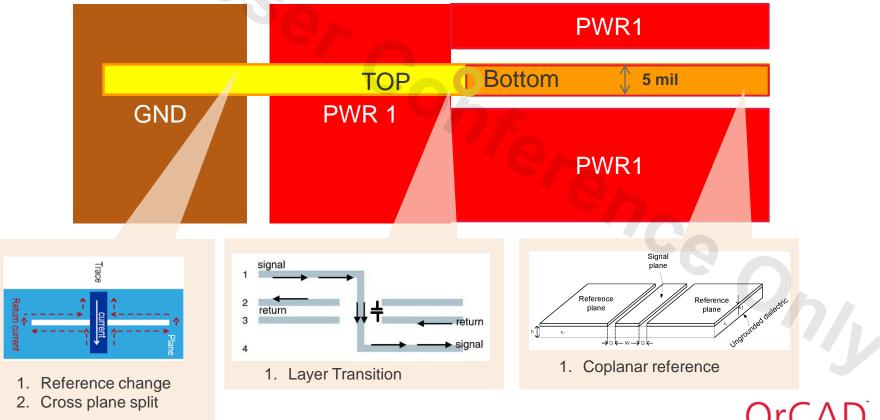

- Return path discontinuity

- Layer transitions or plane split crosses

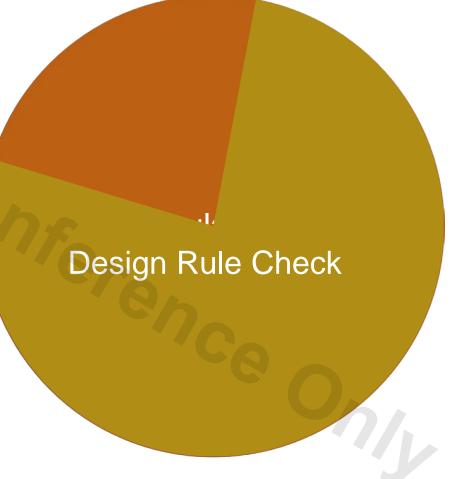

### Simulation and Design Rule Check

- Ideally, designs should be 100% driven and validated by simulation

- Typically, pre-layout simulation results drive design rules

- Only small portion covered by simulation

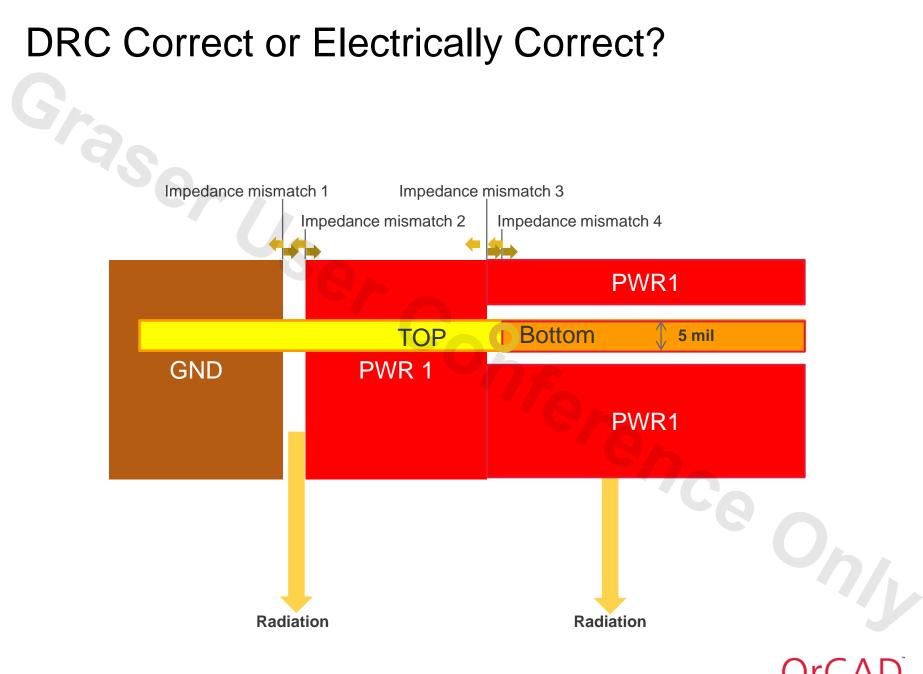

- PCB DRCs usually contain only dimension information such as length, width, distance, spacing, etc.

- What do constraints / DRCs forget to tell you?

Simple design rule checks for dimension will not validate electrical characteristics

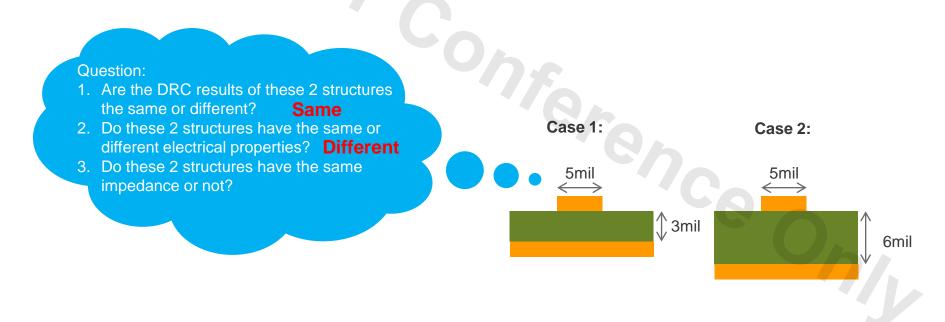

- Pre-layout simulation, defines a trace width to be 5 mils for a target impedance

- The following routed trace results in **no DRC** violation

CADENCE PCR SOLUTION

CADENCE PCB SOLUTIONS

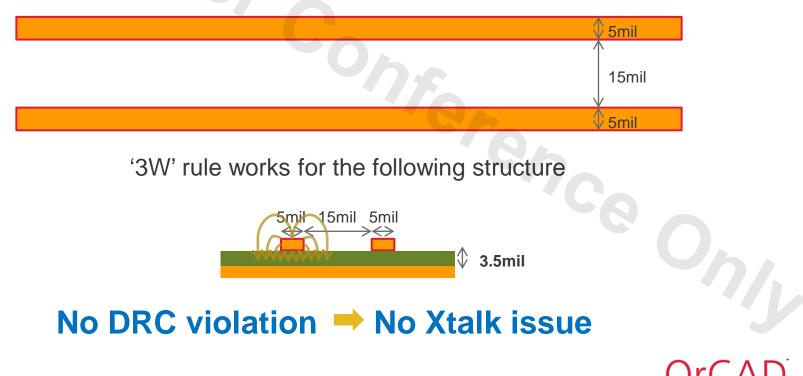

- To minimize crosstalk, many follow the '3W' rule set the spacing between critical adjacent traces to 3 times the width of the trace

- The following routed trace results in no DRC violation

What if the stack-up looks like the following, will '3W' rule still work?

- DRCs only validate MINIMUM, PHYSICAL requirements of design constraints

- Do no DRCs mean a good, quality design?

- Can PCB designers identify and address signal quality issues?

How difficult is it to setup? Is it easy to use? Do I have to be an SI expert? Is it expensive?

## OrCAD Sigrity Technology for PCB Designers

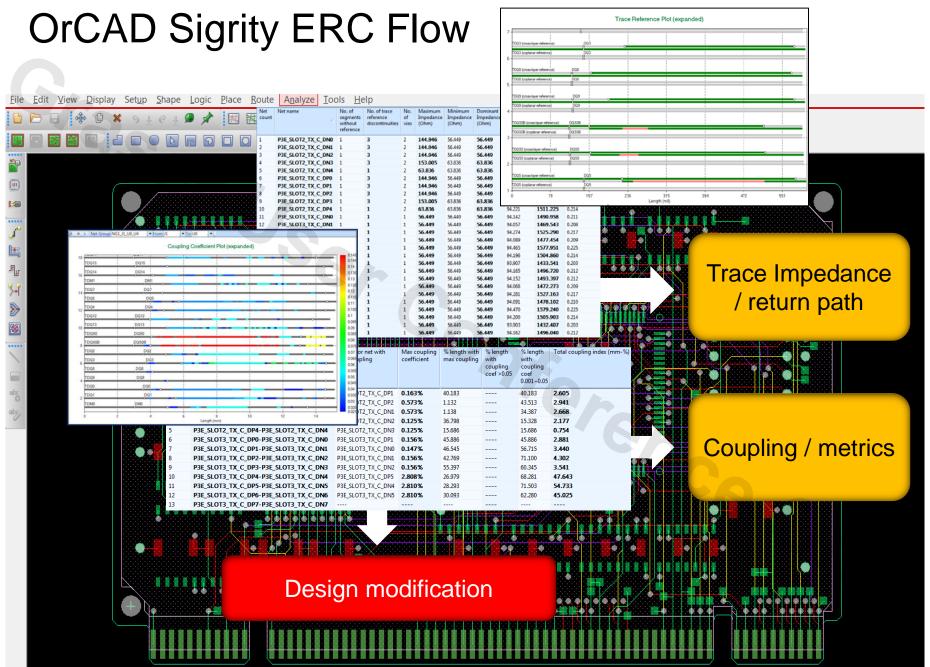

### Electrical Rule Checks with OrCAD Sigrity ERC

- ERCs are better than DRCs for signal quality validation – Go beyond MINIMUM, GEOMETRY-BASED constraint validation

- Easy to use, minimal setup

- PCB designers can identify and address signal quality issues

### OrCAD Sigrity ERC (coming 2015 / 17.0 & QIRs)

- No complex modeling / setup required

- Electrical checks include

- SI Metrics (Level 1 & Level 2)

- Differential Pair Serial Link Screening

- Trace impedance check

- Trace return path check

- Via return path check

- Trace coupling check

- Net coupling check

- Additional future checks

- OrCAD FloorPlanner

- Place and route edits only

- Cross-probe (pan / highlight / zoom) between analysis & layout

© 2014 Cauence Design Systems, inc.

CADENCE PCB SOLUTIONS

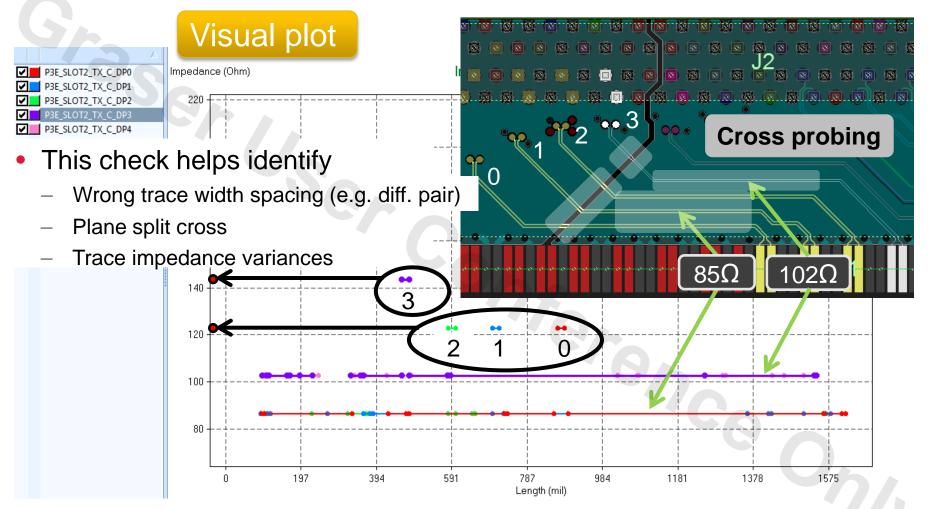

### Trace Impedance Check

Visually or tabular results for trace impedance check shows trace segment(s) mismatch vs. target impedance

### Trace Impedance Check

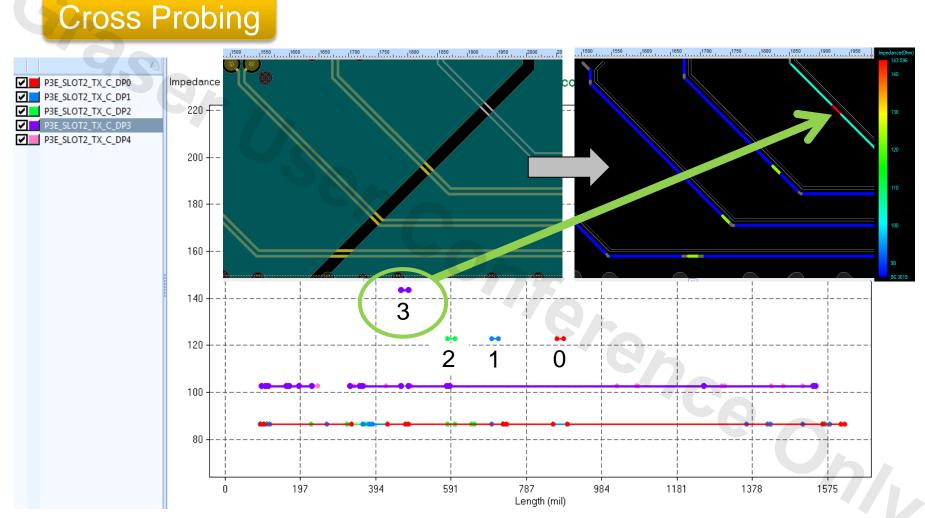

Cross probing allows issues to be quickly identified

### Trace Impedance Check

#### Tabular Results

| Net<br>count                                                      | Net name                                                           | No. of<br>segments<br>without<br>reference | No. of trace<br>reference<br>discontinuities | No.<br>of<br>vias | Maximum<br>Impedance<br>(Ohm) | Minimum<br>Impedance<br>(Ohm) | Dominant<br>Impedance<br>(Ohm) | Dominant<br>Imp Length<br>(%) | Trace total<br>length (mil) | Trace delay(ns) |

|-------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------|----------------------------------------------|-------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------|-----------------------------|-----------------|

| 1                                                                 | P3E_SLOT2_TX_C_DN0                                                 | 1                                          | 3                                            | 2                 | 144.946                       | 56.449                        | 56.449                         | 92.921                        | 1633.158                    | 0.233           |

| 2                                                                 | P3E_SLOT2_TX_C_DN1                                                 | 1                                          | 3                                            | 2                 | 144.946                       | 56.449                        | 56.449                         | 93.168                        | 1583.722                    | 0.225           |

| 3                                                                 | P3E_SLOT2_TX_C_DN2                                                 | 1                                          | 3                                            | 2                 | 144.946                       | 56.449                        | 56.449                         | 93.186                        | 1575.168                    | 0.224           |

| 4                                                                 | P3E_SLOT2_TX_C_DN3                                                 | 1                                          | 3                                            | 2                 | 153.005                       | 63.836                        | 63.836                         | 93.074                        | 1549.678                    | 0.220           |

| 5                                                                 | P3E_SLOT2_TX_C_DN4                                                 | 1                                          | 1                                            | 2                 | 63.836                        | 63.836                        | 63.836                         | 94.228                        | 1513.121                    | 0.214           |

| 6                                                                 | P3E_SLOT2_TX_C_DP0                                                 | 1                                          | 3                                            | 2                 | 144.946                       | 56.449                        | 56.449                         | 92.923                        | 1633.643                    | 0.233           |

| 7                                                                 | P3E_SLOT2_TX_C_DP1                                                 | 1                                          | 3                                            | 2                 | 144.946                       | 56.449                        | 56.449                         | 93.221                        | 1583.404                    | 0.225           |

| 8                                                                 | P3E_SLOT2_TX_C_DP2                                                 | 1                                          | 3                                            | 2                 | 144.946                       | 56.449                        | 56.449                         | 93.184                        | 1574.865                    | 0.224           |

| 9                                                                 | P3E_SLOT2_TX_C_DP3                                                 | 1                                          | 3                                            | 2                 | 153.005                       | 63.836                        | 63.836                         | 93.059                        | 1546.528                    | 0.219           |

| 10                                                                | P3E_SLOT2_TX_C_DP4                                                 | 1                                          | 1                                            | 2                 | 63.836                        | 63.836                        | 63.836                         | 94.221                        | 1511.225                    | 0.214           |

| 11                                                                | P3E_SLOT3_TX_C_DN0                                                 | 1                                          | 1                                            | 1                 | 56.449                        | 56.449                        | 56.449                         | 94.142                        | 1490.958                    | 0.211           |

|                                                                   |                                                                    |                                            |                                              |                   |                               |                               |                                |                               | 1100 513                    | 0.208           |

| Cross plane split?                                                |                                                                    |                                            |                                              |                   |                               |                               |                                |                               | 0.217                       |                 |

|                                                                   |                                                                    |                                            |                                              |                   |                               |                               |                                |                               |                             | 0.209           |

|                                                                   | Any trace comment microstab? Croce place colit?                    |                                            |                                              |                   |                               |                               |                                |                               |                             | 0.225           |

| • /                                                               | <ul> <li>Any trace segment mismatch? Cross plane split?</li> </ul> |                                            |                                              |                   |                               |                               |                                |                               |                             | 0.214           |

| _                                                                 |                                                                    |                                            |                                              |                   |                               |                               |                                |                               |                             | 0.203           |

| •                                                                 | <ul> <li>Too much breakout neck length?</li> </ul>                 |                                            |                                              |                   |                               |                               |                                |                               |                             | 0.212           |

|                                                                   |                                                                    |                                            |                                              |                   |                               |                               |                                |                               |                             | 0.212           |

| <ul> <li>Too much MS/SL routing difference in a group?</li> </ul> |                                                                    |                                            |                                              |                   |                               |                               |                                | 0.209                         |                             |                 |

| The much wo/or routing unreferice in a group?                     |                                                                    |                                            |                                              |                   |                               |                               |                                | 0.217                         |                             |                 |

|                                                                   |                                                                    |                                            |                                              |                   |                               |                               |                                |                               |                             | 0.210           |

|                                                                   | The same trace length means the same trace delay?                  |                                            |                                              |                   |                               |                               |                                | 0.225                         |                             |                 |

|                                                                   |                                                                    |                                            |                                              |                   |                               |                               |                                |                               | 0.214                       |                 |

| <ul> <li>Routing on MS/SL has different trace delay.</li> </ul>   |                                                                    |                                            |                                              |                   |                               |                               | 0.203                          |                               |                             |                 |

|                                                                   |                                                                    |                                            |                                              |                   |                               |                               |                                | 0.212                         |                             |                 |

CADENCE PCB SOLUTIONS

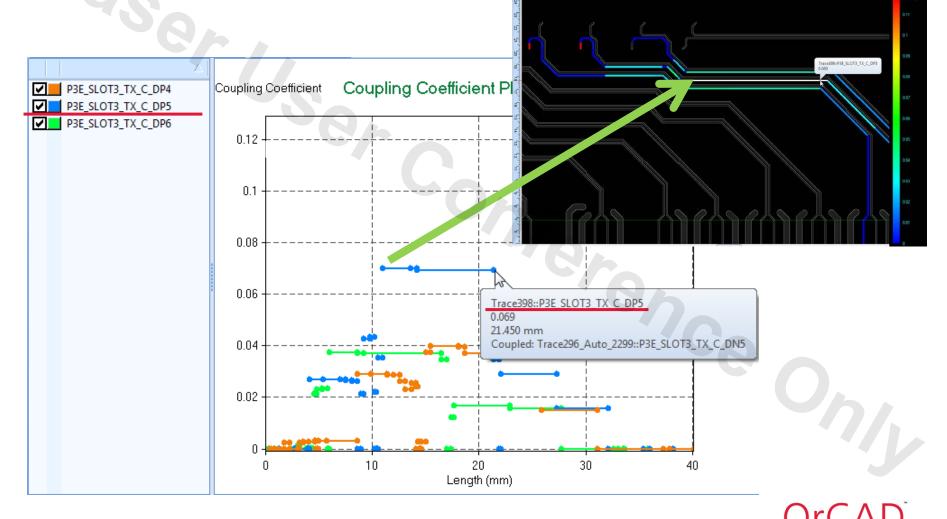

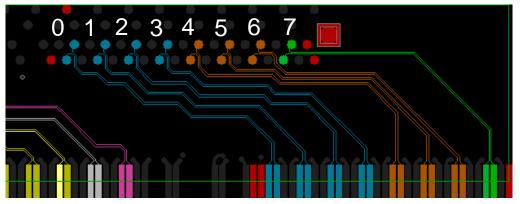

### Trace Coupling Check

#### Cross probing helps to easily resolve issues

105 106 107 108 109 110 111 112 113

CADENCE PCB SOLUTION

### Trace Coupling Check

| Net<br>count | Net name                              | Aggressor net with<br>max coupling | Max coupling<br>coefficient | % length with<br>max coupling | % length<br>with<br>coupling<br>coef >0.05 | % length<br>with<br>coupling<br>coef<br>0.001~0.05 | Total coupling index (mm-%) |

|--------------|---------------------------------------|------------------------------------|-----------------------------|-------------------------------|--------------------------------------------|----------------------------------------------------|-----------------------------|

| 1            | P3E_SLOT2_TX_C_DP0-P3E_SLOT2_TX_C_DN0 | P3E_SLOT2_TX_C_DP1                 | 0.163%                      | 40.183                        |                                            | 40.183                                             | 2.605                       |

| 2            | P3E_SLOT2_TX_C_DP1-P3E_SLOT2_TX_C_DN1 | P3E_SLOT2_TX_C_DP2                 | 0.573%                      | 1.132                         |                                            | 43.513                                             | 2.941                       |

| 3            | P3E_SLOT2_TX_C_DP2-P3E_SLOT2_TX_C_DN2 | P3E_SLOT2_TX_C_DN1                 | 0.573%                      | 1.138                         |                                            | 34.387                                             | 2.668                       |

| 4            | P3E_SLOT2_TX_C_DP3-P3E_SLOT2_TX_C_DN3 | P3E_SLOT2_TX_C_DN2                 | 0.1257                      | 36.798                        |                                            | 15.328                                             | 2.177                       |

| 5            | P3E_SLOT2_TX_C_DP4-P3E_SLOT2_TX_C_DN4 | P3E_SLOT2_TX_C_DN3                 | 0.125%                      | 15.686                        |                                            | 15.686                                             | 0.754                       |

| 6            | P3E_SLOT3_TX_C_DP0-P3E_SLOT3_TX_C_DN0 | P3E_SLOT3_TX_C_DP1                 | 0.156%                      | 45.886                        |                                            | 45.886                                             | 2.881                       |

| 7            | P3E_SLOT3_TX_C_DP1-P3E_SLOT3_TX_C_DN1 | P3E_SLOT3_TX_C_DN0                 | 0.147%                      | 46.545                        |                                            | 56.715                                             | 3.440                       |

| 8            | P3E_SLOT3_TX_C_DP2-P3E_SLOT3_TX_C_DN2 | P3E_SLOT3_TX_C_DN1                 | 0.156%                      | 42.769                        |                                            | 71.100                                             | 4.302                       |

| 9            | P3E SLOT3 TX C DP3-P3E SLOT3 TX C DN3 | P3E SLOT3 TX C DN2                 | 0.156%                      | 55.397                        |                                            | 60.345                                             | 3.541                       |

| 10           | P3E_SLOT3_TX_C_DP4-P3E_SLOT3_TX_C_DN4 | P3E_SLOT3_TX_C_DP5                 | 2.808%                      | 26.979                        |                                            | 68.281                                             | 47.643                      |

| 11           | P3E_SLOT3_TX_C_DP5-P3E_SLOT3_TX_C_DN5 | P3E_SLOT3_TX_C_DN4                 | 2.810%                      | 28.293                        |                                            | 71.503                                             | 54.733                      |

| 12           | P3E SLOT3 TX C DP6-P3E SLOT3 TX C DN6 | P3E SLOT3 TX C DN5                 | 2.810%                      | 30.093                        |                                            | 62.280                                             | 45.025                      |

| 13           | P3E_SLOT3_TX_C_DP7-P3E_SLOT3_TX_C_DN7 |                                    |                             |                               |                                            |                                                    |                             |

- Tight coupling pairs

- Max coupling aggressor

- Dangerous vs. safe coupling

→18X (= 2.81% / 0.156%)

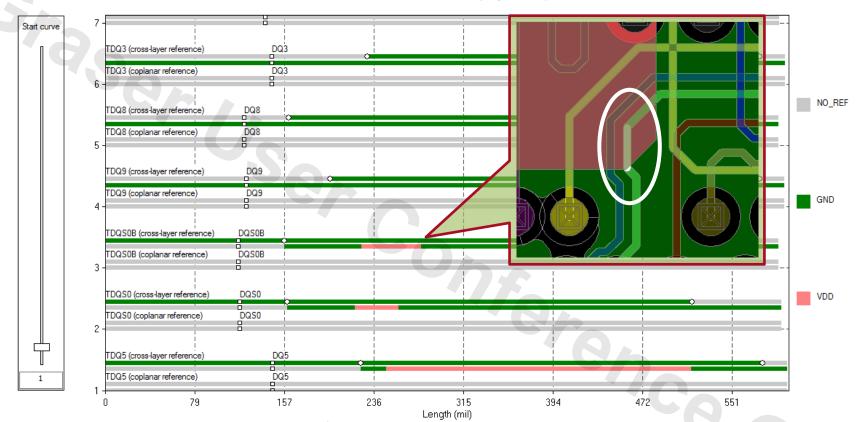

### **Trace Reference Check**

Trace Reference Plot (expanded)

- <u>Trace cross layer reference</u> shows the net names for the reference plane shapes directly above and below the corresponding trace segment

- <u>Trace coplanar reference</u> shows the net names for the reference plane shapes next to the corresponding trace segment on the same layer

### Summary / Benefits

ERCs are better than DRCs for signal quality validation

Identify issues geometry-based DRCs miss

- OrCAD Sigrity ERC specifically designed for PCB designers leveraging industry-leading Cadence Sigrity technology

- Easy to use, minimal setup

- Cross-probing

- Actionable results to identify and quickly address signal quality issues

### CADENCE PCB SOLUTIONS

©2014 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, Sigrity, and OrCAD are registered trademarks and the OrCAD logo is a trademark of Cadence Design Systems, Inc. in the United States and other countries. All other trademarks are the property of their respective owners.

тм