# Simple Transistor to Behavior Model Conversion

Eric Chen 13/Aug/2013

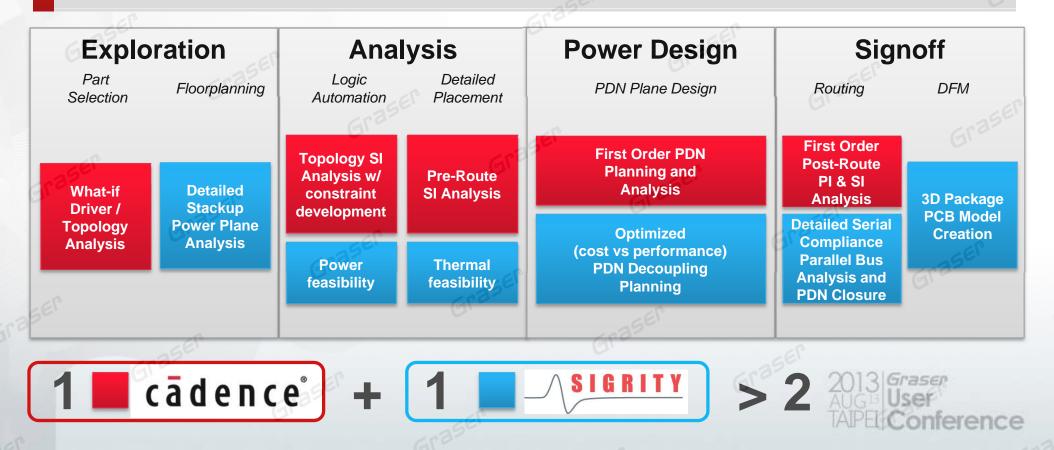

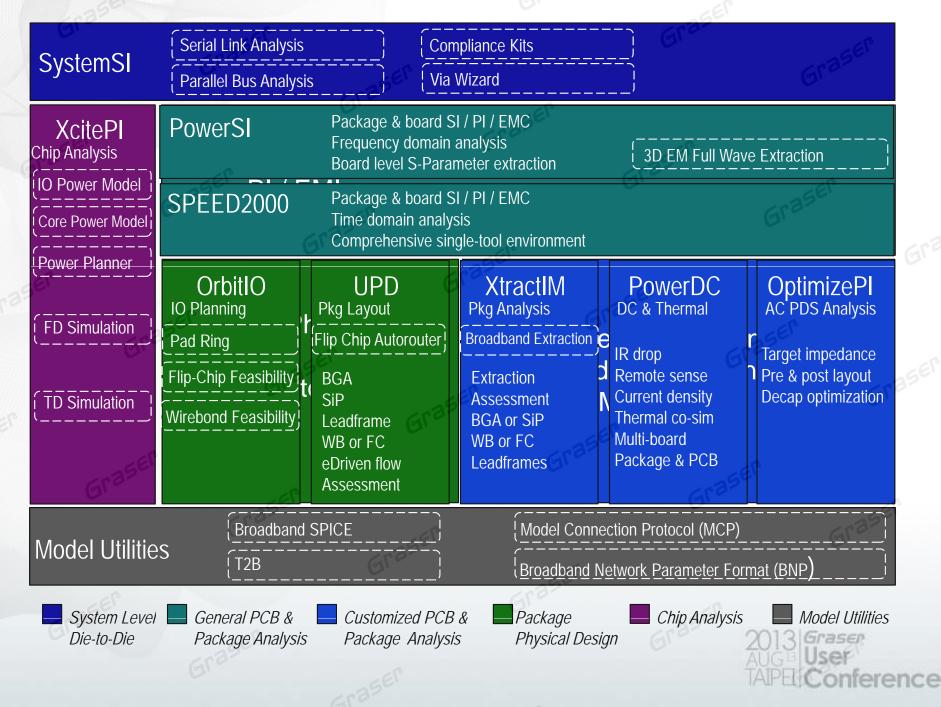

# Allegro / Virtuoso / EPS with Sigrity

- Comprehensive Front-to-Back Solution

- Better Together

Single vendor Front-to-Back flow: design, verification, analysis, and compliance closure For emerging gigabit design challenges Focus on High-end Consumer and Data-center Infrastructure verticals Integrated 3D solvers for chip, package and board

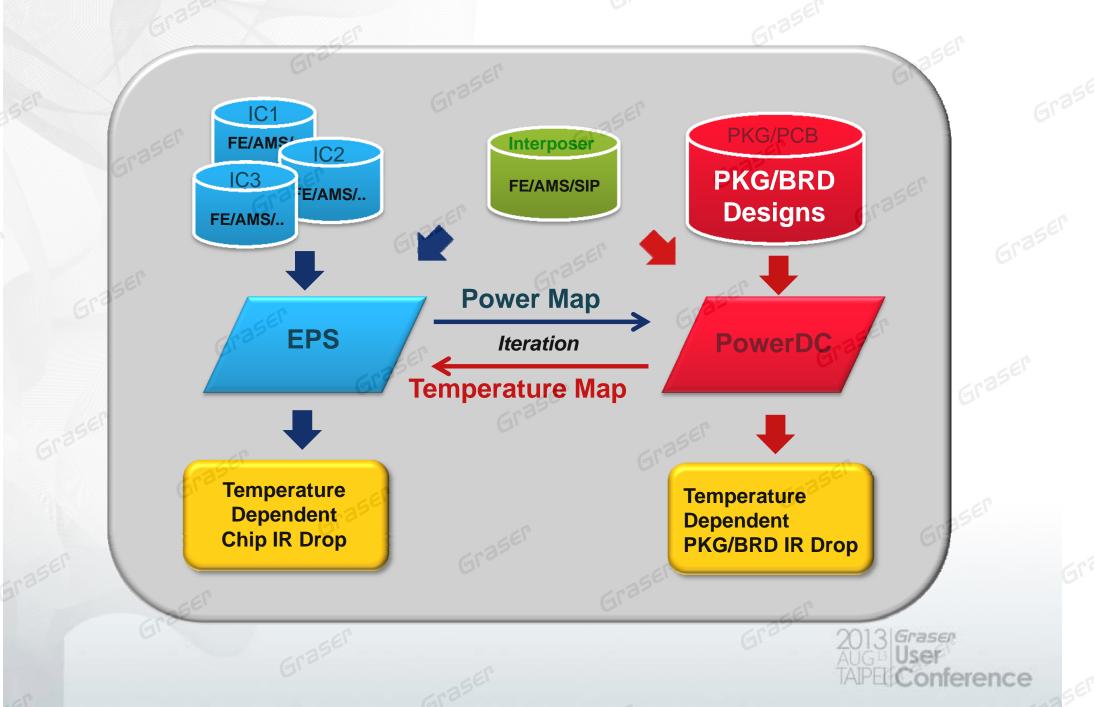

# Digital IC - Sigrity EPS + PowerDC

# Overview

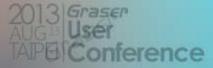

- EPS + PowerDC → Electrical/Thermal Co-Simulation of 3D IC

- EPS generates temperature and location dependent power maps

- PowerDC computes detailed temperature distribution of dies, interposer, package, and board

- Physics Based 3D Thermal Simulation

- Each and every vias, wires, balls, and bump are modeled explicitly

- Considers both Joule heating and component heating

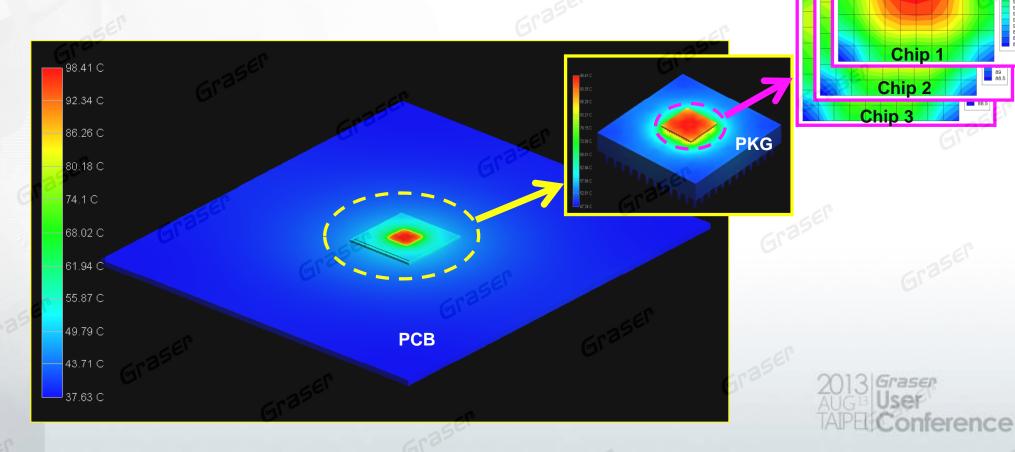

# **Electrical-Thermal Co-Simulation**

Leakage Power Temperature

- Thermal Runaway

- Positive feedback and interaction among chip's temperature, leakage and power dissipation

- Temperature-dependent EMIR failures

- Physics Based 3D Thermal Simulation in "EPS + Sigrity PowerDC"

- EPS generates temperature and location dependent "Power Map" file

- PowerDC computes detailed temperature distribution for Chip-PKG-PCB and sends back "Temperature Map" file to EPS for more iteration and convergence

- Thermal view is available in 2D/3D for interposer and full 3DIC systems.

# **CoWoS Thermal Simulation Flow**

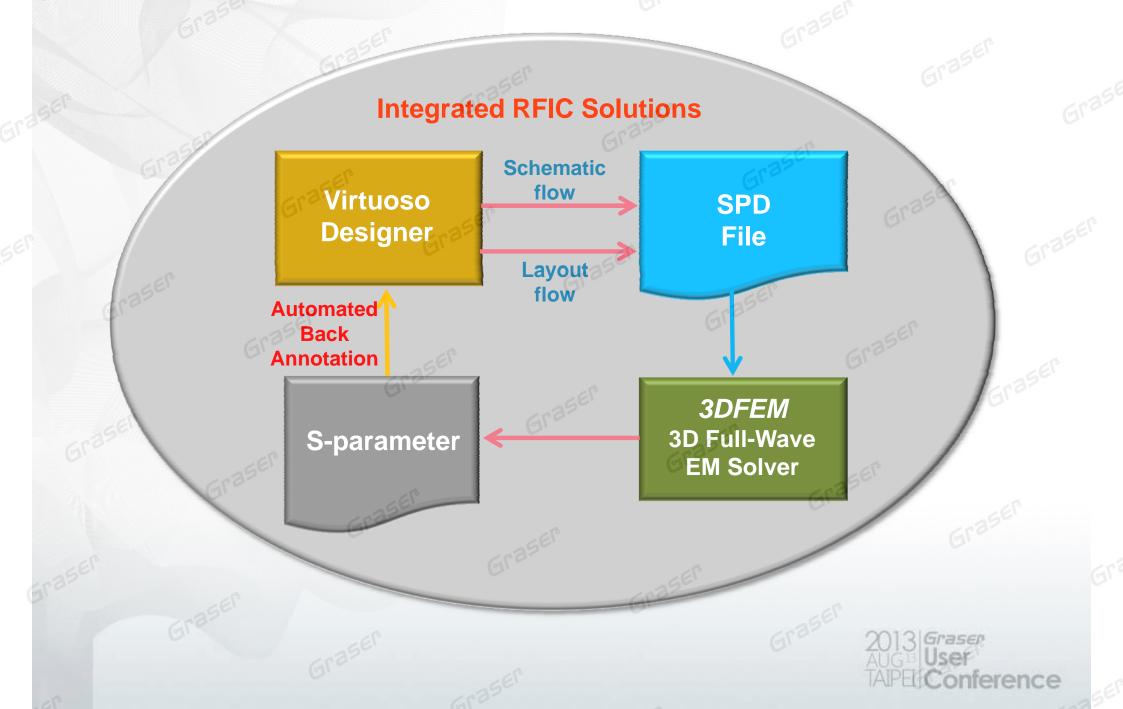

# Custom IC - Sigrity Virtuoso + PowerDC

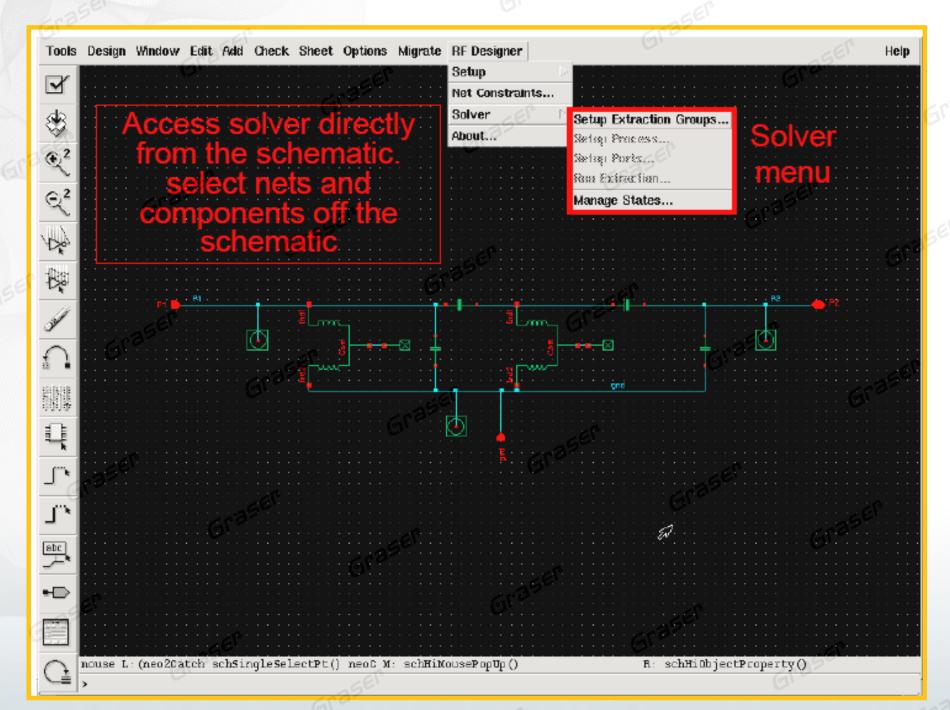

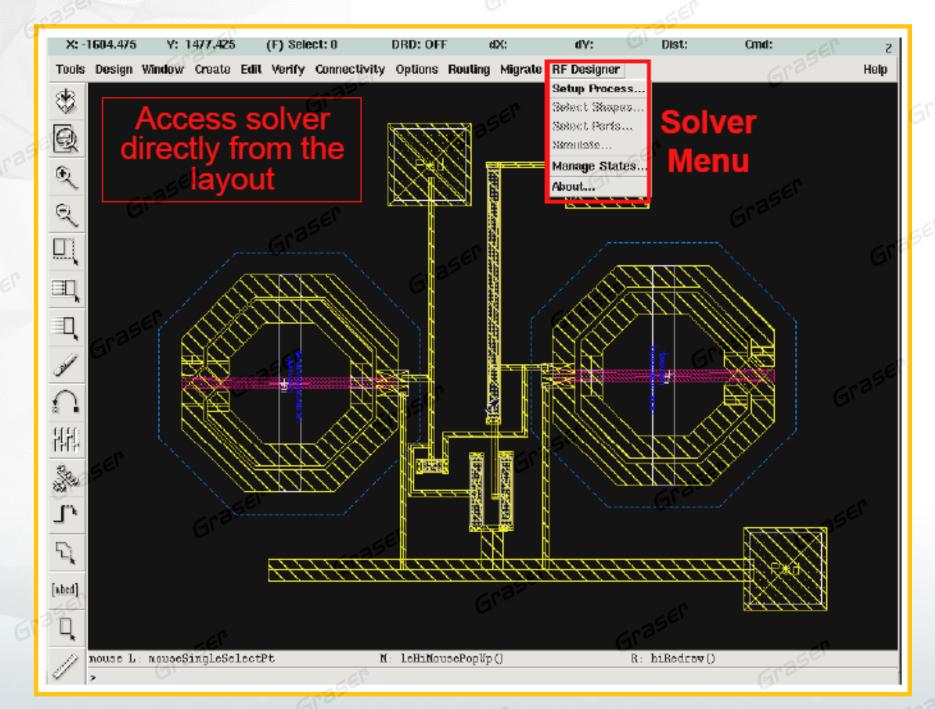

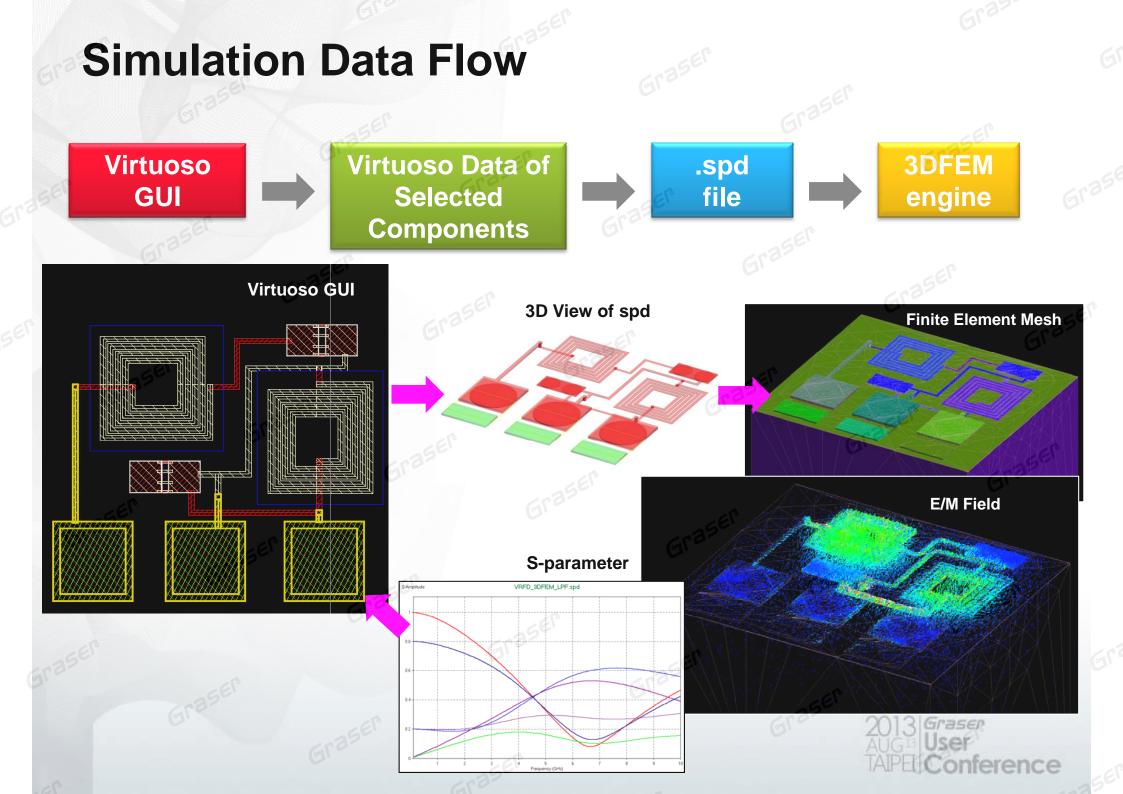

# **Seamless Integration**

### **Schematic Flow**

### **Layout Flow**

C.P.

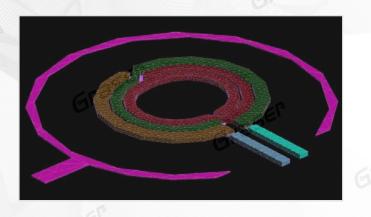

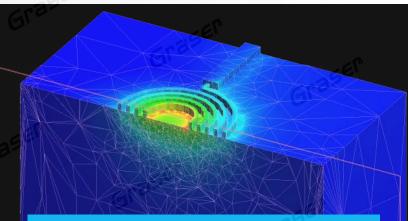

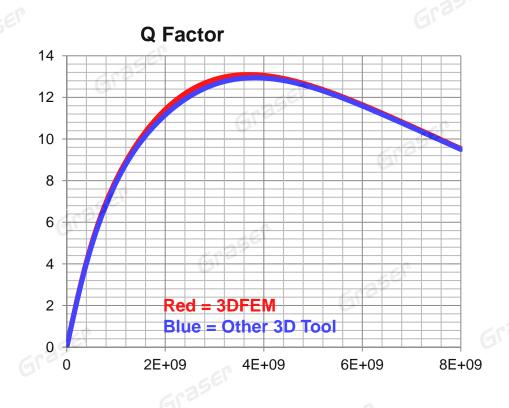

### Accuracy and Performance Benchmark RFIC Spiral Inductor

#### Adaptive Meshing →

- Denser Meshes in High Field Regions

- Coarser Meshes in Low Field Regions

Even with a slower computer, 3DFEM's speed is still >4X of the other 3D tool ✓ 3DFEM : i5-2520, 2-core

Other Tool: Xenon-5620, 8-core

2013 Graser AUG D User TAIPEL Conference

# **Cadence Sigrity Products**

# Simple Transistor to Behavior Model Conversion

# **T2B Overview**

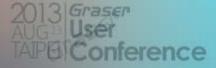

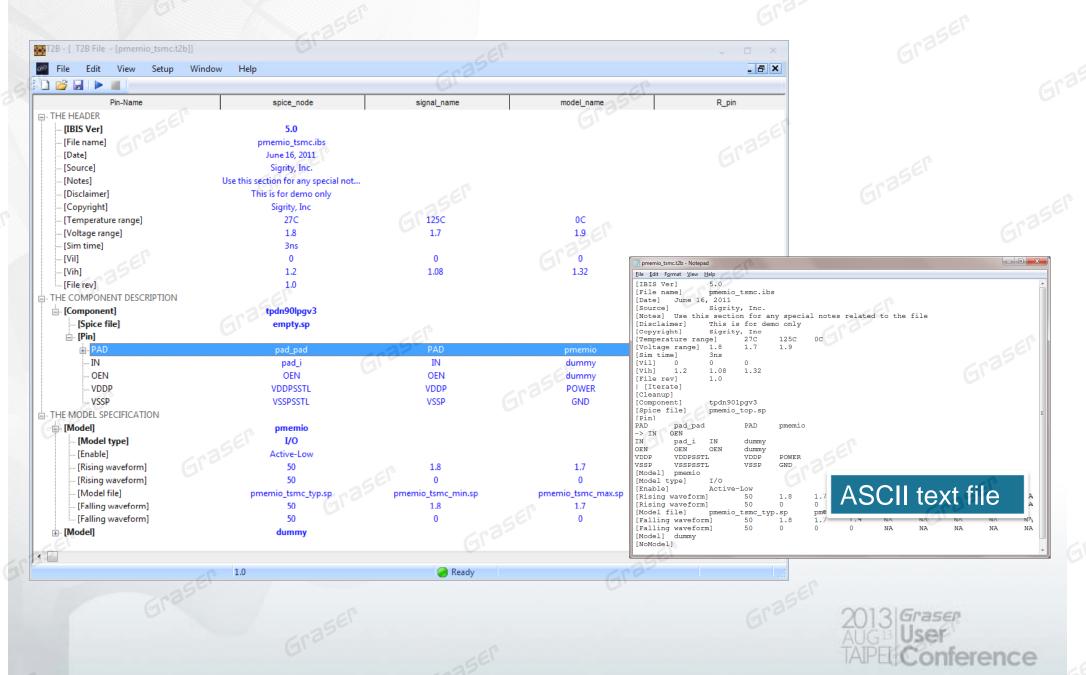

- T2B converts SPICE transistor-level buffer models to IBIS behavioral models.

- Implementation based on S2IBIS from NC State Univ.

### • T2B Features

- code translated from Java

- GUI added for both front-end and back-end processing

- spreadsheet setup

- graphical results

- applies golden parser

- applies either HSPICE, SPDSIM or Spectre

- BIRD 95/98 support added for full support of IBIS 5.0

- "power-aware" capabilities

- IBIS Plus model

- Greater accuracy than standard IBIS, including: on-die capacitance extraction as well as bias-dependent/frequency-dependent C\_comp.

- applications support and software support/enhancements from Cadence/Sigrity

# **SSO Simulation Enablement**

- High-speed parallel buses experience issues when all signals are switched simultaneously

- this is dominantly due to power delivery effects

- proximity coupling of signals plays a secondary role

- SSO simulation with ideal power delivery will rarely, if ever, be successful

- Transistor-level IO models properly power current

- simulations take days to run for only a few lanes in a bus modeled

- capacity/accuracy are limited, simple board/package models are applied

- W-elements for boards, a few RLC elements for packages

- IBIS 5.0 buffer models properly consider power currents

- IBIS 5.0 added support for power-aware effects with BIRD 95/98

- requires full IBIS 5.0 circuit simulator support (e.g. Sigrity SPEED2000/SystemSI and Synopsys HSPICE)

- S2IBIS lacks support beyond IBIS 3.2, specifically for BIRD 95/98

- SSO simulation with power-aware IBIS 5.0 models is fast and accurate

- hours become minutes, where including even one transistor-level model implies days

- IBIS 5.0 power-aware models enable system-level SSO simulation

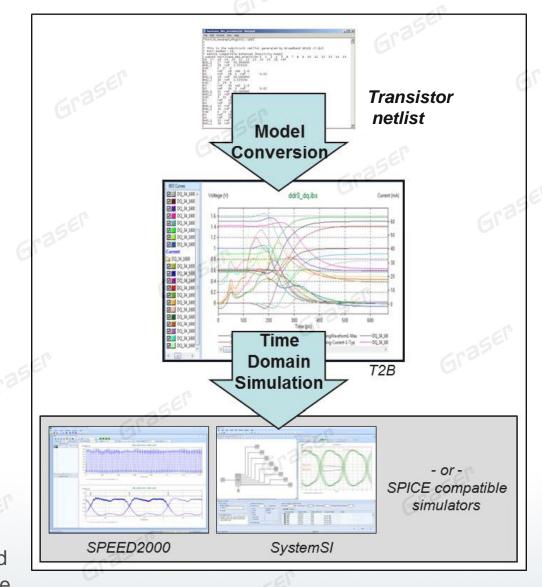

# **SSO Simulation Flow**

#### **Extract IBIS power-aware model**

#### 1. Setup for Conversion

- start with transistor-level netlist

- configure the conversion

- select the IOs to convert, select output type, etc.

- test circuit simulation with the netlist

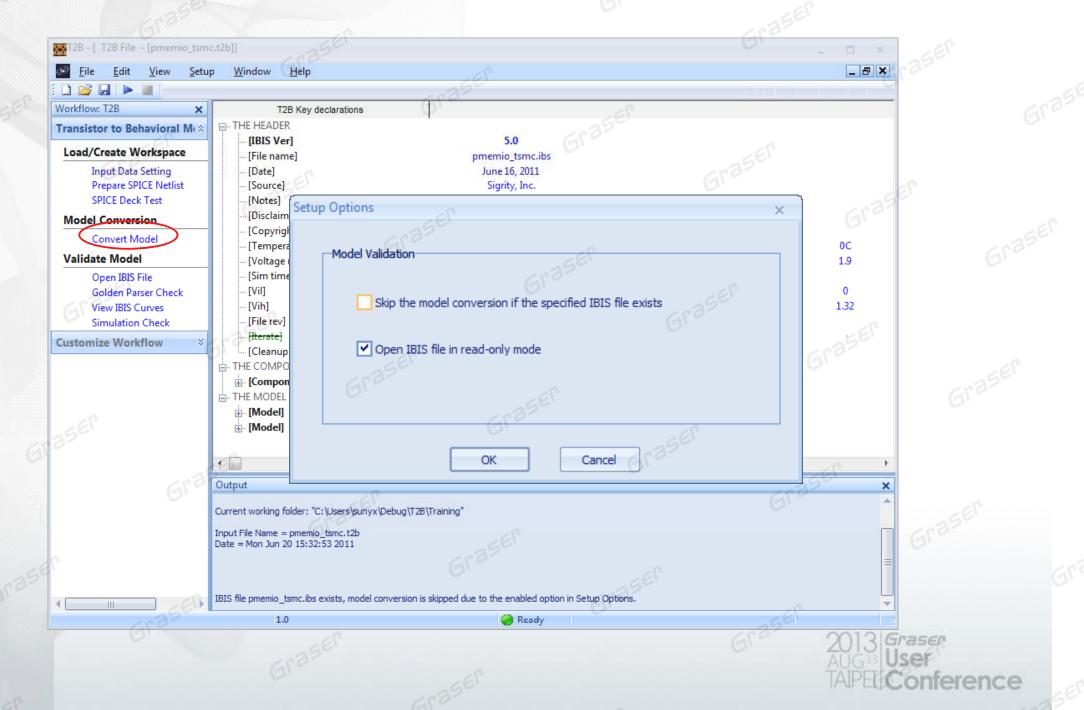

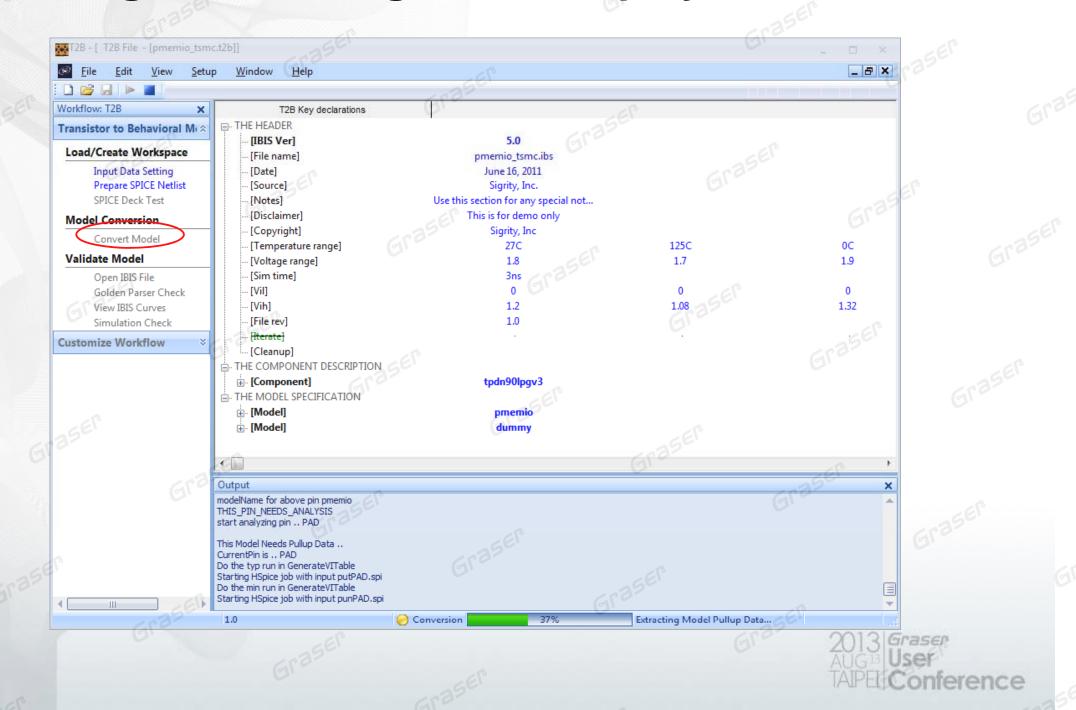

#### 2. Convert

launch the conversion, observe progress bar

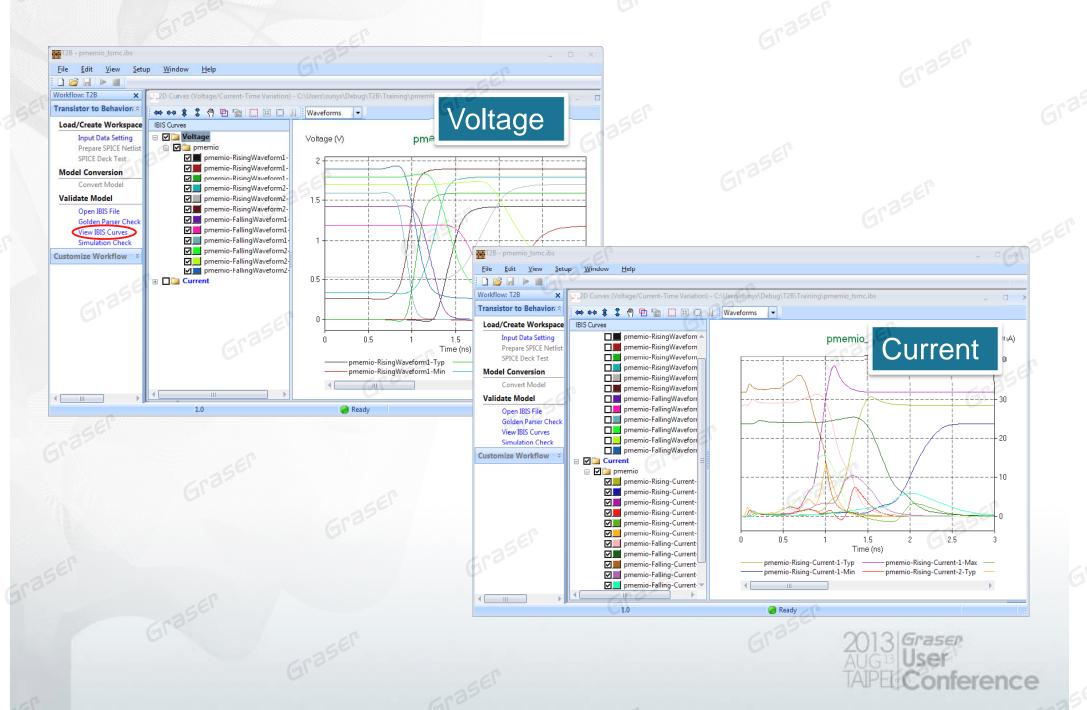

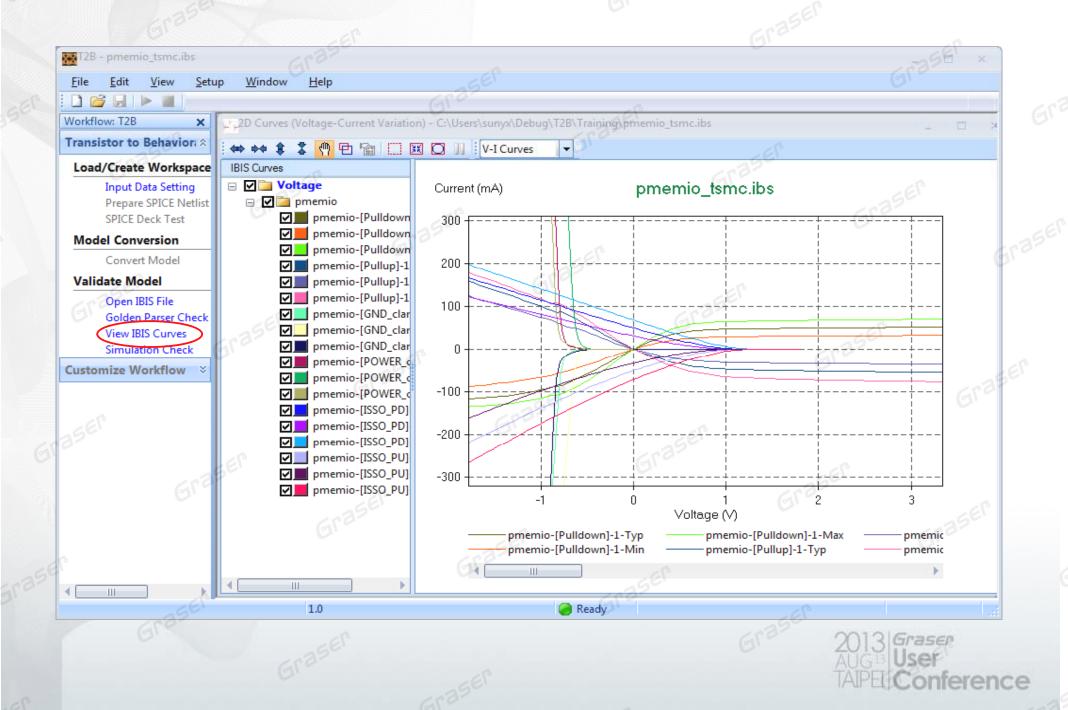

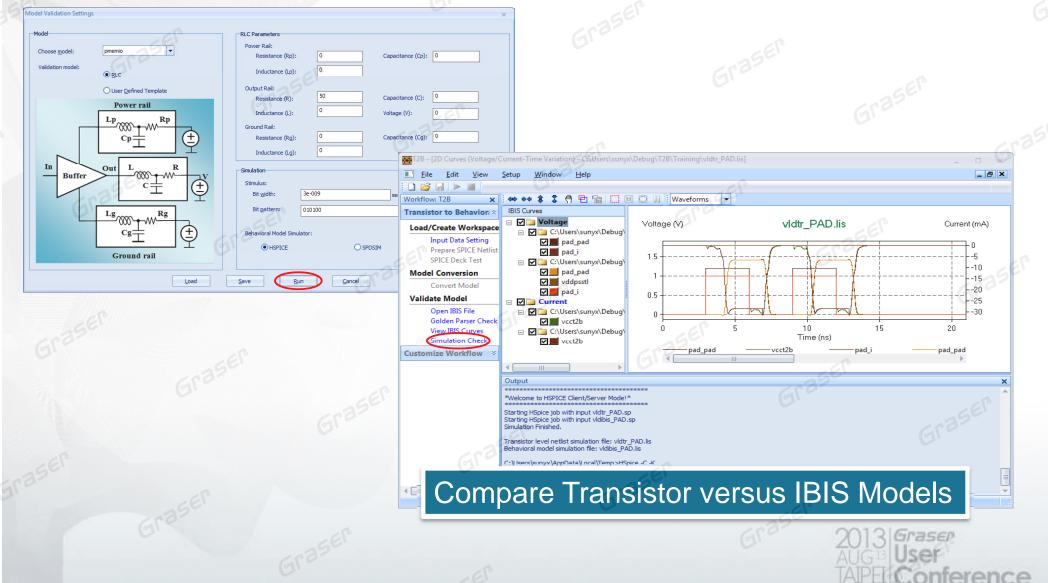

#### 3. Validate Model

- check with IBIS golden parser

- view voltage/current for rising/falling edges

- compare transistor vs. behavioral power currents

- verify circuit behavior for various loads

#### **Apply model for SSO simulation**

- 4. Transient circuit/system simulation

- Cadence/Sigrity SPEED2000/SystemSI and

- HSPICE each provide IBIS 5.0 power-aware support

rence

# **System Requirements**

### Circuit simulation engine

- HSPICE E-2010.12 or later

- SPDSIM 11.0 or later

- Spectre (conversion only, no IBIS 5.0 support yet)

### Environment variables setting

- HSPICE licensing environment variable

- Path to HSPICE executable

# **T2B Workflow**

## Setup - Intelligent Spreadsheet Setup GUI

1

# **Setup - Prepare and Test the Netlist Call**

| ddiow: T28       xvdd VDD 0 DC Vcore         unsistor to Behavioral Mico       vvdd Stl VDDSSTL 0 DC Vore         oad/Create Workspace       vvdd Stl VDDSSTL 0 DC Vore         ingur Data Setting       vedsts ESUVSS 00 C0 v         Prepare SPICE Netlist       vvddStl VDDSSTL 0 DC Vore         Noversion       vvddStst VDDSSTL 0 DC Vore         Vessti VDSSSTL 0 DC 0v       vessti VSSSSTL 0 DC 0v         vessti VSSSSTL 0 DC Vore       vessti VSSSSTL 0 DC Vore         vsssti VSSSSTL 0 DC 0v       vessti VSSSSTL 0 DC Vore         vessti VDSSSTL 0 DC Vore       vessti VSSSSTL 0 DC Vore         vessti VDSSSTL 0 DC Vore       vessti VSSSSTL 0 DC Vore         vessti VDSSSTL 0 DC Vore       vessti VSSSSTL 0 DC Vore         vessti VDSSSSTL 0 DC Vore       vessti VSSSSTL 0 DC Vore         vessti VDSSSSTL 0 DC Vore       vessti VSSSSTL 0 DC Vore         vessti VSSSSTL 0 DC Vore       vessti VSSSSTL 0 DC Vore         vessti VSSSSSTL 0 DC Vore       vesti VSSSSSSSSSSSSSTL 0 DC Vore         vessti VSSSSSTL 0 DC Vore       vesti VSSSSSSSSSSSSSSTL 0 DC Vore         vessti VSSSSSTL 0 DC Vore       vesti VSSSSSTL 0 DC Vore         vesti VSSSSSTL 0 DC Vore       vesti VSSSSSTL 0 DC Vore         vesti VSSSSSSTL 0 DC Vore       vesti VSSSSSTL 0 DC Vore         vennet VSSSSSSSUSSSSSSSSSSSSSSSSSSSSSSSSSSSSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>File Edit View Set</u> | up <u>W</u> indow <u>H</u> elp |                                  |                           | _ 8 ×             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------|----------------------------------|---------------------------|-------------------|

| Insistor to Behavioral M+2       Vvss VSS 0 DC 0v         oad/Create Workspace       Vvss VSS 0 DC 0v         Input Data Setting       vvsssstl VSSSSTL 0 DC Vore         vvsssstl VSSSSTL 0 DC Vio       vossstl VSSSSTL 0 DC Vio         Convert Model       vvsssstl VSSSSTL 0 DC Vio         alidate Model       vvsssstl VSSPSSTL 0 DC Vio         Convert Model       vvsssstl VSSPSSTL 0 DC Vio         alidate Model       vvsssstl VSSPSSTL 0 DC Vio         Open IBIS File       ODC 0v         Golden Parser Check       vvssspsstl VSSPSSTL 0 DC 0v         vvssstl VSSPSSTL 0 DC 0v       vorfesst VPCSSTL 0 DC 0v         -connect POCSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect POCSSTL VSSPSSTL       vvssspsstl VSSPSSTL 0 DC 0v         -connect VSSRSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect VSSRSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect VSSPSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect VSSPSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect VSSPSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect VSSPSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect VSSPSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -connect VSSPSSTL 0 DC 0v       vorfesst VSSPSSTL 0 DC 0v         -co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 😂 🖬 🕨 🔳 👘                 |                                | 1355                             |                           | G                 |

| understore       Veddssti VDDSSTL 0 DC Vcore         vvssssti VSSSSTL 0 DC 0v         vvssssti VSSSSTL 0 DC 0v         vesdvss ESDVSS 0 DC 0v         vesdvss ESDVSS 0 DC 0v         vesdvss ESDVSS 0 DC 0v         connect ESDVSS VSSPSSTL 0 DC Vio         convert Model         alidate Model         Open IBIS File         Golden Parser Check         View IBIS Curves         Simulation Check         stormize Workflow         **/vi nin 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)         */vin in 10 pulgeVcore 0v 40n 0.5n 0.5n 40n 41n)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | rkflow: T2B 🗙             | vvdd VDD 0 DC Vcore            | EEP                              |                           | A                 |

| bad/Create Workspace       vvsssstl VSSSSTL 0 DC 0v         Input Data Setting       vsedvss ESDVSS 0 C 0 v         prepare SPICE Netlist       vsedvss ESDVSS 10 DC 0v         connect KDSVSS VSSSTL 0 DC Vio       vsedsstl VDSSSTL 0 DC 0v         convert Model       vvvdgsstl VDDPSSTL 0 DC 0v         alidate Model       vvvdgsstl VDDPSSTL 0 DC 0v         Open IBIS File       Golden Parser Check         Golden Parser Check       vvrefssl VESSSTL 0 DC 0v         vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin pad_i i 0 pwl(0 tv 10n tv 10.24n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.24n 0v 30n 0v)         ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nsistor to Behavioral M 🖄 |                                |                                  |                           |                   |

| Input Data Setting       *vesdvss ESDVSS 0 DC 0v         Prepare SPICE Netlist       *vesdvss ESDVSS 0 DC 0v         SPICE Deck Test       odel Conversion         Convert Model       *vvd55sstl VDDPSSTL 0 DC 0v         alidate Model       *vocdsstl VDSSPSSTL 0 DC 0v         Open IBIS File       *vocdsstl VDSSPSSTL 0 DC 0v         Golden Parser Check       *vvm IBIS Curves         Simulation Check       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 pad_i VDD VSS BUFFD2         ****** SUBCKT PMEMIO A2 A6 C DS I LVCMOS OEN PAD PWD S0 S1       ****** SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEM OEN PAD PGATE PGATEM PGATEM PGATEM PGCSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDSSTL VSSRSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ad/Create Workspace       |                                |                                  |                           |                   |

| Prepare SPICE Netlist<br>SPICE Deck Test       .connect ESDVSS VSSPSSTL         odel Conversion       "vvd25sst I VD2SSTL 0 DC Vio         "vvsspsstI VSSPSSTL 0 DC 0v       "vvddpsstI VDDPSSTL 0 DC Vio         "vvddpsstI VDDPSSTL 0 DC 0v       "vvddpsstI VDDPSSTL 0 DC 0v         alidate Model       "vpocsstI POCSSTL 0 DC 0v         Open IBIS File       connect VSSRSSTL 0 DC 0v         Golden Parser Check       "vestssI VSSPSSTL 0 DC 0v         View IBIS Curves       .connect VSSRSSTL 0 DC 0v         Simulation Check       "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       "vin in 10 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         "vin in 10 pulse(Vcore 0v 50 0.5N 1.2000 Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v)         "***** SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS SUS PMEMIO <t< td=""><td></td><td></td><td></td><td></td><td>F</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |                                |                                  |                           | F                 |

| SPICE Deck Test       *vvd25sst1 V025SSTL 0 DC Vio         odel Conversion       *vvsspsst1 V325SSTL 0 DC 0v         Convert Model       *vvsspsst1 V325SSTL 0 DC 0v         alidate Model       *vordspsst1 VD2SSSTL 0 DC 0v         Open IBIS File       connect V02SSSTL 0 DC 0v         Golden Parser Check       *vrefssl VREFSSTL 0 DC 0v         View IBIS Curves       connect V02SSSTL 0 DC 0v         Simulation Check       *vvin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in2 Workflow       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in2 Workflow       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin in2 0 pul(0 0v 10n 0v 10.24n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v)         **xtm rpc-layout spice         **xtms SUBCKT PMEMIO A2 & 6 C DS I LVCMOS OEN PAD PWD S0 S1         **xtms SUBCKT PMEMIO A2 & 6 C DS SI VDDSSTL VDDSSTL VSSPSSTL VSSSPSSTL VSSPSSTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           | .connect ESDVSS VSSPSSTL       |                                  |                           |                   |

| odel Conversion       .connect VD25SSTL VDDPSSTL         Convert Model       *vvdgsstl VDDPSSTL 0 DC 0v         alidate Model       *vvodsstl VDDPSSTL 0 DC 0v         connect POCSSTL VSSPSSTL       vvrefssl VSSPSSTL 0 DC 0v         connect VSSRSSTL 0 DC 0v       *vvrefssl VREFSSTL 0 DC 0v         connect VSSRSSTL 0 DC 0v       *vvrefssl VREFSSTL 0 DC 0v         simulation Check       *vvssrsstl VSSRSSTL 0 DC 0v         tomize Workflow       *vin in 10 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *vin pad_i 0 pwl[0 0v 10n 0v 10.24n Vcore 13.00n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v]         **xin 11 pad_i VDD VSS BUFFD2         *******       pre-layout spice         ********       IN pe spice         *******       SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM POCSSTL VSS VSS pad_ vSS pad_i VSS VSS pad_i VSS VSS PMEMIO         ********       IDE spice         *******       VSS VSS pad_i VSS PSSTL VDDPSSTL VDDSSTL VREFSSTL VSSPSSTL VSSSSTL VSSSSSTL VSSSSTL VSSSSSTL VSSSSSTL VSSSSTL VSSSSTL VSSSSSTL VSSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           | *vvd25sstl VD25SSTL 0 DC Vio   |                                  |                           | GI                |

| Convert Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |                                |                                  |                           |                   |

| alidate Model       "vpocssfl POCSSTL 0 DC 0v         Open IBIS File       connect POCSSTL VSSPSSTL         Golden Parser Check       vverfssl VREFSSTL 0 DC 0v         View IBIS Curves       connect VSSRSSTL VSSPSSTL         Simulation Check       "vin in 10 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *vin in 10 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]       "vin in 10 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *vin in 10 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]       "vin in 10 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *vin in 10 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]       "vin in 2 pullo 0v 10n 0v 10.24n Vcore 13.04n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v]         **x1 in1 pad_i VDD VSS BUFFD2       "**x1 in1 pad_i VDD VSS BufFD2         ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                |                                  |                           |                   |

| Image induct foreign       .connect POCSSTL VSSPSSTL         Open IBIS File       .connect POCSSTL VSSPSSTL 0 D C '0.5*Vio'         View IBIS Curves       *vin in1 0 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *tomize Workflow       *vin in1 0 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *tomize Workflow       *vin in1 0 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *tomize Workflow       *vin pad_i 0 pul[0 0v 10n 0v 10.24n Vcore 13.00n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v]         *tx1 in1 pad_i VDD VSS BUFFD2         *txtmst pre-layout spice         *txtmst suBcKT PMEMIO A2 A6 C DS I LVCMOS OEN PAD PWD S0 S1         *tx2 VSS VSS pad_c VSS pad_i VSS VSS pad_pad VDD VSS VSS PMEMIO         *txtmst lpe spice         *txtmst SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM POCSSTL VDDPSSTL VDDSSTL VDDSSTL VREFSSTL VSSPSSTL VSSRSTL                                                                                                                                                                                                                                                                                                                                                      | Convert Model             |                                |                                  |                           |                   |

| Open IBIS File         Golden Parser Check         View IBIS Curves         Simulation Check         tomize Workflow         **vin in1 0 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *vin nad_i 0 pwl(0 0v 10n 0v 10.24n Vcore 13.00n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v)         **x1 in1 pad_i VDD VSS BUFFD2         *******         ******         SUBCKT PMEMIO A2 A6 C DS I LVCMOS 0EN PAD PWD S0 S1         ******         ******         SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM 0EN PAD PGATE PGATEH PGATEM         POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VSSPSSTL VDDPSSTL         ****** SUBCKT PMEMIO A2 A6 C DS ESDVSS pad_i VSS n2 n3 n4 0EN pad n5 n6 n7 VSS VDD VSS VSS VD25SSTL VDDPSSTL         VDDSSTL VREFSSTL VSSPSSTL                                                                                                                                                                                                                                                                                                                                                                                                                                  | alidate Model             |                                |                                  |                           |                   |

| Golden Parser Check<br>View IBIS Curves<br>Simulation Check       *vssrsstl VSSRSSTL 0 DC 0v<br>.connect VSSRSSTL VSSPSSTL         tomize Workflow       *vin in1 0 pulse(Vcore 0v 40n 0.5n 0.5n 40n 41n)         *vin pad_i 0 pwl(0 0v 10n 0v 10.24n Vcore 13.00n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v)         *x1 in1 pad_i VDD VSS BUFFD2         ****** SUBCKT PMEMIO A2 A6 C DS I LVCMOS 0EN PAD PWD S0 S1         **x2 VSS VSS pad_c VSS pad_i VSS VSS pad_pad VDD VSS VSS PMEMIO         ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Open IBIS File            |                                |                                  |                           | .0                |

| View IBIS Curves<br>Simulation Check       .connect VSSRSSTL VSSPSSTL         *tomize Workflow       *         *ti na 1 0 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *vin pad_i 0 pwl[0 0v 10n 0v 10.24n Vcore 13.00n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v]         **X1 in1 pad_i VDD VSS BUFFD2         ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Golden Parser Check       |                                |                                  |                           | SEL I             |

| Simulation Check         #tomize Workflow         *tin in 1 0 pulse[Vcore 0v 40n 0.5n 0.5n 40n 41n]         *trin pad_i 0 pwl[0 0v 10n 0v 10.24n Vcore 13.00n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v]         *tx1 in 1 pad_i VDD VSS BUFFD2         *ttimt pre-layout spice         *ttimt lpe spice         *ttimt lpe spice         *ttimt SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM POCSSTL PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDSSTL VDDSSTL VSSPSSTL VDDPSSTL VSSPSSTL VSSPSS                                                                                                                                                                                                                 | View IBIS Curves          |                                |                                  |                           | Gra               |

| *vin pad_i 0 pwl(0 0v 10n 0v 10.24n Vcore 13.00n Vcore 13.24n 0v 16.00n 0v 16.24n Vcore 19.00n Vcore 19.24n 0v 30n 0v)         **x1 in1 pad_i VDD VSS BUFFD2         **x**** SUBCKT PMEMIO A2 A6 C DS I LVCMOS OEN PAD PWD S0 S1         **x2 VSS VSS pad_c VSS pad_i VSS VSS pad_pad VDD VSS VSS PMEMIO         ******* SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL VSSRSSTL         ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Simulation Check          |                                | u 0.5n 40n 41n)                  |                           |                   |

| ***1 in1 pad_i VDD VSS BUFFD2 ******** pre-layout spice ******** SUBCKT PMEMIO A2 A6 C DS I LVCMOS OEN PAD PWD S0 S1 ***2 VSS VSS pad_c VSS pad_i VSS VSS pad_pad VDD VSS VSS PMEMIO ******* SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL VSSRSSTL VSSRSSTL VSSRSSTL VSSRSSTL VSSRSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VDDPSSTL VSSRSSTL V | tomize Workflow 🛛 🛛       |                                |                                  | 16.24n Vcore 19.00n Vcore | 19.24n 0v 30n 0v) |

| ****** SUBCKT PMEMIO A2 A6 C DS I LVCMOS OEN PAD PWD S0 S1<br>**x2 VSS VSS pad_c VSS pad_i VSS VSS pad_pad VDD VSS VSS PMEMIO<br>****** Ipe spice<br>****** SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM<br>POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL<br>x2 VSS VSS pad_c VSS ESDVSS pad_i VSS n2 n3 n4 OEN pad_pad n5 n6 n7 VSS VDD VSS VSS VD25SSTL VDDPSSTL<br>VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL PMEMIO<br>c2 pad_c VSS 0.25p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -r                        |                                |                                  |                           |                   |

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           | ****** pre-layout spice        |                                  |                           |                   |

| ****** Ipe spice<br>****** SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM<br>POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL<br>x2 VSS VSS pad_c VSS ESDVSS pad_i VSS n2 n3 n4 OEN pad_pad n5 n6 n7 VSS VDD VSS VSS VD25SSTL VDDPSSTL<br>VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL PMEMIO<br>c2 pad_c VSS 0.25p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |                                |                                  |                           |                   |

| ****** SUBCKT PMEMIO A2 A6 C DS ESDVSS I LVCMOS NGATE NGATEH NGATEM OEN PAD PGATE PGATEH PGATEM<br>POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL<br>x2 VSS VSS pad_c VSS ESDVSS pad_i VSS n2 n3 n4 OEN pad_pad n5 n6 n7 VSS VDD VSS VSS VD25SSTL VDDPSSTL<br>VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL PMEMIO<br>c2 pad_c VSS 0.25p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                           |                                | S VSS pad_pad VDD VSS VSS PMEMIO |                           | EF                |

| POCSSTL PWD S0 S1 VD25SSTL VDDPSSTL VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSRSSTL<br>x2 VSS VSS pad_c VSS ESDVSS pad_i VSS n2 n3 n4 OEN pad_pad n5 n6 n7 VSS VDD VSS VSS VD25SSTL VDDPSSTL<br>VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSSSTL PMEMIO<br>c2 pad_c VSS 0.25p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |                                |                                  | 623                       | 2                 |

| x2 VSS VSS pad_c VSS ESDVSS pad_i VSS n2 n3 n4 OEN pad_pad n5 n6 n7 VSS VDD VSS VSS VD25SSTL VDDPSSTL<br>VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSSSTL PMEMIO<br>c2 pad_c VSS 0.25p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |                                |                                  |                           | EH PGATEM         |

| VDDSSTL VREFSSTL VSSPSSTL VSSRSSTL VSSSSSTL PMEMIO<br>c2 pad_c VSS 0.25p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |                                |                                  |                           |                   |

| c2 pad_c VSS 0.25p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           |                                |                                  | 22 ADD 422 422 AD522221   |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |                                | SSRSSTE VSSSSTE PMEMIU           |                           |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           | cz pau_c voo u.zop             |                                  |                           |                   |

| 1.0 Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |                                | Gra                              | 9                         |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           | 1.0                            | 🥑 Ready                          |                           |                   |

1Ce

### **Launch the Conversion**

### **Progress Messages are Displayed**

### Validation - View the IBIS File

|                                 | ME den Hale                                                            |             |

|---------------------------------|------------------------------------------------------------------------|-------------|

| <u>File Edit View Setup</u>     | Window Help                                                            | Gra-B×      |

|                                 | ***************************************                                |             |

|                                 | LIBIS file nmemio, temp ibs created by T2B Version 1.0                 | -           |

| ransistor to Behavioral Model ( | Sigrity, Inc. 2011                                                     |             |

| Load/Create Workspace           | Simulator: ****** HSPICE – E-2010.12 32-BIT (Nov 20 2010) winnt ****** |             |

| Input Data Setting              | [IBIS ver] 5.0                                                         |             |

| Prepare SPICE Netlist           | [File name] pmemio_tsmc.ibs                                            |             |

| SPICE Deck Test                 | [File Rev] 1.0                                                         |             |

| Model Conversion                | [Date] June 16, 2011<br>– [Source] Sigrity, Inc.                       |             |

| Convert Model                   | [Notes] Use this section for any special notes related to the file     |             |

| Validate Model                  | [Disclaimer] This is for demo only                                     |             |

| Open IBIS File                  | [Copyright] Sigrity, Inc                                               |             |

| Golden Parser Check             | *****************                                                      |             |

| View IBIS Curves                | Component tpdn90lpgv3                                                  |             |

| Simulation Check                | <u> </u>                                                               |             |

| ustomize Workflow               | [Component] tpdn90lpgv3                                                |             |

| G                               | [Manufacturer] Manufacturer name                                       |             |

|                                 | [Package]                                                              |             |

|                                 | variable typ min max<br>R pkg 0.0 0.0 0.0                              |             |

|                                 | L_pkg 0.0H 0.0H 0.0H                                                   |             |

|                                 | C_pkg 0.0F 0.0F 0.0F                                                   |             |

|                                 | <br> Pin  signal name model name R pin L pin C pin                     |             |

|                                 | VSSP VSSP GND                                                          |             |

|                                 | VDDP VDDP POWER                                                        |             |

|                                 | JOEN OEN dummy<br>JIN IN dummy                                         |             |

|                                 | PAD PAD pmemio                                                         |             |

|                                 | Gru                                                                    |             |

| 111                             | SE CONTRACTOR                                                          | (3)         |

|                                 | 1.0 Gr Ready                                                           | Ln 1, Col 1 |

|                                 |                                                                        |             |

AUG User TAIPEL Conference

# Validation - Warnings from the Golden Parser

| E File Edit View Setup                                     | indow Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 | 8 ×      |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|

|                                                            | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |          |

| Workflow: T2B                                              | **********************                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 |          |

| Transistor to Behavioral Model (*<br>Load/Create Workspace | IBIS file pmemio_tsmc.ibs created by T2B Version 1.0<br>Sigrity, Inc. 2011<br>Simulator: ****** HSPICE – E-2010.12 32-BIT (Nov 20 2010) winnt ******                                                                                                                                                                                                                                                                                                                       |                                                                 |          |

| Input Data Setting<br>Prepare SPICE Netlist                | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 |          |

| SPICE Deck Test                                            | [File Rev] 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                 | -10      |

| Model Conversion                                           | [Date] June 16, 2011                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                 | 561      |

| Convert Model                                              | [Source] Sigrity, Inc.<br>[Notes] Use this section for any special notes related to the file                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |          |

| Validate Model                                             | [Disclaimer] This is for demo only<br>[Copyright] Sigrity, Inc                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                 |          |

| Open IBIS File                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 | -        |

| Golden Parser Check                                        | Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 | ×        |

| View IBIS Curves<br>Simulation Check                       | WARNING (line 42) -<br>Model pmemio: C_comp min value is not the smallest value listed                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 | <b>^</b> |

|                                                            | WARNING (line 42) -                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |          |

| Customize Workflow                                         | Model pmemio: C_comp max value is not the largest value listed<br>WARNING (line 43) -                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |          |

| Grass                                                      | Model pmemio: C_comp_pullup min value is not the smallest value listed<br>WARNING (line 43) -<br>Model pmemio: C_comp_pullup max value is not the largest value listed<br>WARNING (line 44) -<br>Model pmemio: C_comp_pulldown min value is not the smallest value listed<br>WARNING (line 44) -                                                                                                                                                                           |                                                                 |          |

| 10                                                         | Model pmemio: C_comp_pulldown max value is not the largest value listed<br>NOTE (line 163) - Pullup Maximum data is non-monotonic<br>NOTE (line 164) - Pullup Typical data is non-monotonic<br>NOTE (line 521) - ISSO_PD Minimum data is non-monotonic<br>WARNING - Model 'pmemio': Model_type 'I/O' must have Vinl set<br>WARNING - Model 'pmemio': Model_type 'I/O' must have Vinh set<br>WARNING - Model 'pmemio': Wmeas timing test load parameter should be specified |                                                                 |          |