## Mixed-Signal Design for Analog-Centric & Digital-Centric Verification

Stacy Chen / Paine Chuang 13/Aug/2013

## Topic

- Mixed-Signal Verification Challenges

- Overview of Mixed-Signal Solution

- Mixed-Signal Verification

- Analog-Centric Verification

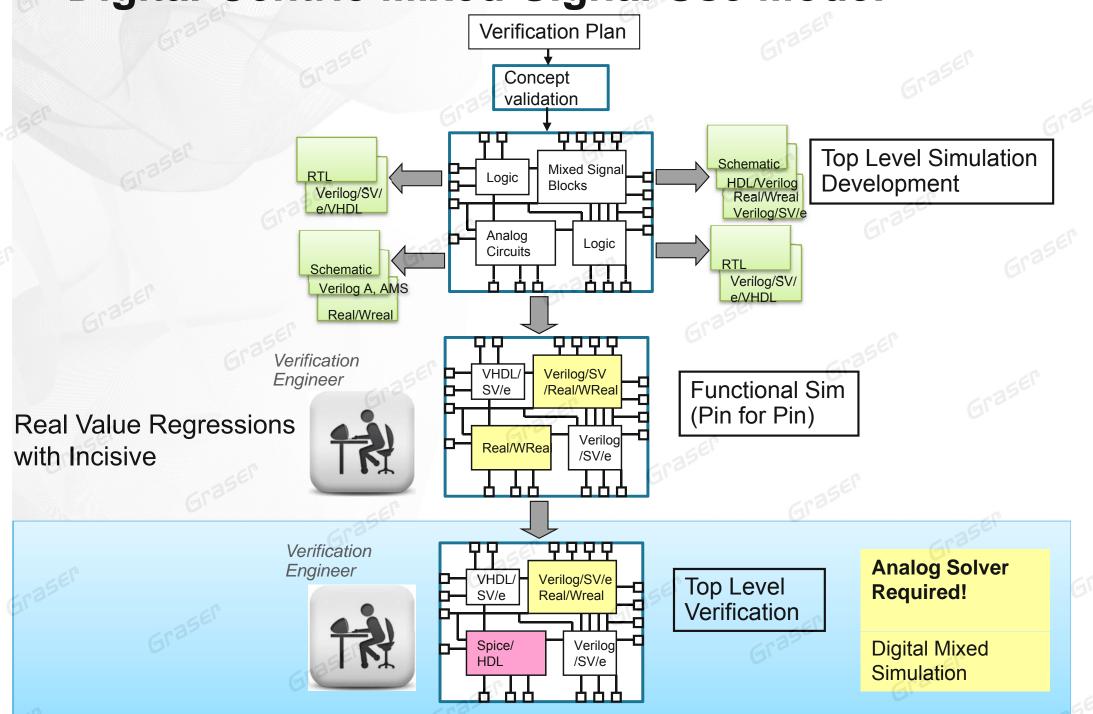

- Digital-Centric Verification

### Summary

## **Mixed-Signal Verification Challenges**

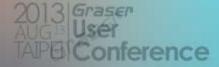

## **Market Trends**

- High growth applications generating demand for digital and analog circuitry in turn fueling mixed-signal growth

- Over 80% of these designs are mixed-signal

- Real-world data requires analog and digital processing

- Operating at Ghz+ requires high speed interfaces

- Integrated systems require analog/RF components mixed with digital

- Low power requirements driving integration

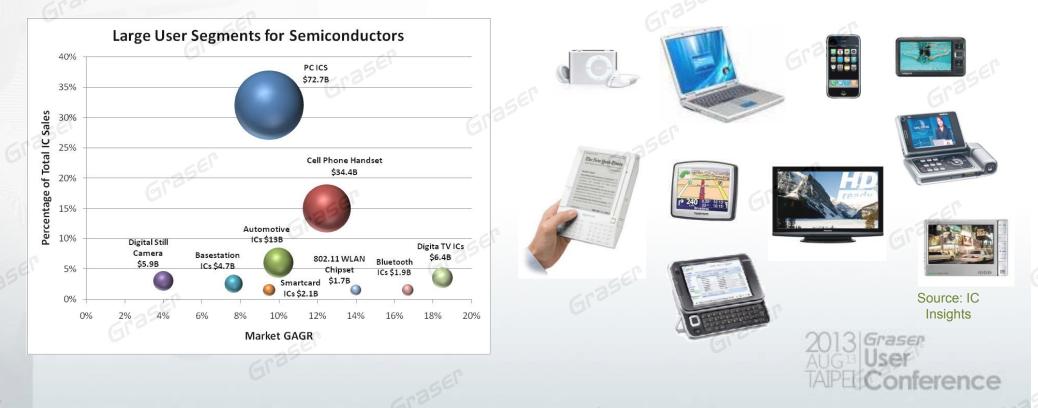

## **MS Verification Challenges**

#### **Mixed-signal SoC Complexity**

## **MS Verification Challenges**

#### Why is SoC Level MS Verification so difficult?

#### Mixed Signal simulation issues:

- CoSim: Analog domain is continuous and Digital is event driven

- MS/Analog simulation performance limitations

- Speed vs. Accuracy tradeoffs

- Analog coverage need visibility into Analog space to gauge quality of verification

- Pin connectivity errors

- Analog and cross domain low power issues

- Complex debugging

#### MS Modeling issues:

- Verification environment must support different levels of abstraction (Spice / Verilog-AMS / Real-Number Models)

- Model Creation: fidelity of model how much accuracy is really needed vs. how much accuracy is possible?

- Model Validation: how to establish models equivalence at different levels of abstraction

## **MS Verification Challenges**

#### The usual dilemma ...

- I need my simulation results as soon as possible ...

- I need maximum accuracy ...

- I need a full chip simulation ...

- Started a spice solver on full chip transistor level netlist

still waiting for the simulation results

- Finished a pure digital simulation

- but don't see analog effects

- Ran a small block on spice

- how do I know that it works correctly in the bigger context?

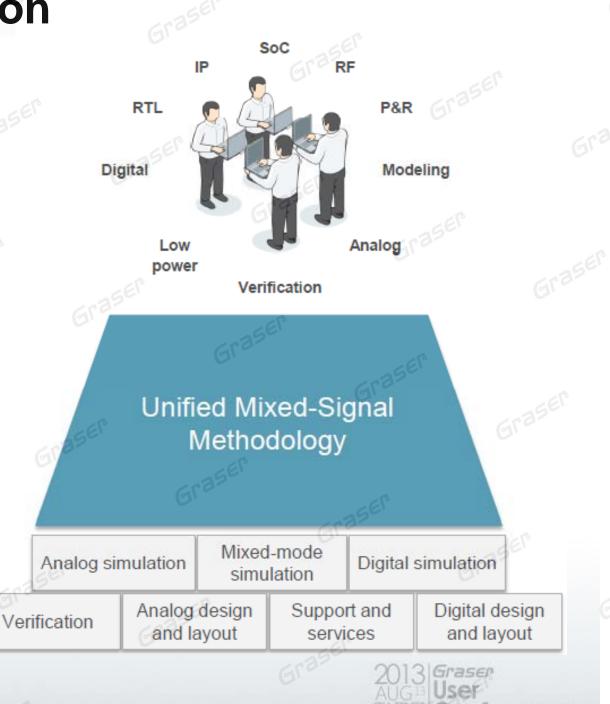

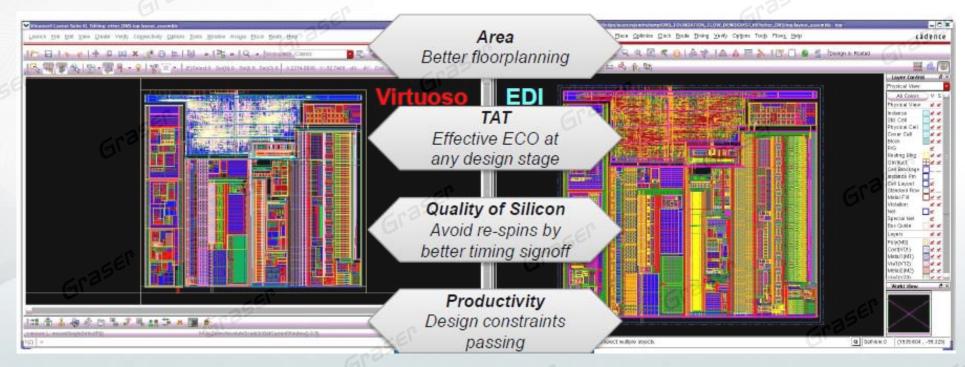

## **Overview of Mixed-Signal Solution**

#### Benefits

- Design quality, area

- Productivity, TAT

- Fewer iterations/re-spins

- Unified design methodology

- Addresses design challenges

- Scalable for complexity

#### Foundation

- Products and technology

- Support and services

- IP and ecosystem

erence

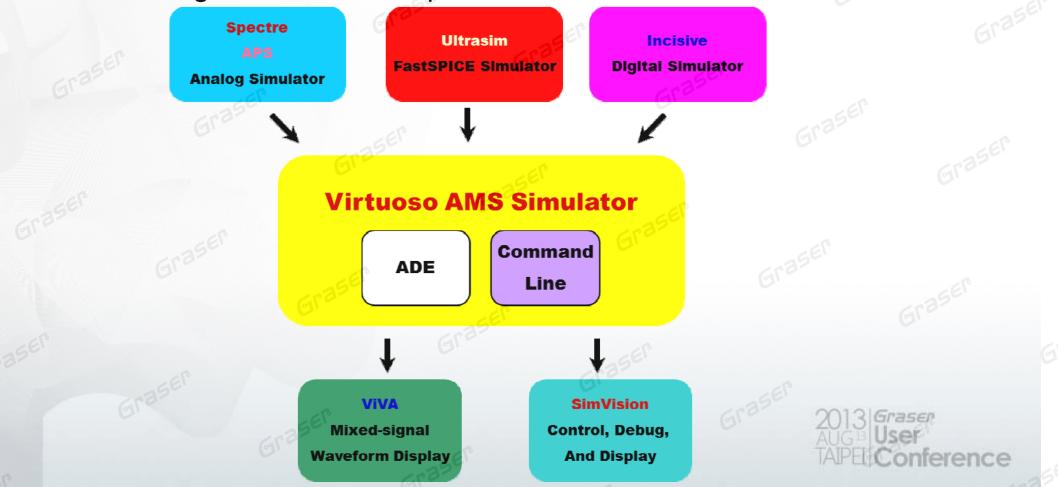

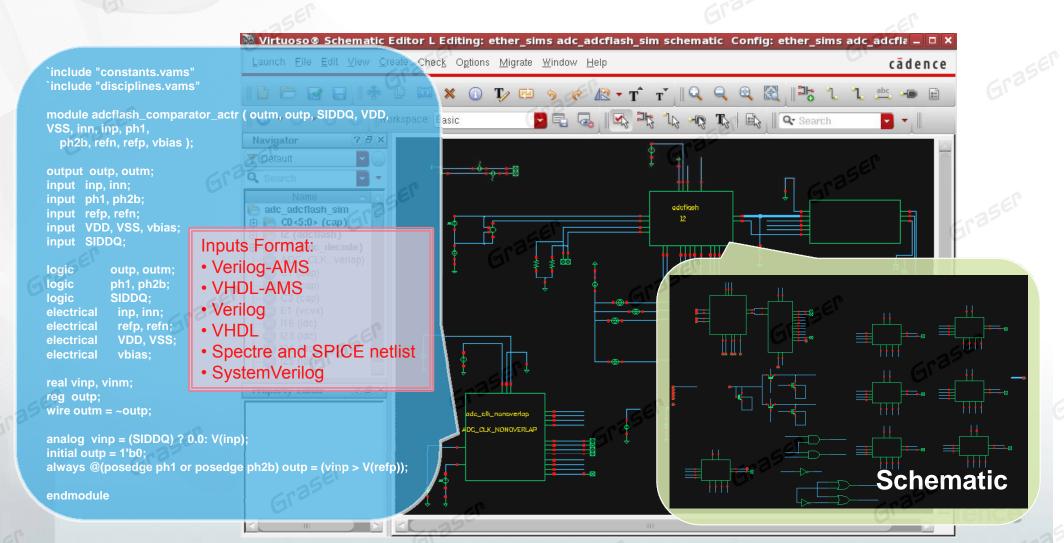

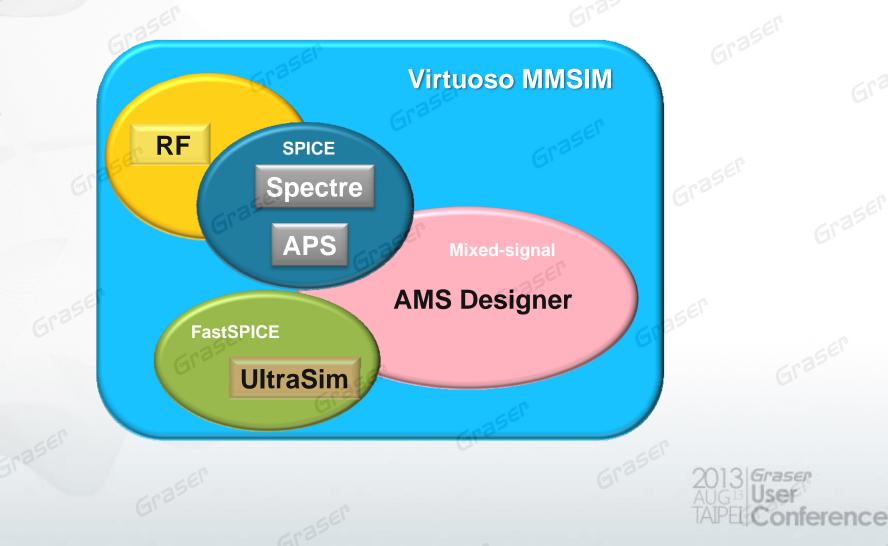

#### **Virtuoso AMS Designer Verification**

Virtuoso AMS Designer is a single executable mixed-signal simulator based on the proven technology of Virtuoso Spectre, Virtuoso Accelerated Parallel Simulator, UltraSim Full-Chip Simulator, and the Incisive digital simulation capabilities.

#### **Virtuoso AMS Designer Verification**

#### **Virtuoso AMS Designer Verification**

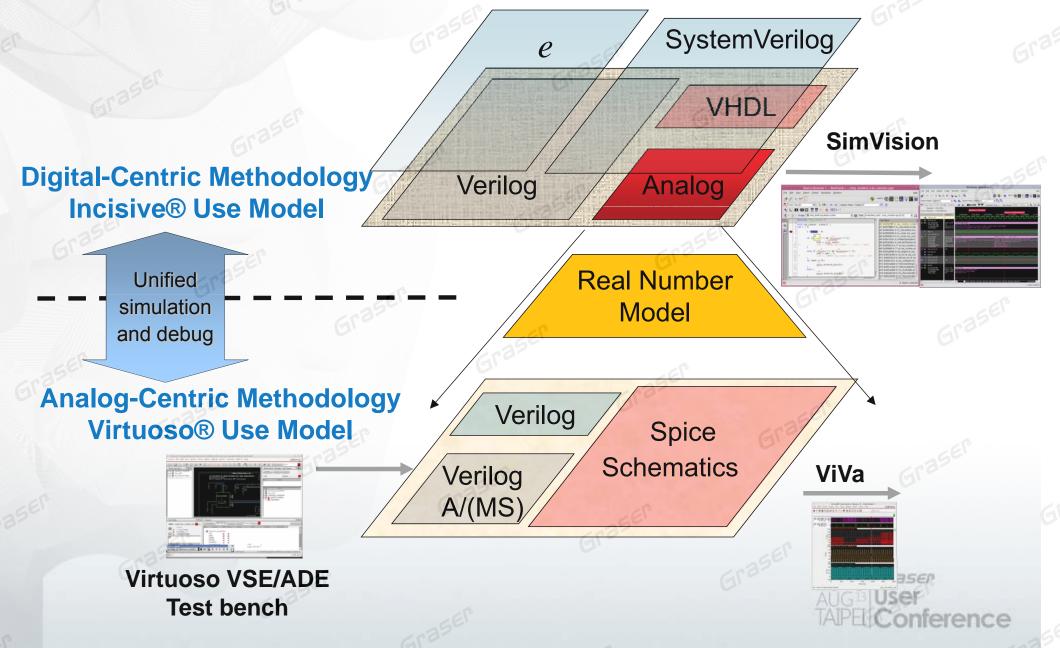

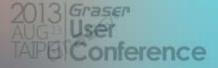

#### **Analog Centric Verification**

- Target: AMS IP creation

- Analog Design Engineer

- Analog (and analog-centric MS) Methodology

- Schematic driven, GUI based

- Transistor level simulationFunctional

- DC, AC, Transient

- Corner Analysis

- □ Monte Carlo Analysis

- Performance

- AC, RF, Noise

#### **Digital Centric Verification**

- Target: MS SoC Verification

- Verification Engineer

•

- Digital MDV Methodology

Command-line driven

Directed random testbenches

Assertion-based Verification

Metrics and Coverage Driven

Low Power CPF

Verification Management

- HW/SW Verification

**Comprehensive Verification Methodology bridging the gap**

#### **Virtuoso AMS Designer Verification**

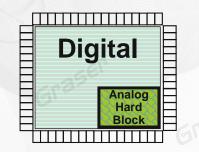

- Digital-centric Mixed-signal Verification User

- Mainly application specific digital blocks designed with standard cell methodology

- Analog blocks support specific function protocol Integration through hard analog IP import

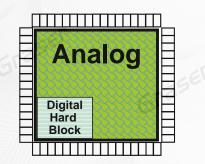

- Analog-centric Mixed-signal Verification User

- Dominant analog, custom-digital and RF blocks developed using custom methodology

- Digital blocks for control, calibration & connectivity

- Integration through hard digital IP import

- Mixed-Signal SoC Verification User

- Full-chip SoC verification

- Iterative verification done by digital group

- High volume digital-centric nightly regressions tests

- Concurrent analog & digital block design flows

- Soft IP import and integration done by digital group

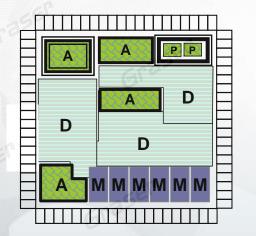

#### **Unified Environment for MS Implementation**

#### Unified Design DataBase \_OpenAccess

- No Data translation for Productivity

- Floorplan

- Placement

- Routing

- Unified Library and Technology setup

- Techfile

- Standard cell library

## **Analog-Centric Verification**

AMS Designer Verification in Virtuoso

2013 Graser AUGE User TAPE Conference

#### **Virtuoso Schematic Editor**

- Hierarchical schematic entry and hierarchy editor supports

- Analog, digital, mixed-signal, and RF symbol libraries are supported

#### **CoSim of digital configuration input and analog behavior**

|                                                                                                                                 | Virtuoso® Hierarchy Edit                                                                                                                                               | or: (amsPLL_test pll.                                                                                                                                                                                                                                                                    | _160MHz_sim co                                                                                 |                                                                                                                                                                                                       | _ 🗆   |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| e <u>E</u> dit <u>V</u> iew <u>P</u> li                                                                                         | ugins <u>H</u> elp                                                                                                                                                     | 0.                                                                                                                                                                                                                                                                                       |                                                                                                | cāde                                                                                                                                                                                                  | e n c |

| î 🖻 🗔   🖟                                                                                                                       | 🕈 🕹 🥱 🦿 🛈   🕻                                                                                                                                                          | 🖹 🛁   🗟 🥥                                                                                                                                                                                                                                                                                |                                                                                                |                                                                                                                                                                                                       |       |

| p Cell                                                                                                                          | P                                                                                                                                                                      | ? 🗗 🤉                                                                                                                                                                                                                                                                                    | Slobal Binding                                                                                 | gs                                                                                                                                                                                                    | ?5    |

|                                                                                                                                 | - 25 <sup>EI</sup>                                                                                                                                                     |                                                                                                                                                                                                                                                                                          | Librory List                                                                                   | td synopsys vital_memory                                                                                                                                                                              |       |

| orary: amsPLL_te                                                                                                                | st_1                                                                                                                                                                   | -F                                                                                                                                                                                                                                                                                       | Library List:                                                                                  | tu synopsys vitai_memory                                                                                                                                                                              |       |

| ell: pll_160MH                                                                                                                  | z_sim                                                                                                                                                                  | 255                                                                                                                                                                                                                                                                                      | View List:                                                                                     | riloga vhdl vhdlams wreal (                                                                                                                                                                           | C     |

| iew: schematic                                                                                                                  |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          | The second                                                                                     |                                                                                                                                                                                                       |       |

|                                                                                                                                 |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          | Stop List:                                                                                     | spectre                                                                                                                                                                                               |       |

| Open Edit                                                                                                                       |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          | Constraint List:                                                                               | -01                                                                                                                                                                                                   | C     |

|                                                                                                                                 |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          |                                                                                                | 3560                                                                                                                                                                                                  | _     |

|                                                                                                                                 |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          |                                                                                                |                                                                                                                                                                                                       |       |

| Table View                                                                                                                      | Tree View                                                                                                                                                              |                                                                                                                                                                                                                                                                                          |                                                                                                |                                                                                                                                                                                                       |       |

|                                                                                                                                 |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          |                                                                                                |                                                                                                                                                                                                       |       |

| Cell Bindings                                                                                                                   |                                                                                                                                                                        | EL                                                                                                                                                                                                                                                                                       |                                                                                                |                                                                                                                                                                                                       |       |

|                                                                                                                                 | CellSras                                                                                                                                                               | CP<br>View Found                                                                                                                                                                                                                                                                         | View To Us                                                                                     | se Inherited View List                                                                                                                                                                                |       |

| Cell Bindings<br>Library<br>amsPLL                                                                                              | Cell<br>PLL_160MHZ_MDIV                                                                                                                                                | View Found<br>schematic                                                                                                                                                                                                                                                                  | View To Us                                                                                     | se Inherited View List spectre spice veril                                                                                                                                                            |       |

| Library                                                                                                                         |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          | View To U                                                                                      |                                                                                                                                                                                                       |       |

| Library<br>amsPLL                                                                                                               | PLL_160MHZ_MDIV                                                                                                                                                        | schematic                                                                                                                                                                                                                                                                                | View To U                                                                                      | spectre spice veril                                                                                                                                                                                   |       |

| Library<br>amsPLL<br>amsPLL                                                                                                     | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV                                                                                                                                     | schematic<br>schematic                                                                                                                                                                                                                                                                   | aser                                                                                           | spectre spice veril<br>spectre spice veril                                                                                                                                                            |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL                                                                                           | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST                                                                                                                         | schematic<br>schematic<br>schematic<br>verilog<br>verilog                                                                                                                                                                                                                                | schematic                                                                                      | spectre spice veril<br>spectre spice veril<br>spectre spice veril                                                                                                                                     |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL                                                                                 | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG                                                                                                         | schematic<br>schematic<br>schematic<br>verilog<br>verilog<br>schematic                                                                                                                                                                                                                   | schematic<br>et Cell View                                                                      | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril                                                                                                              |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL_test                                                                  | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP                                                                                               | schematic<br>schematic<br>schematic<br>verilog<br>verilog<br>schematic<br>schematic                                                                                                                                                                                                      | schematic<br>schematic<br>et Cell View<br>splain                                               | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril                                                                                       |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL_test<br>amsPLL                                                        | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP<br>PLL_PFD                                                                                    | schematic<br>schematic<br>verilog<br>verilog<br>schematic<br>schematic<br>schematic                                                                                                                                                                                                      | schematic<br>schematic<br>et Cell View<br>splain<br>pen                                        | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br><none><br/>layout<br/>schematic</none>                                             |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL_test<br>amsPLL<br>amsPLL                                              | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP<br>PLL_PFD<br>PLL_VCO_320MHZ                                                                  | schematic<br>schematic<br>verilog<br>verilog<br>schematic<br>schematic<br>schematic                                                                                                                                                                                                      | schematic<br>schematic<br>et Cell View<br>splain                                               | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>onne><br>layout<br>schematic<br>symbol                                             |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL_test<br>amsPLL<br>amsPLL<br>amsPLL                                    | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP<br>PLL_PFD<br>PLL_VCO_320MHZ<br>PLL_VCO_320MHZ                                                | schematic<br>schematic<br>verilog<br>verilog<br>schematic<br>schematic<br>schematic<br>schematic                                                                                                                                                                                         | schematic<br>schematic<br>et Cell View<br>splain<br>pen                                        | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>sout<br>schematic<br>symbol<br>verilog                                             |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL_test<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL                          | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP<br>PLL_PFD<br>PLL_VCO_320MHZ<br>PLL_VCO_320MHZ<br>PLL_VCO_CMOSD                               | schematic<br>schematic<br>verilog<br>verilog<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic                                                                                                                                                                            | schematic<br>et Cell View<br>eplain<br>pen<br>pen (Read-Only)                                  | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br><none><br/>layout<br/>schematic<br/>symbol<br/>verilog<br/>veriloga</none>         |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL           | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP<br>PLL_PFD<br>PLL_VCO_320MHZ<br>PLL_VCO_320MHZ<br>PLL_VCO_CMOSD<br>PLL_VCO_INV                | schematic<br>schematic<br>schematic<br>verilog<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic                                                                               | schematic<br>schematic<br>plain<br>pen<br>pen (Read-Only)<br>dd Stop Point<br>emove Stop Point | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>sone><br>layout<br>schematic<br>symbol<br>verilog<br>veriloga<br>verilogams        |       |

| Library<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL<br>amsPLL | PLL_160MHZ_MDIV<br>PLL_160MHZ_PDIV<br>PLL_ARST<br>PLL_ARST_DIG<br>PLL_CP<br>PLL_PFD<br>PLL_VCO_320MHZ<br>PLL_VCO_320MHZ<br>PLL_VCO_CMOSD<br>PLL_VCO_INV<br>PLL_VCO_REG | schematic<br>schematic<br>schematic<br>verilog<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic<br>schematic | schematic<br>schematic<br>et Cell View<br>splain<br>sen<br>sen (Read-Only)<br>dd Stop Point    | spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>spectre spice veril<br>sone><br>layout<br>schematic<br>symbol<br>verilog<br>veriloga<br>SPICE Source File |       |

2013 *Graser* Augu **User** TAPEL **Conference**

#### **AMS Designer Multiple Tests**

Can set simulations running in parallel or series in ADE

| ADE XL Test Editor - amsPLL_test_1PLL_160MH7z_LF:1 _ X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C Virtuoso® Analog Design Enviror                                                                                                                                                   | nment XL Editing: amsPLL_test_1 PL                                                                                                                                     | L_160MHZ_LF adexl                                                                                                                                      | _ 0     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Session Setup Analyses Variables Quiputs Simulation Câdence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Launch <u>File</u> <u>Create</u> <u>T</u> ools <u>O</u> ptions R <u>u</u> n Pa <u>r</u> asit                                                                                        | tics <u>W</u> indow <u>H</u> elp                                                                                                                                       | SEP                                                                                                                                                    | cādence |

| Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                     | »                                                                                                                                                                      | space: Basic                                                                                                                                           | - 5.    |

| Name         Spration         Setup         Analyses         Question         Câdence           Image: Spration         Image: S | No Parasitics Vo Sweeps                                                                                                                                                             | 🔨 🛄 📗 Single Run, Sweeps and                                                                                                                                           | Corners 🧧 🗞 🚸 I                                                                                                                                        | 0) 🗘    |

| Design of state         Value           If SSP         2544           If SSP         2544 <t< td=""><td>Data View  C  S Tests amsPLL_test_1:PLL_160MHZ_LF:1 amsPLL_test_1:PLL_160MHZ:1 amsPLL_test_1:PLL_NDVR:1</td><td>Detail a Salar 💽 🎨 🎞</td><td>Diagnostics</td><td>• »</td></t<>                                                                                                                                                                                                                                                                                                                                           | Data View  C  S Tests amsPLL_test_1:PLL_160MHZ_LF:1 amsPLL_test_1:PLL_160MHZ:1 amsPLL_test_1:PLL_NDVR:1                                                                             | Detail a Salar 💽 🎨 🎞                                                                                                                                                   | Diagnostics                                                                                                                                            | • »     |

| Solution L<br>Solution L<br>Solution L<br>Solution Ready Tract C Simulator sam(SpectrupAPS Moder batch   State semPLL_bard_TPLL_1000MC GT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Global Variables<br>Global Variables<br>Global Variables<br>Global Variables<br>Global Variables<br>Global Variables<br>Global Variables<br>Corners<br>Documents<br>Data<br>History | Test<br>amsPLL_test_1:PLL_160MHZ_LF:1<br>amsPLL_test_1:PLL_160MHZ_LF:1<br>amsPLL_test_1:PLL_160MHZ_LF:1<br>amsPLL_test_1:PLL_160MHZ:1<br>amsPLL_test_1:PLL_160MHZ:1    | /DUMP 🗠                                                                                                                                                | Spec A  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Run Summary     ? 健 ×       3 Tests     ✓       ✓     1 Point Sweep       ✓     0 Corner       ✓     Nominal Corner                                                                 | amsPLL_test_1:PLL_160MHZ:1<br>amsPLL_test_1:PLL_NDVR:1<br>amsPLL_test_1:PLL_NDVR:1<br>amsPLL_test_1:PLL_NDVR:1<br>amsPLL_test_1:PLL_NDVR:1<br>amsPLL_test_1:PLL_NDVR:1 | /CLK_160MHZ         L           /IPLY_25u         L           /VSS         L           /VREF         L           /DN         L           /PD         L |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | History Item                                                                                                                                                                        | Interactive.8                                                                                                                                                          | ve.9                                                                                                                                                   | ×       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Immouse L:<br>31(56) Build Estimated View                                                                                                                                           | . М:                                                                                                                                                                   |                                                                                                                                                        | F       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |                                                                                                                                                                        | 2013 Graser<br>AUG User<br>TAIPEL Confe                                                                                                                | erence  |

#### **Virtuoso AMS Designer**

- Mixed Signal Design Verification

- High performance and accuracy

## **AMS Verification in Virtuoso**

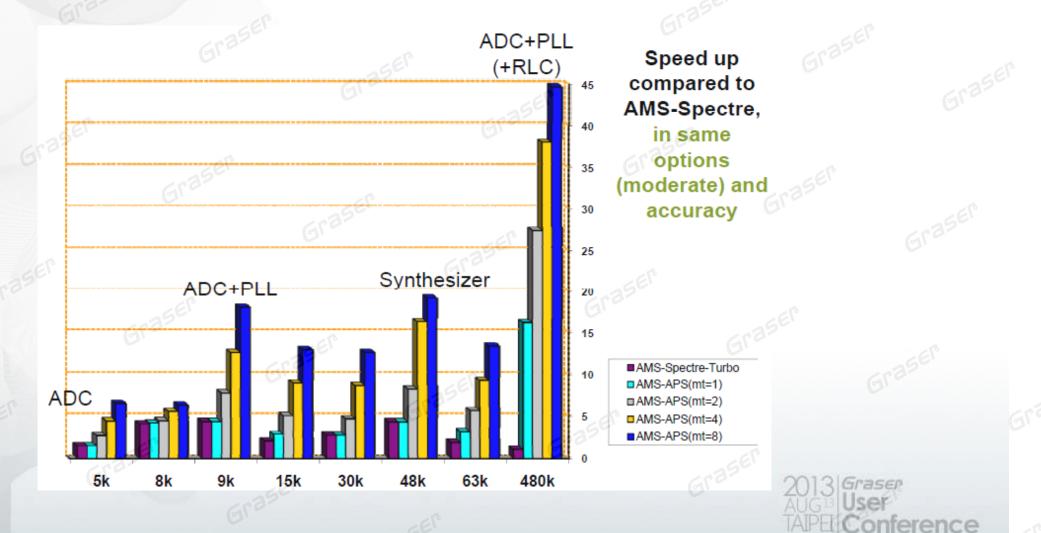

#### **AMS Designer-APS Key Features**

- APS Integration with AMS Designer

- Full Spectre accuracy

- Fully compatible with Spectre Solver

- Improved capacity compared to AMS-Spectre

- Maximum simulation performance with multi-threading support on multi-core/multi-CPU systems

- Simplified use model for command line (irun/ncsim) and ADE usage

## **AMS Verification in Virtuoso**

#### **Virtuoso AMS Designer-APS**

- Performance and Capacity improvement

- More performance gain with larger device count

## **AMS Verification in Virtuoso**

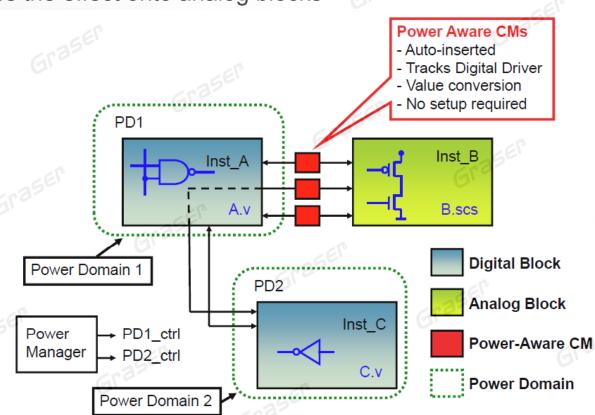

#### **Mixed-Signal Low Power support**

- Support for multiple-voltage power domains

- Power Smart connect module carries the effect of power shut-off, power active state conditions, power modes and transitions onto analog blocks

- Simulator identifies the CPF influence on analog blocks

- Automatically Inserts "Power-Smart" Connect modules

- Carries the effect onto analog blocks

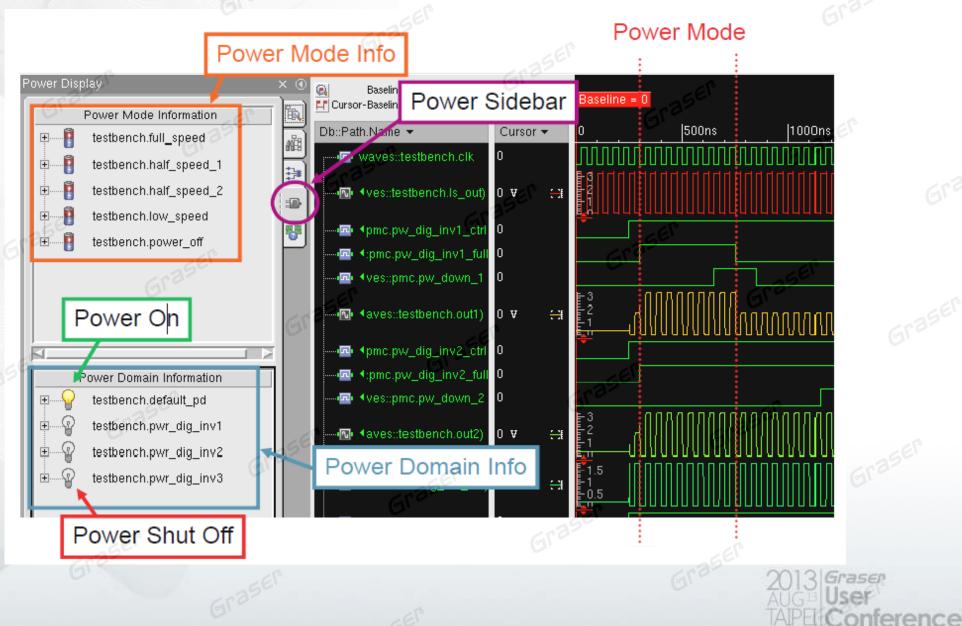

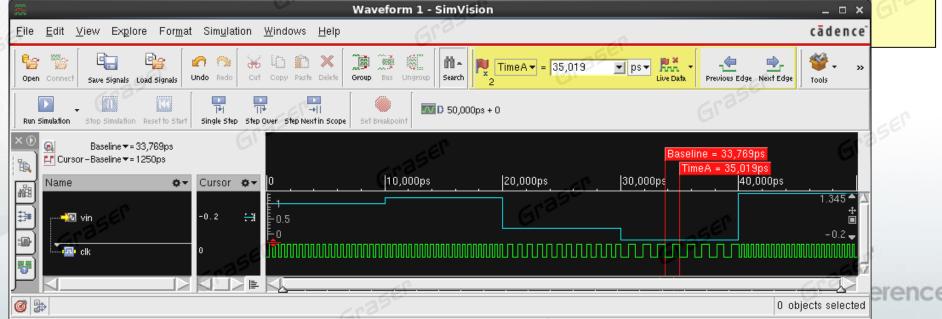

#### Low Power Info in SimVision

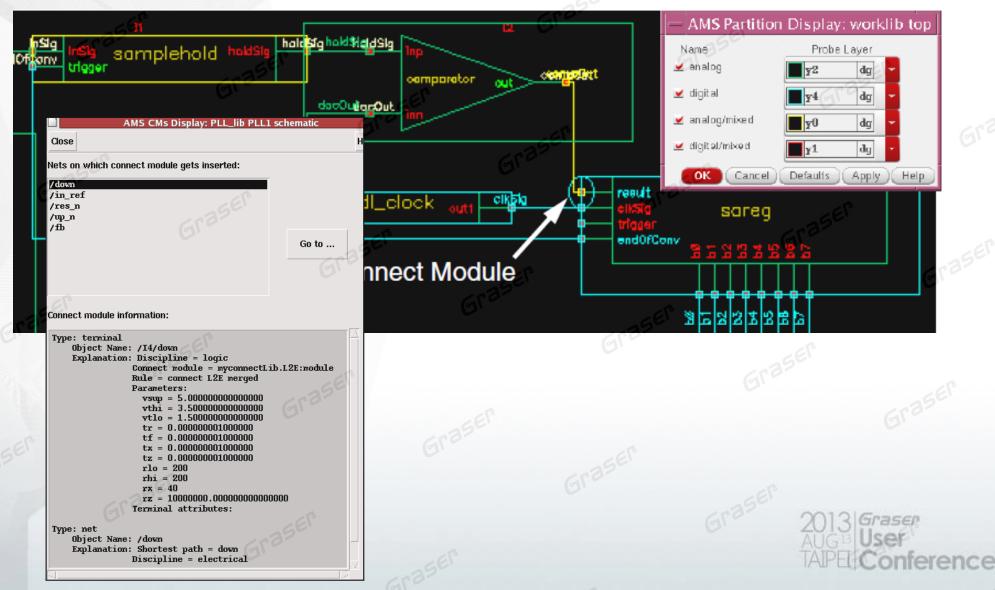

#### **Display domains and connect modules**

Show Info on the schematic after simulation

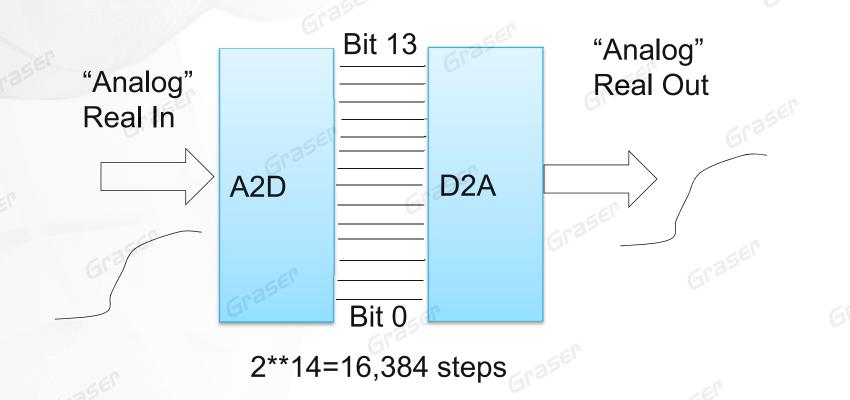

## **Digital-centric Verification**

**AMS Designer Verification in Incisive**

## **Digital Centric Mixed Signal Use Model**

## Mixed Signal Packaging Proposal for Digital Centric Model

#### Real Value "IP Usage" Use Model

- Create a New mixed signal market segment for Cadence

- Digital Mixed Signal (DMS)

- Provide a Real Value Modeling capability for digital centric use model

- Extremely high performance behavioral Mixed Signal verification

- BigD/SmallA full-chip verification

- Enable high volume digital-centric nightly regressions tests

- Allows customers to perform SoC Top-level mixed signal verification using only digital simulators

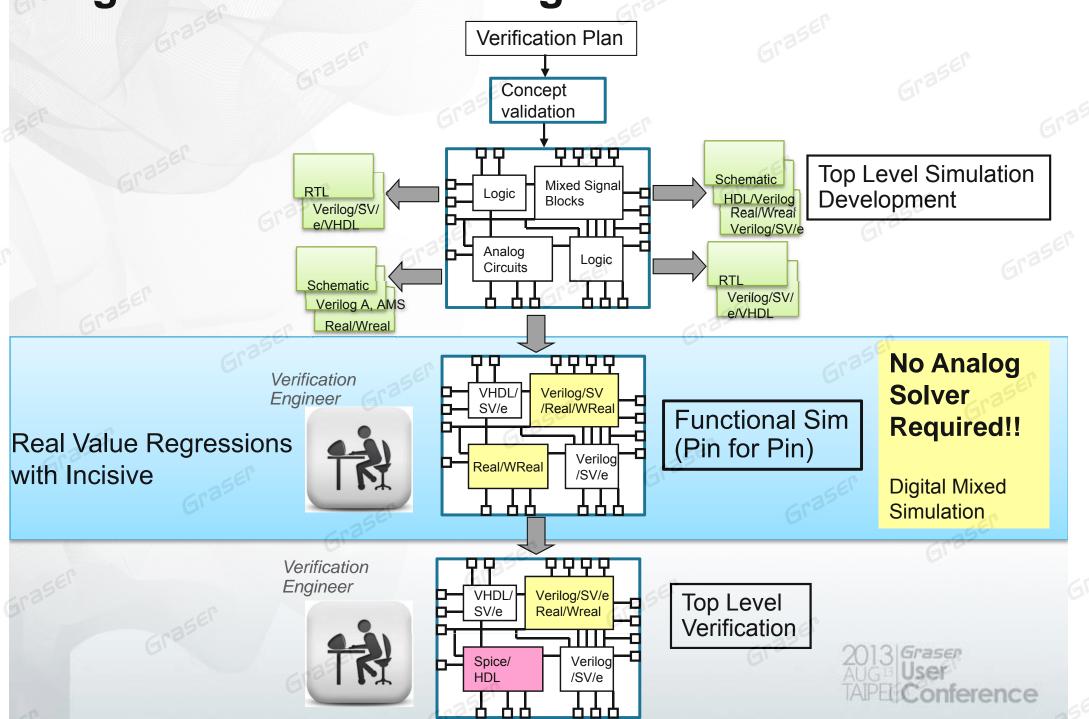

## What's Real Number Modeling?

- Model analog blocks operation as signal flow models

- Digital only simulation  $\rightarrow$  remains high simulation performance

- Use the event solver for fast calculation and avoid convergence issues

- wreal ports in Verilog-AMS or

- Note: wreal is defined only in the verilog-ams standard, however, only the digital kernel is used for simulation

- real in VHDL or

- real in SystemVerilog

## **Real Modeling Concept**

3 simulation paradigms in Mixed Signal:

#### 1. Event simulation

Digital blocks

#### 2. Analog solver: solve differential equations

- Accurate analog simulation based on circuit theory; ohms law, kirchoff's law

- E.g. SPICE, transistor level

- 3. Signal-flow simulation

- Analog and mixed-signal simulation based on behavioral models

## **Real Value Model Example**

#### **14bits ADC + 14bits DAC complete transfer**

HDL-A using "real" model: 3 seconds!

Full transistor level simulation could take days ...

## **Improve Analog/MS Simulation Performance**

- Transistor level ideal circuit (1.0 x)

- Fast spice simulation (5-20 x)

- Analog behavioral modeling (5-100 x)

- Real number modeling (50-500 x)

- Pure digital model (500-10K x)

## **Digital-Centric Mixed-Signal Verification**

#### **Improves top-level SoC verification**

- High-performance, real-number modeling for mixed-signal verification

- Run full-chip verification regression suites at digital speeds

- Enabled by Incisive Digital Mixed-Signal (DMS) Option

- Cadence extensions to Verilog-AMS "wreal" feature donated to Accellera

## **The Wreal Datatype in Verilog-AMS**

- Wreal datatype declares a real net that has a real-valued connection to other modules

- A wreal net is discrete in time (event based, see the @(vin))

- It is continuous in value real

module vco(vin, clk); input vin; wreal vin; output clk; reg clk; real freq,clk\_delay; always @(vin) begin freq = center\_freq + vco\_gain\*vin; clk\_delay = 1.0/(2\*freq); end always #(clk\_delay) clk = ~clk;

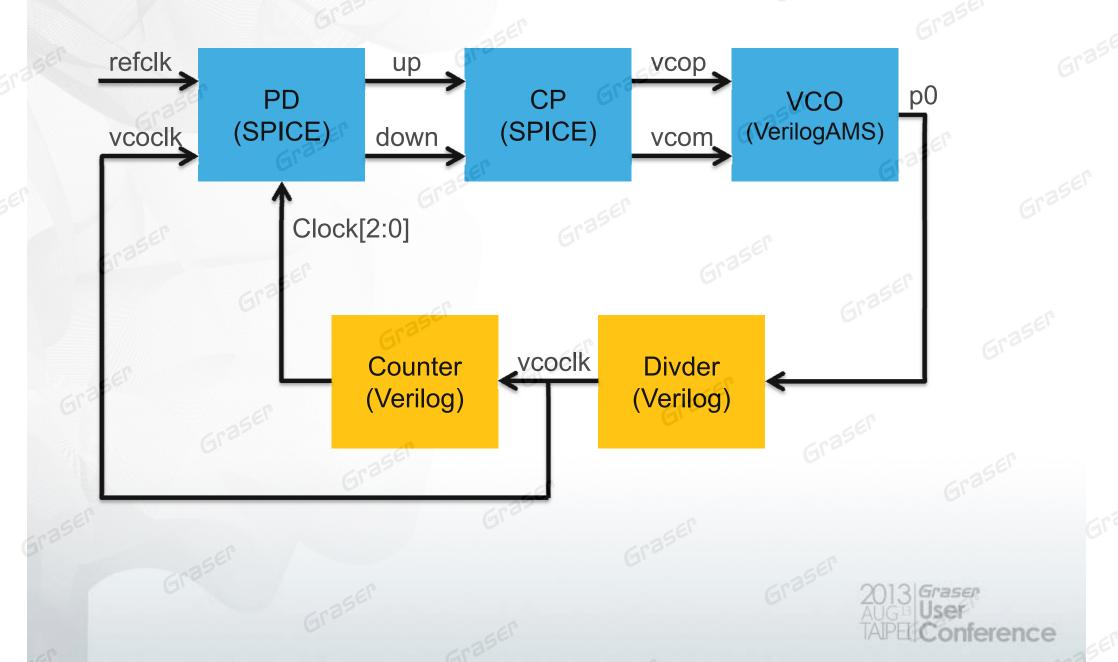

## **Digital-Centric Mixed-Signal Use Model**

# PLL Example with SPICE, Verilog-AMS and Verilog Languages

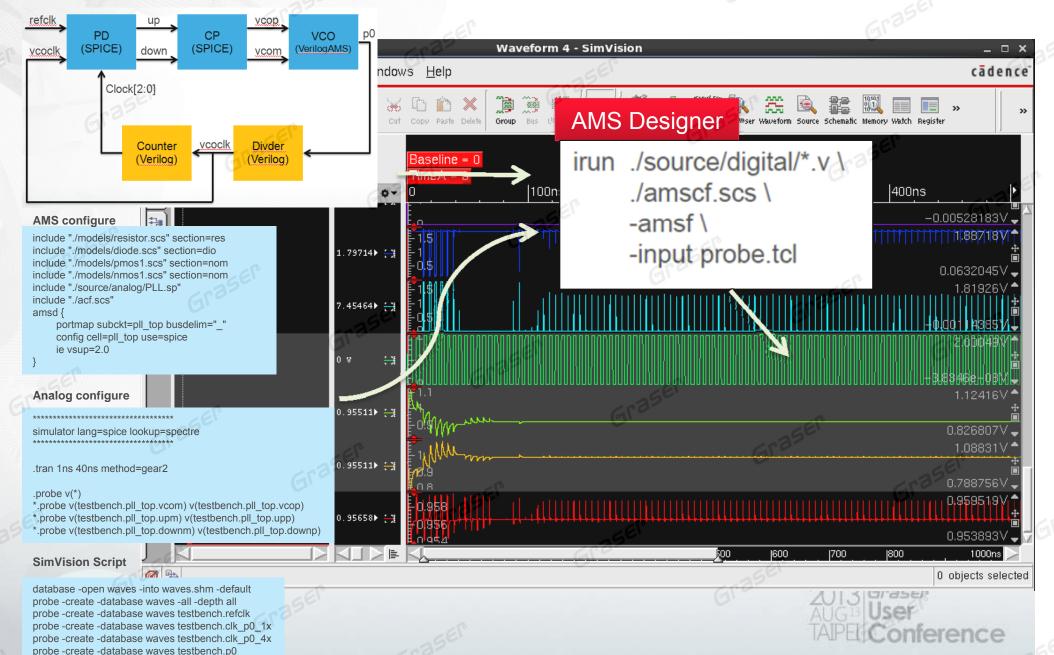

### **File Preparation for Signal-Step Verification Flow**

#### **AMS Control File, Analog Control File and Digital Probing TCL File**

#### Analog configure

simulator lang=spice lookup=spectre

.tran 1ns 40ns method=gear2

#### .probe v(\*)

\*.probe v(testbench.pll\_top.vcom) v(testbench.pll\_top.vcop)

\*.probe v(testbench.pll\_top.upm) v(testbench.pll\_top.upp)

\*.probe v(testbench.pll\_top.downm) v(testbench.pll\_top.downp)

#### **SimVision Script**

database -open waves -into waves.shm -default probe -create -database waves -all -depth all probe -create -database waves testbench.refclk probe -create -database waves testbench.clk\_p0\_1x probe -create -database waves testbench.clk\_p0\_4x probe -create -database waves testbench.p0

#### **AMS configure**

include "./models/resistor.scs" section=res include "./models/diode.scs" section=dio include "./models/pmos1.scs" section=nom include "./models/nmos1.scs" section=nom include "./source/analog/PLL.sp" include "./acf.scs" amsd {

portmap subckt=pll\_top busdelim="\_"

config cell=pll\_top use=spice

ie vsup=2.0

2013 Graser AUGI User TAIPEL Conference

## Mixed-Signal Flow for Digital-Centric Verification with Spice File

## Summary

- Virtuoso AMS Designer is the integration of Virtuoso MMSIM and IES Simulators

- Two Facets for AMS Verification

- Virtuoso GUI integration

- Incisive batch mode

- Auto-inserted Connect Module Library

- AMS-APS Analog Solver Multi-threading Support and retaining SPICE accuracy

- Addressing Low Power Requirements

- Reduces re-spins

- Leverages high-performance, real-number modeling

- Performs SoC top-level mixed-signal verification

- Finds and fixes errors much earlier in the design cycle by performing fullchip functional verification

- Boosts productivity

- Eliminates convergence issues with digital-speed performance

- Easily and accurately ports models between Virtuoso® and Incisive® environments

- Achieves top-level verification