# **Topic**

- Overview

- Challenges

- Cadence's Complete Solution

- Virtuoso Custom Design and Verification

- Ease and Speed to develop the largest and complex schematic

- **Virtuoso Schematic Editor**

- Fast and Accurate design verification

- Analog Design Environment

- **Multi-Mode Simulation**

- Virtuoso Custom Implement

- Rapid layout implementation

- **Virtuoso Layout Suite**

- Summary

erence

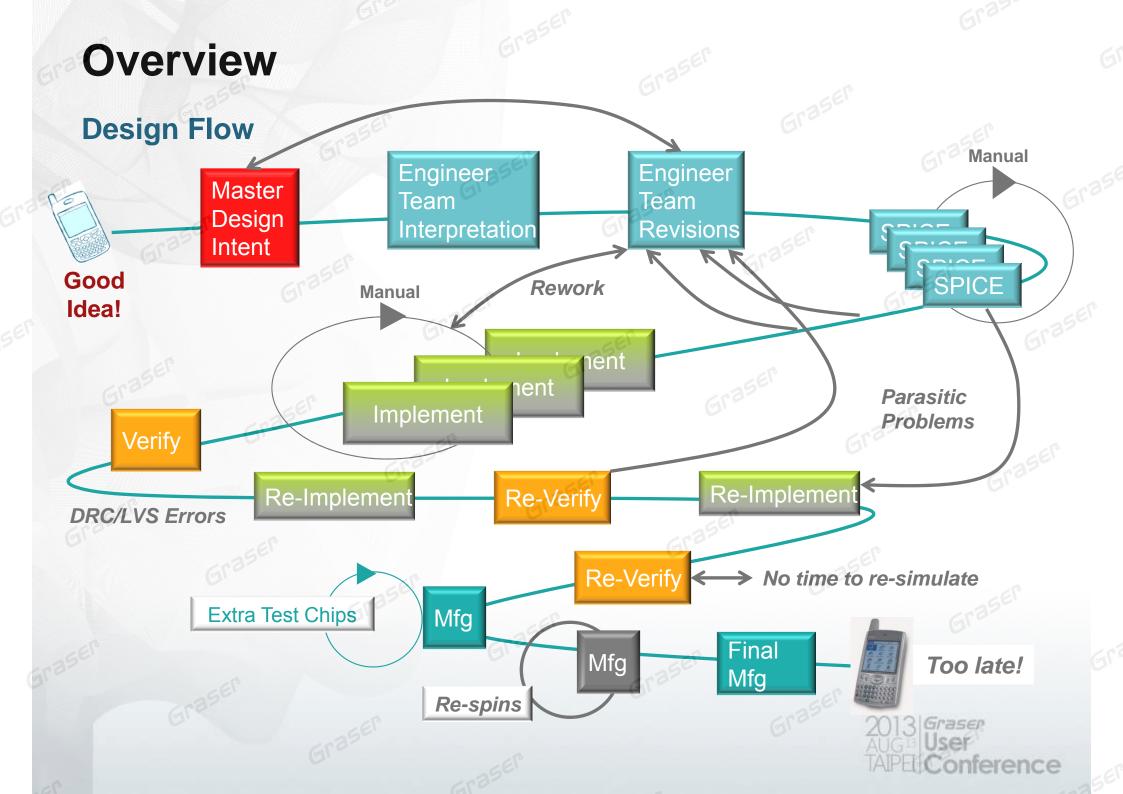

#### Overview

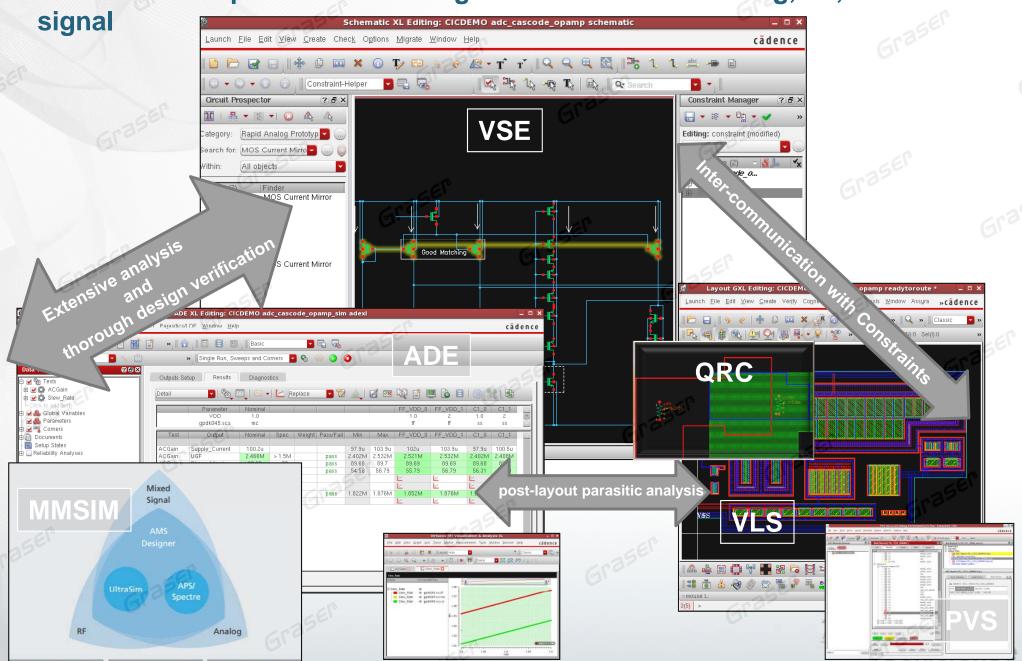

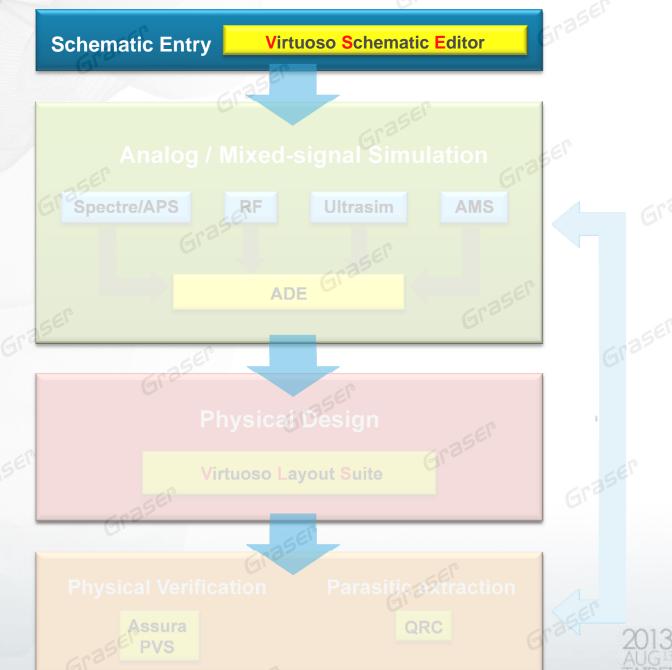

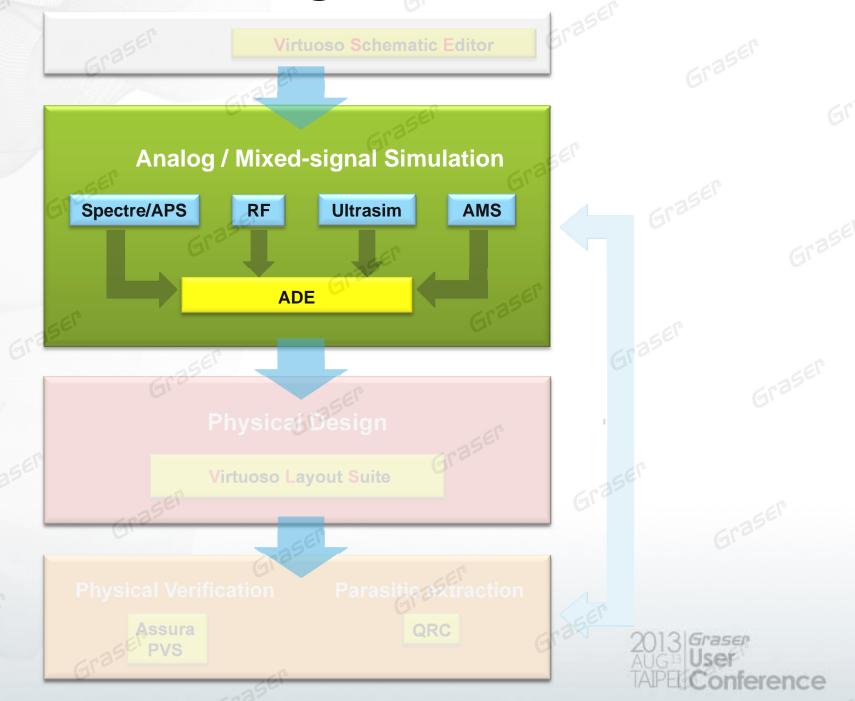

Cadence's complete custom design for front to back analog, RF, and mixed-

signal PDK **Schematic Entry** Virtuoso Schematic Editor **Schematic Symbols** & CDF Analog **Analog / Mixed-signal Simulation** Simulation (Spectre) Models Spectre/APS RF **Ultrasim AMS** & callbacks **Physical ADE** Symbols **Parameterized** Cells Techfile: Layer maps **Physical Design** Layer props Symbolics Connectivity Virtuoso Layout Suite ICC setup Verification Rules **Physical Verification Parasitic extraction** DRC LVS Assura QRC - Extraction **PVS**

#### Overview

Cadence's complete custom design for front to back analog, RF, and mixed-

Ease and Speed to develop the largest and complex schematic

Fast and Accurate design verification

2013 Graser AUG User TAPE Conference Virtuoso Custom Design and Verification

2013 Graser AUG User TAIPE Conferen

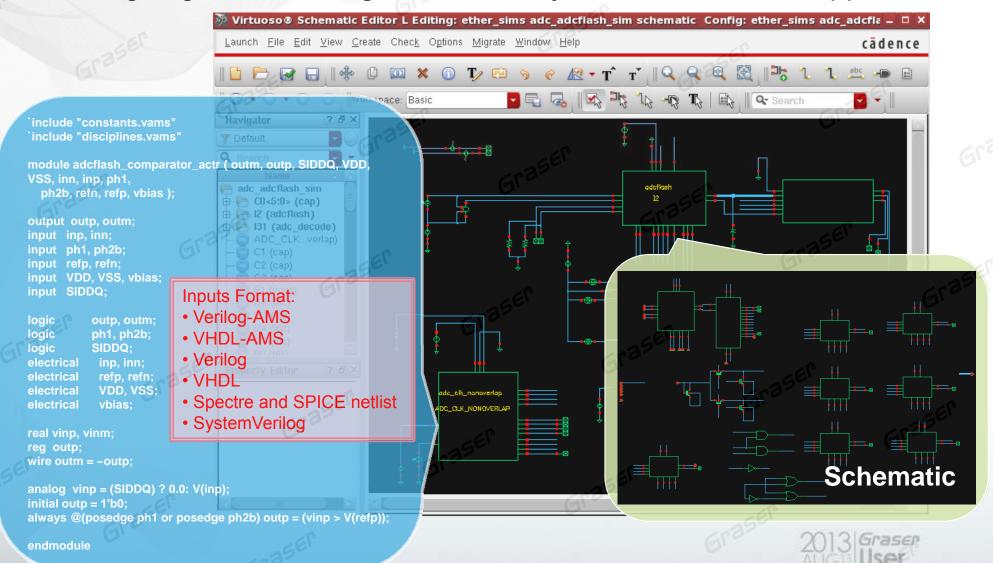

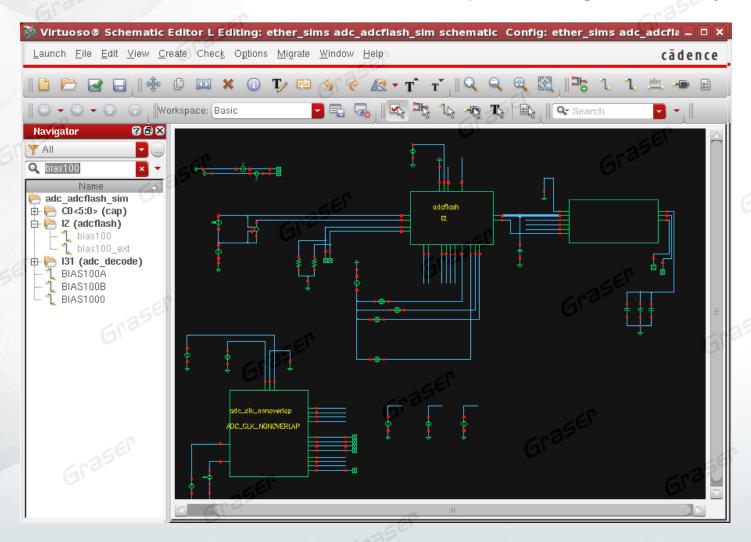

- Hierarchical schematic entry and hierarchy editor supports

- Analog, digital, mixed-signal, and RF symbol libraries are supported

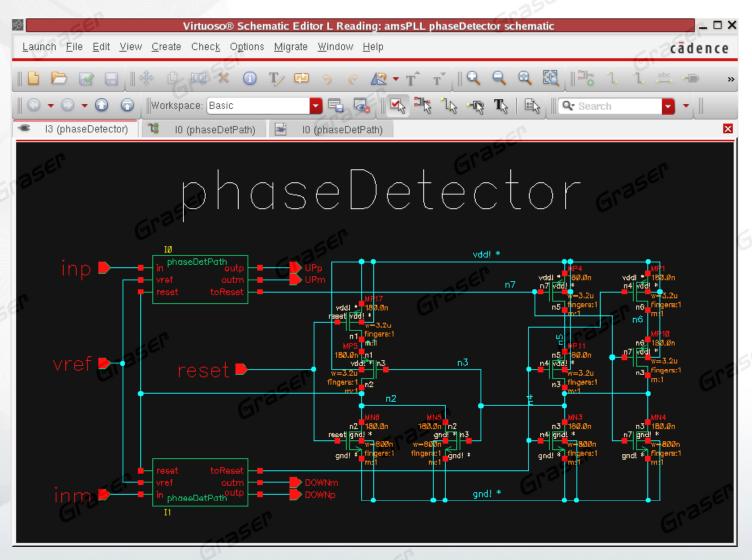

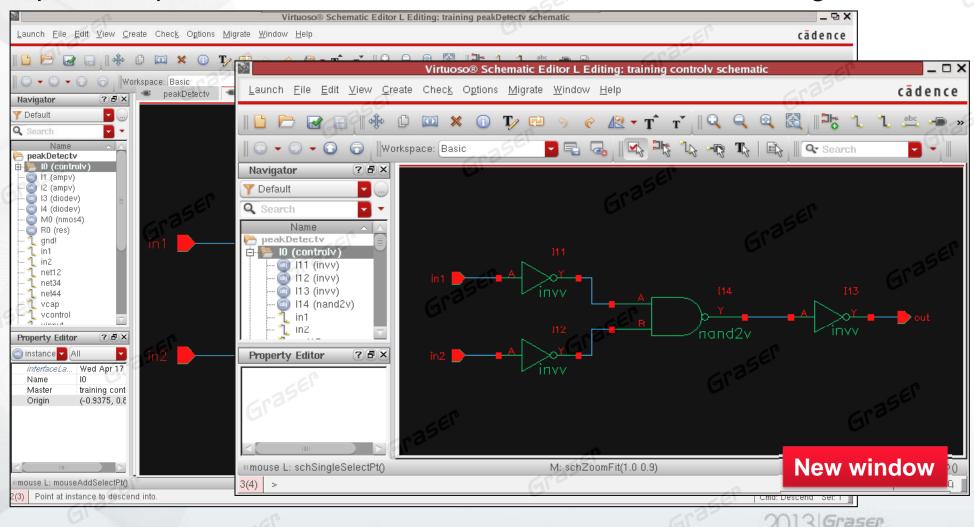

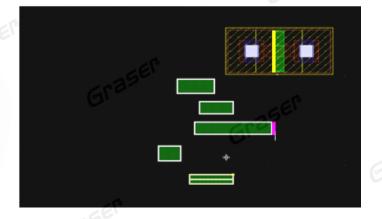

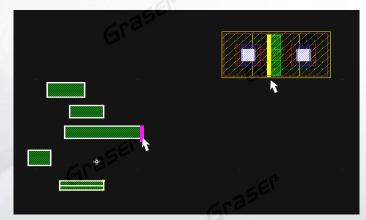

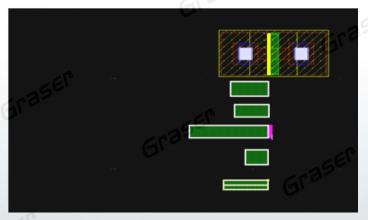

#### Multi-tab / Multi-view canvas

Open multiple schematics, or different views of the same design

#### Multi-tab / Multi-view canvas

Open multiple schematics, or different views of the same design

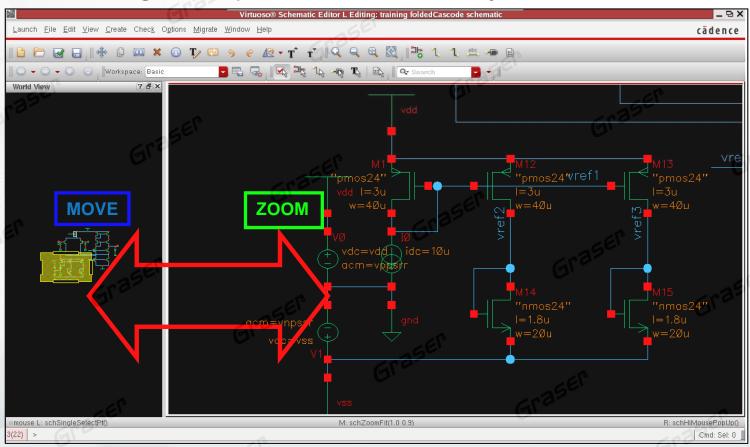

- World View Assistant

- Panoramic view of an entire schematic

- Indicating which portion of it is currently visible in the editor window

- Navigator Assistant

- Efficient, intuitive access to the complete design hierarchy

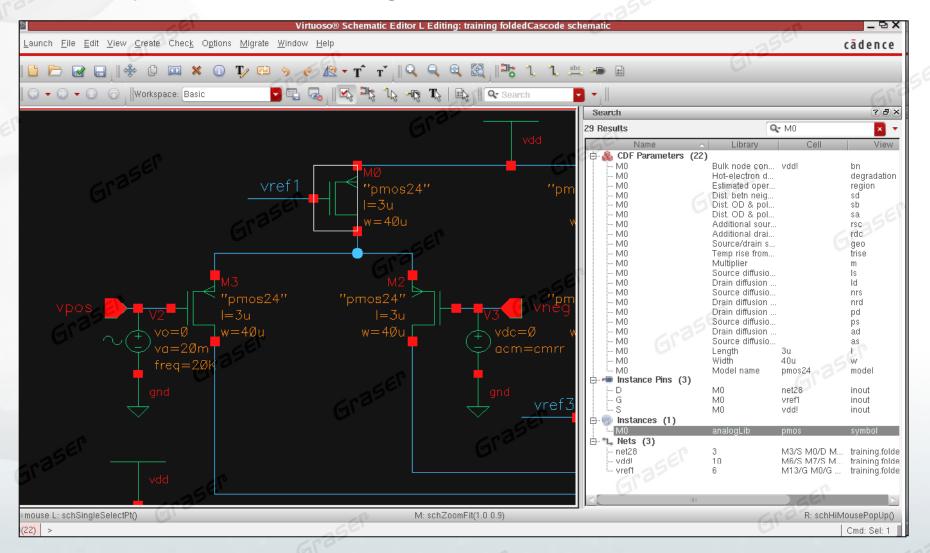

- Search Assistant

- Quick, comprehensive search engine

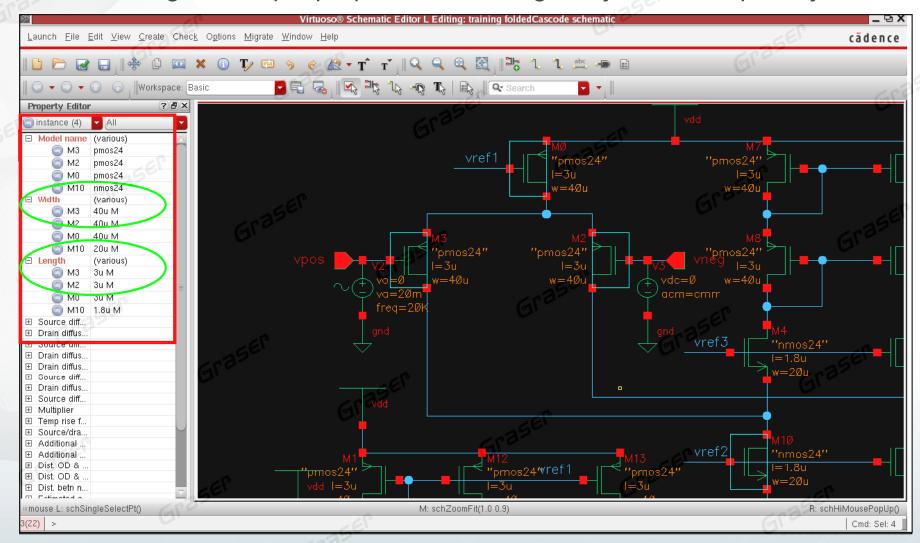

- Property Editor Assistant

- Intuitive editing of multiple properties on a single object or multiple objects

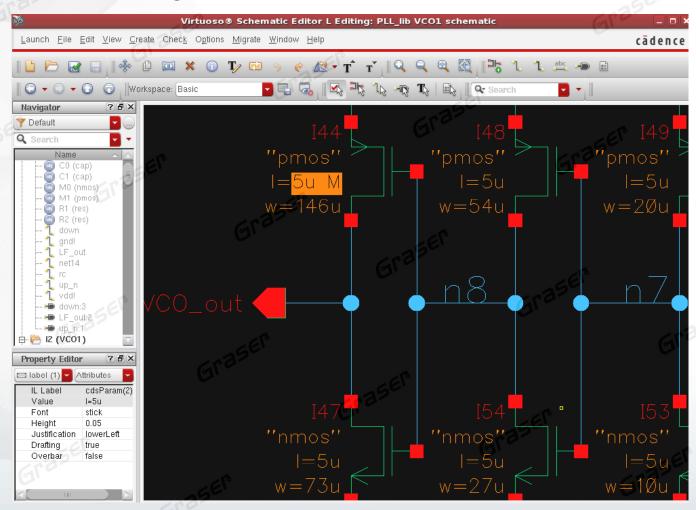

#### **Text Editing**

- Direct Text Edit

- speed to change the values of text

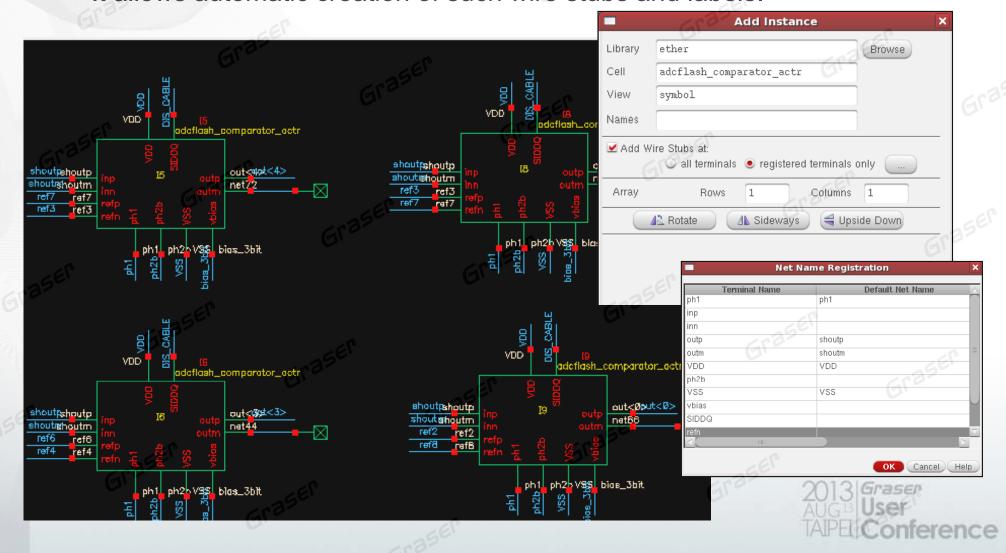

#### Automatic creation wire stubs and labels

- Wire Stubs and Names

- It allows automatic creation of such wire stubs and labels.

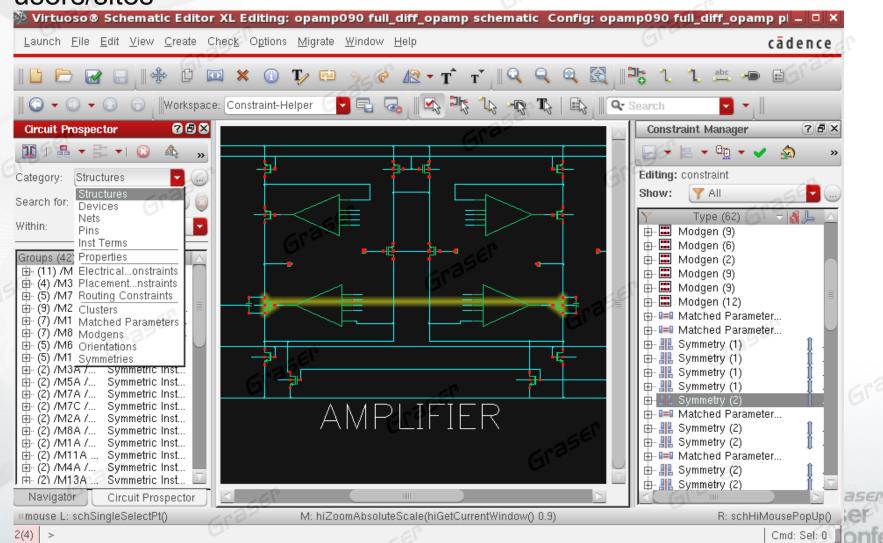

#### **Constraint environment**

Easily communicate critical design constraints between multiple users/sites

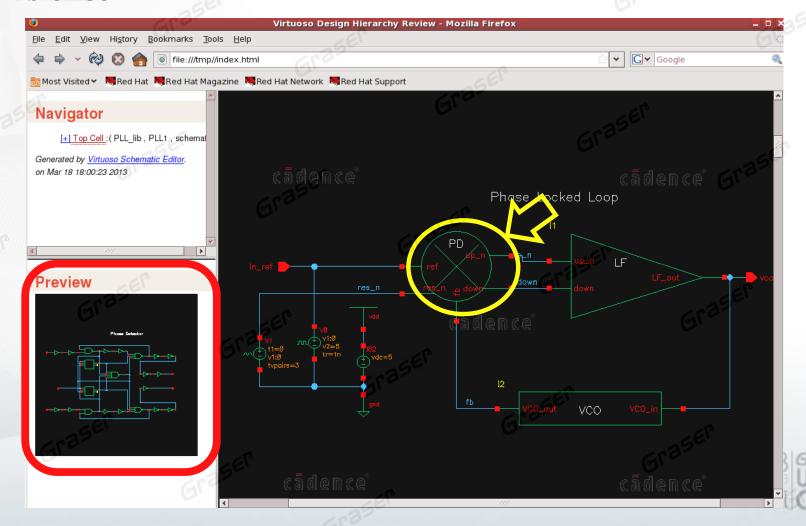

#### **Quick schematics graph output**

- HTML Publisher

- Schematic design hierarchy is published that can be displayed in a web browser

# Virtuoso Custom Design and Verification

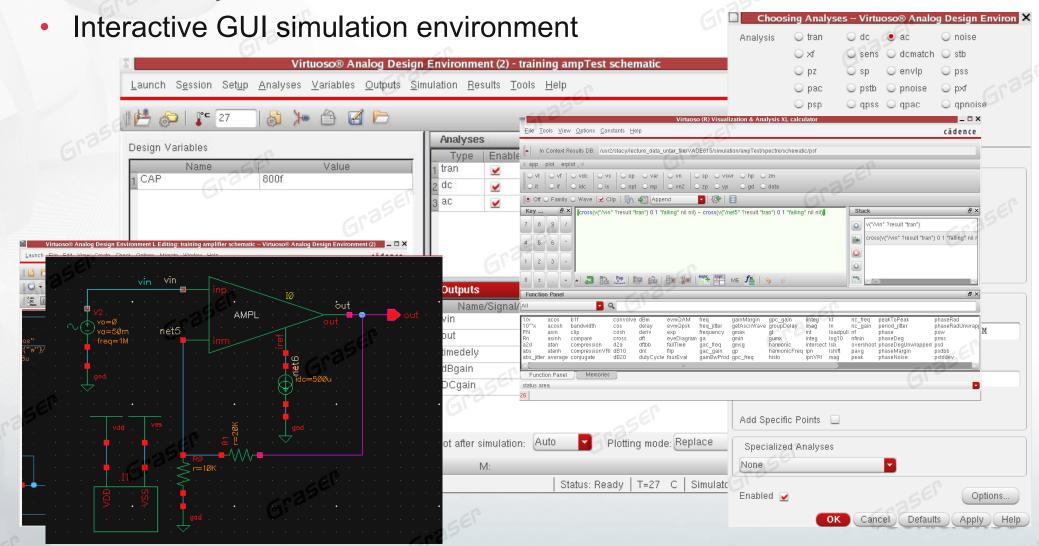

#### **Simulation GUI Window**

- Not necessary to understand netlist syntax

- Common syntax for different simulators

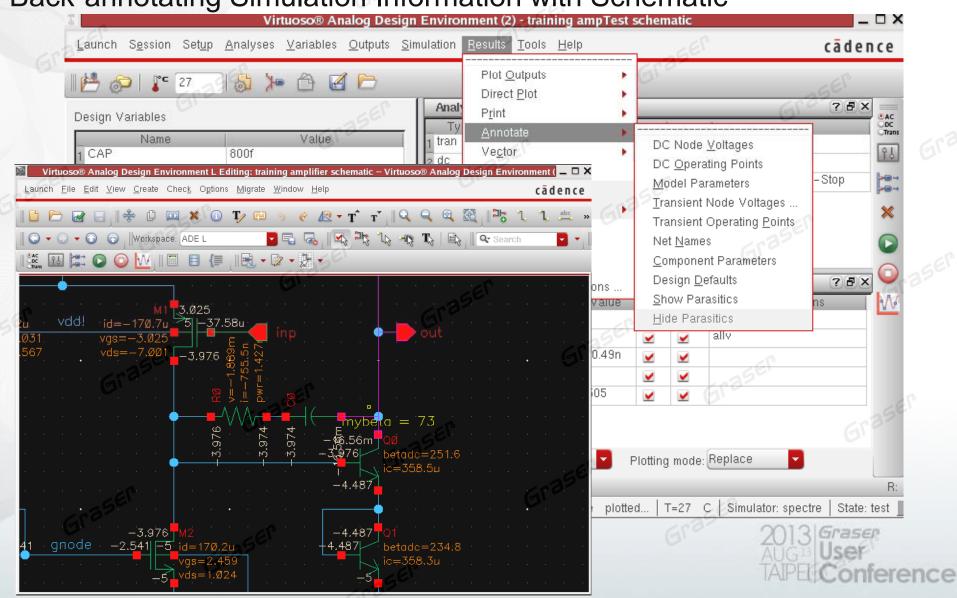

#### **Annotate**

Back-annotating Simulation Information with Schematic

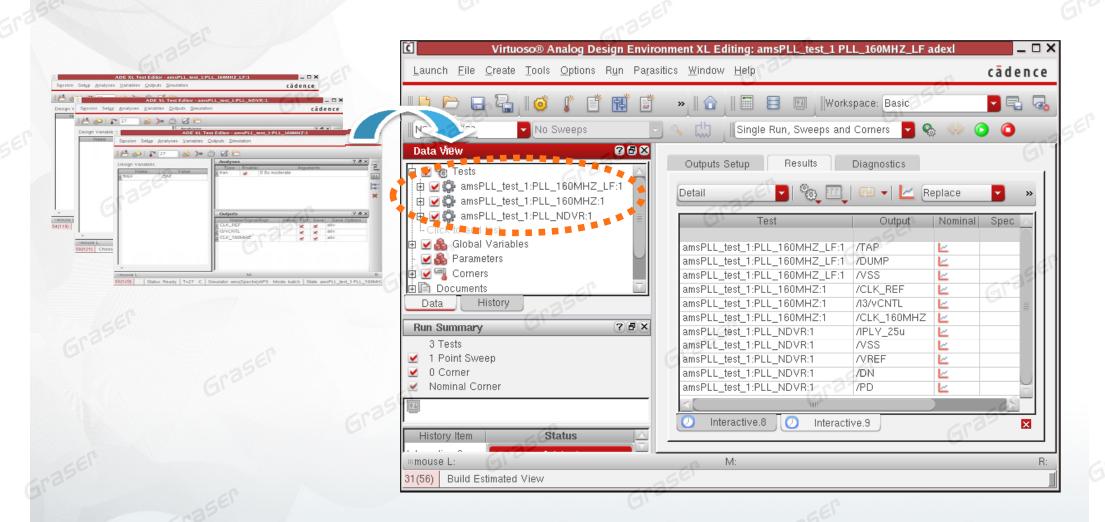

#### **Multi-test Environment**

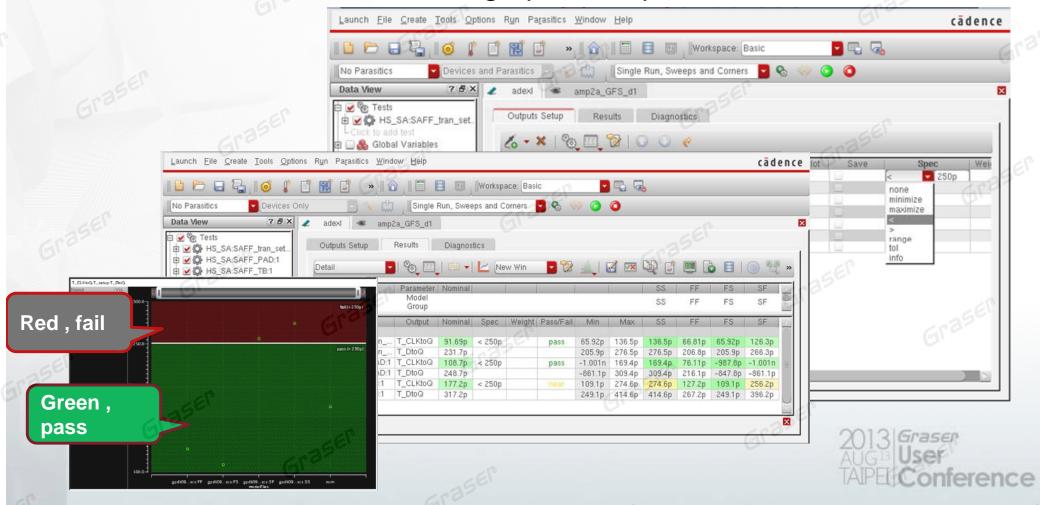

#### Specification-driven design

- Quick Spec setup

- color-coded feedback of all results against target specifications

- Intuitive overview color-coded graph with spec

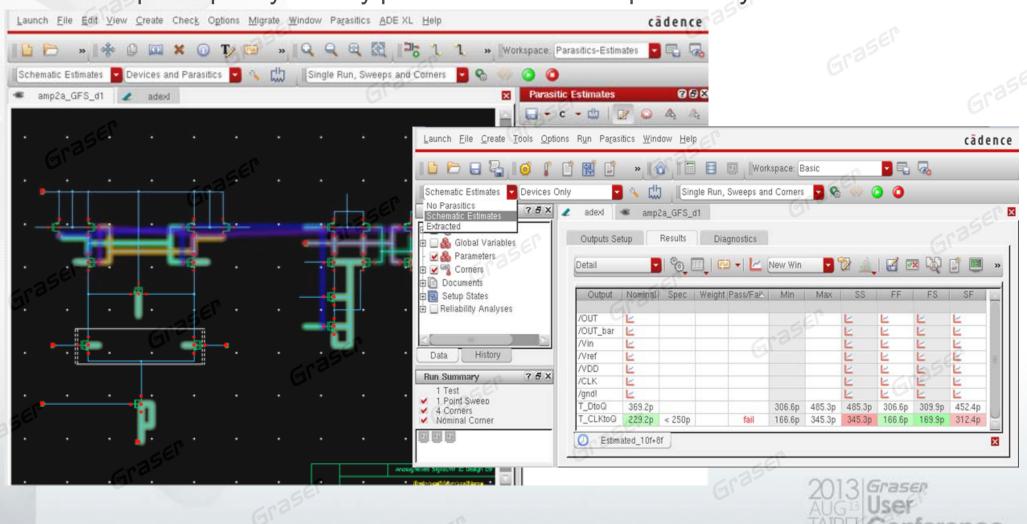

#### **Parasitic Effects**

- Parasitic Estimation

- Helps to quickly identify parasitic sensitivities prior to layout

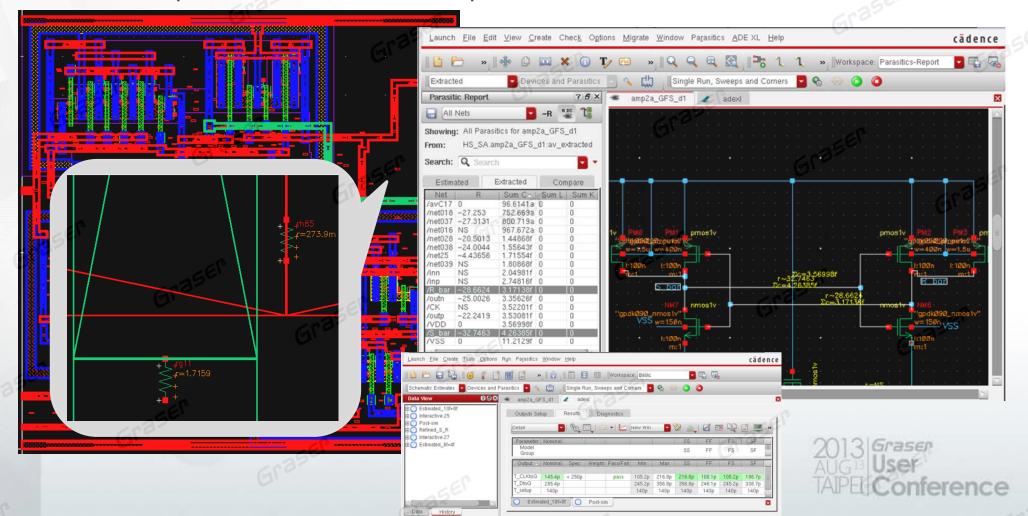

#### **Parasitic Effects**

- post-extracted layouts simulation

- Support av\_extracted file

- Show parasitic sum value on report and schematic view

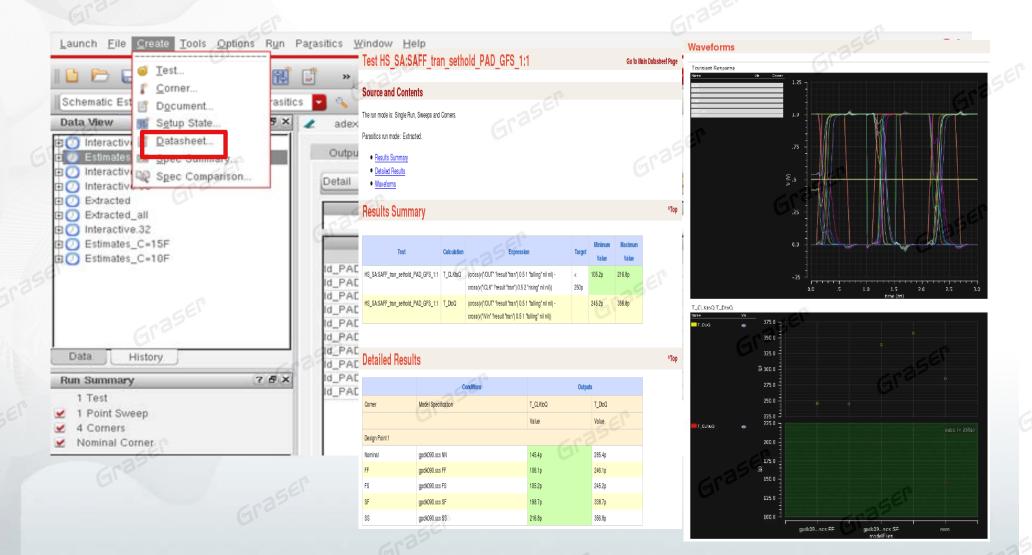

#### **Create Datasheet**

Auto-generate the output of the simulation result and graph to the datasheet

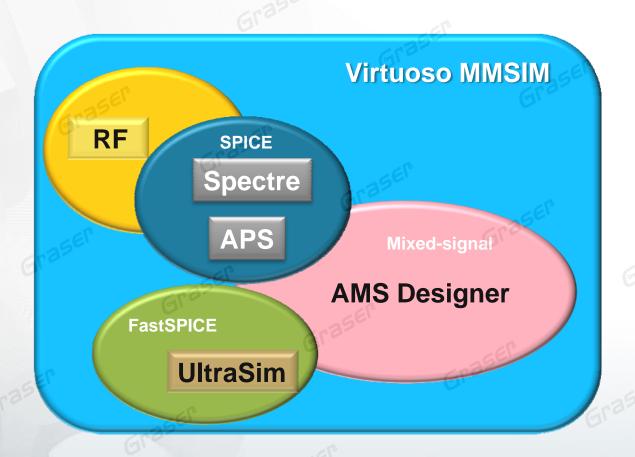

### **Multi-Mode Simulation**

- For Custom Analog and Mixed Signal Design Verification

- MMSIM with multi-core deliver to meet your performance and accuracy

- ✓ Optimized Packaging : Scalability and Flexibility

- ✓ RF Analysis

- ✓ High Performance : AMS- APS Post layout

- ✓ Common model

Virtuoso Custom Implement Spectre/APS **AMS** ADE **Physical Design** Virtuoso Layout Suite

# Agenda

- How to increase Team collaboration and productivity?

- Customize back-end IC design

- Manually

- Accelerate Placement & Editing

- Semi-Auto

- Interactive Routing

- Auto

- Constrain & Generate From Source

# How to increase Team collaboration and productivity?

- Capture requirements on How a design is intended to be implemented

- Minimize miscommunication problems with standard design team communications

- Simplify the procedure of Placement & Editing

- Resolve DRC & LVS errors

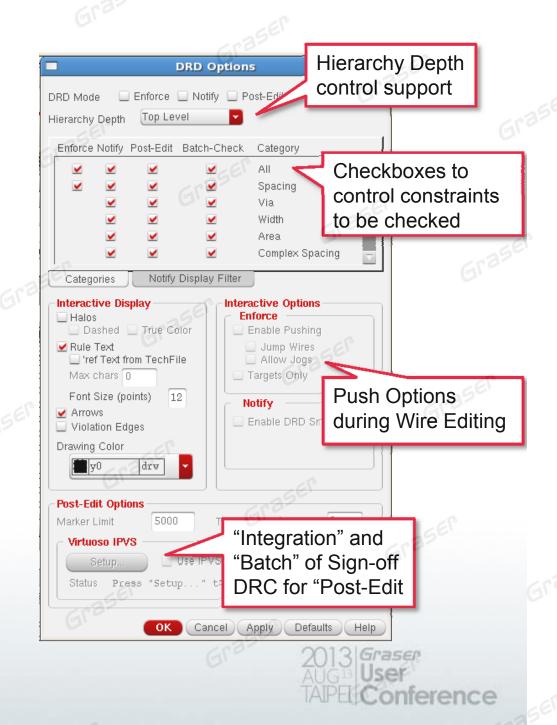

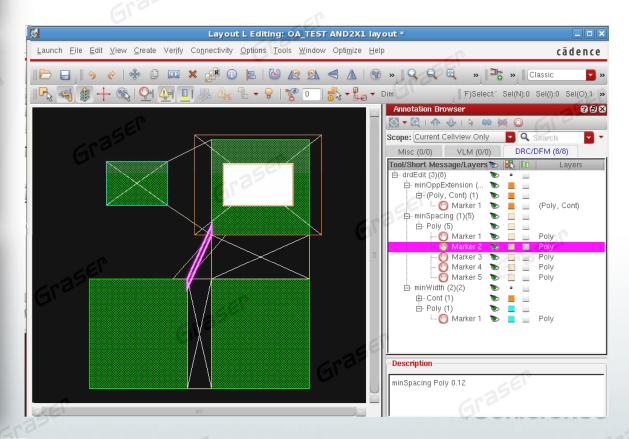

# **Design Rule Driven**

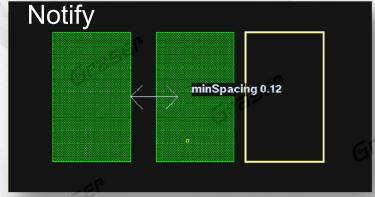

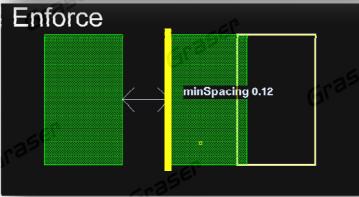

#### **Interactive Design Rule Checking**

- Real-time DRC Checking

- Automatically enforces design rules

- Eliminate physical verification iterations

- Reduce the number of DRC violations during layout editing

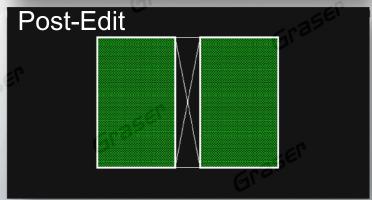

### **Design Rule Driven**

#### **Debugging DRC Violations**

- The post-edit markers can be viewed, analyzed, and filtered in the DRC/DFM tab of Annotation Browser.

- The markers are the persistent objects, which can be saved.

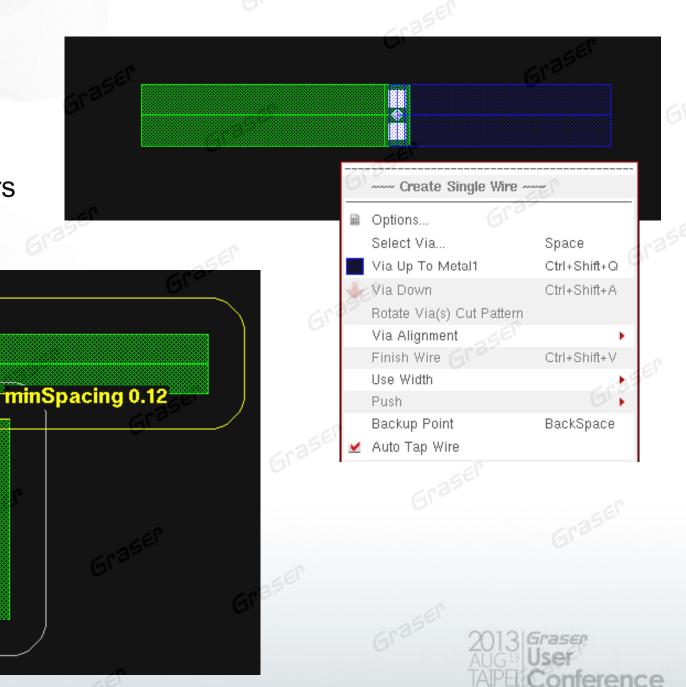

### **Wire Routing**

- Smart snapping

- Auto Tap wire

- Easy to change Layers

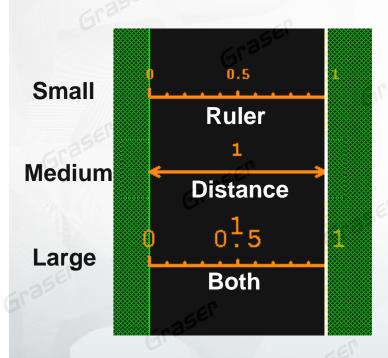

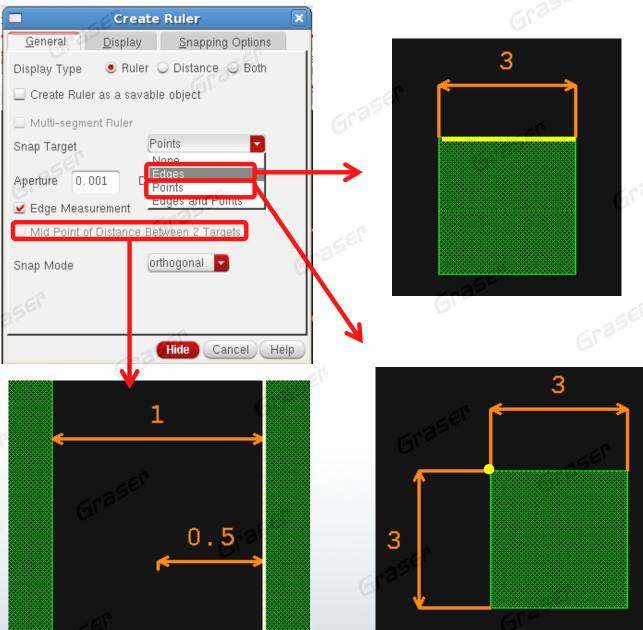

#### **Smart Ruler**

- Smart Snapping

- Multi-segments

- Customize general Ruler measurement and display type

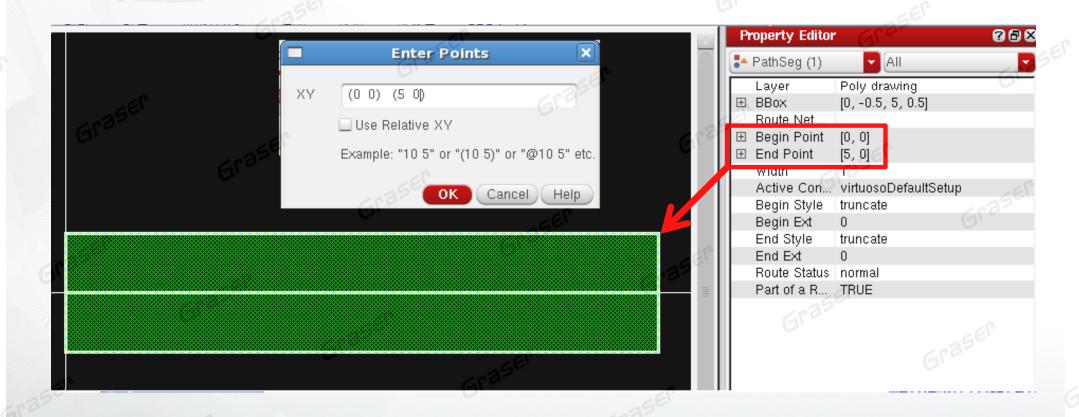

#### **Enter Points**

Easy to specify points for any of the enter function based commands like Create, Move, Stretch, Copy command...

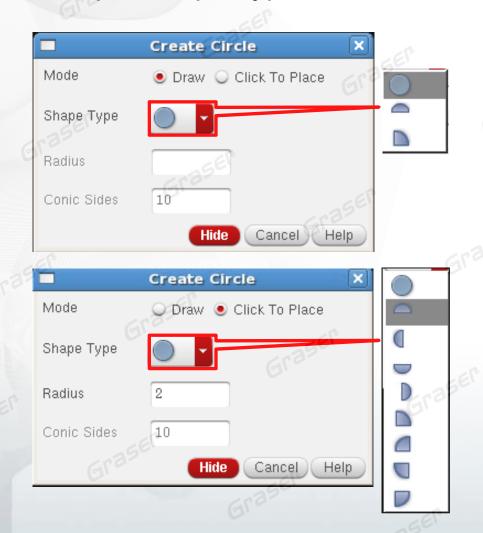

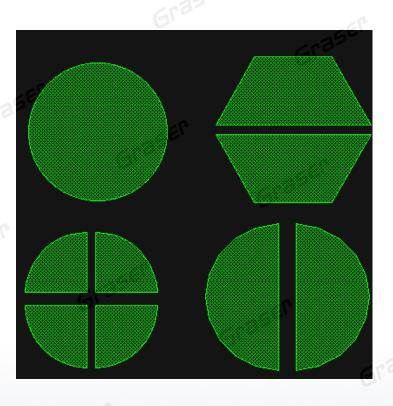

#### **Create Circle**

- Support the Mode of "Draw" and "Click To Place"

- Multiple Shape Type

#### **Create Rectangle**

- Draw mode has the Smart Snapping

- Smart to create abutting rectangles to an existing shape

- Snapping can be restricted to Current Active Layer in Layer Palette

- Easy to customize the Dimension, spacing and Edge of Slot

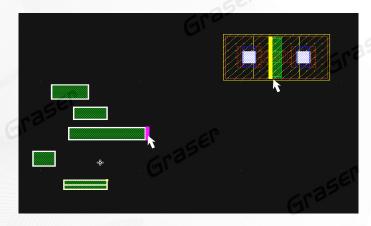

### **Quick Align**

- Quick Align allows users to align objects or instances

- Full align is done in 1 click and 1 double click

■ Relative align is done in 2 clicks

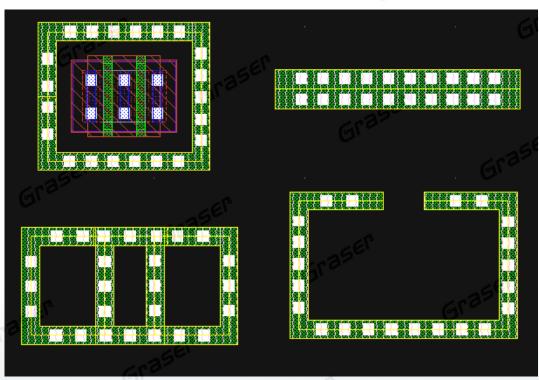

#### **Create Guard Ring**

- Easy to customize the Guard Ring

- It can be created by four different ways: by drawing a path, rectangle, or polygon, or by using the wrap mode

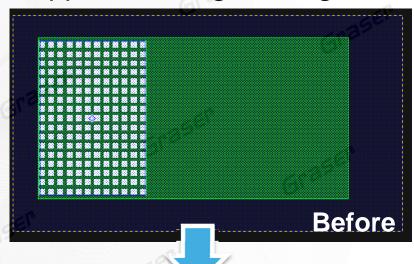

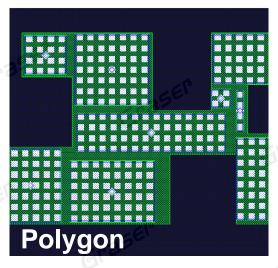

#### **Create Via**

- Supports polygonal shapes

- Autovia can fill a shape which already contains vias

- Supports 45 degree/diagonal shapes with below variables

|              | <b></b>                                       |                                        |

|--------------|-----------------------------------------------|----------------------------------------|

|              | 82888                                         |                                        |

| ស្សស្សស្សស   |                                               |                                        |

| 82222222     |                                               |                                        |

| 88888888     | 8 8 8 8 8                                     |                                        |

| 00000000     | 3 20 0 0 0                                    |                                        |

| 88888888     |                                               | Control Control                        |

| ងផុយផ្យួយប្រ | ប្សសស្ស                                       |                                        |

| 2828288      | 88888                                         | I'm less for was less for              |

| 8282828      | ២១៦១៦                                         |                                        |

|              |                                               | 0828888                                |

|              |                                               | 888888                                 |

| ODODDED      |                                               | 8 8 8 8 8 8 8                          |

| OODEEE       | <i>v,,,,,,,</i> ,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | <b>医性的的口的口</b>                         |

| <b>88888</b> |                                               | ស្តេសាធិស្តេស                          |

|              |                                               | 8 8 8 8 8 8 8                          |

|              |                                               | 8282828                                |

| <b>766</b>   |                                               | 网络四级短级短                                |

|              | 物解物館物                                         |                                        |

| Diagona      | ខែ៦៩៦៩                                        | 8 2 2 2 2 2 2 2                        |

|              |                                               | X///////////////////////////////////// |

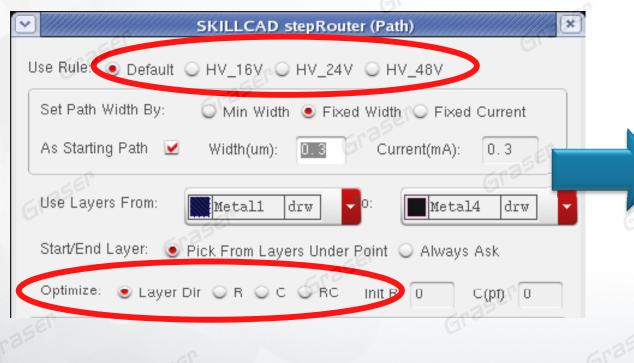

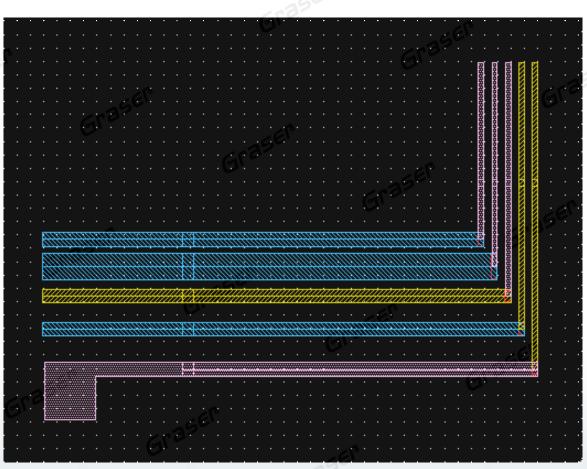

#### **Step Router**

Easy to choose rules

Optimize auto-connections according to

Layer direction

Optimized RC effect

### **Step Router**

- Auto Tap the Width

- Auto change layer, snap pin & add vias

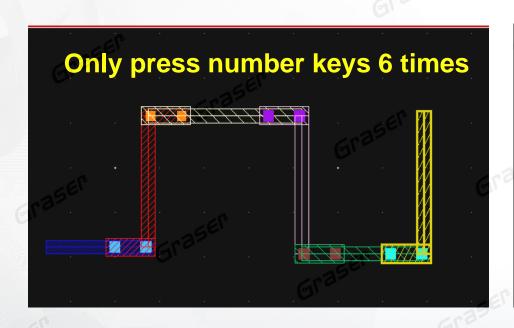

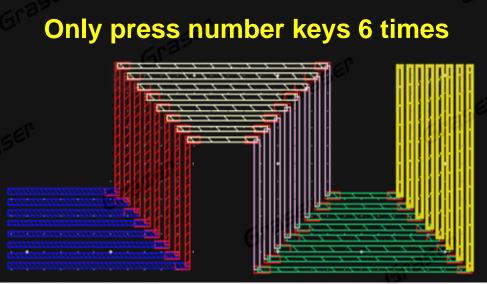

### **Free Jumper**

- Use number keys to change the layer what you want to route

- Add double via automatically

- Flexible via corner align style

#### **Bus Joint**

- Connected wire by user selection

- Auto change routing layers and add vias

- Easy to reverse order

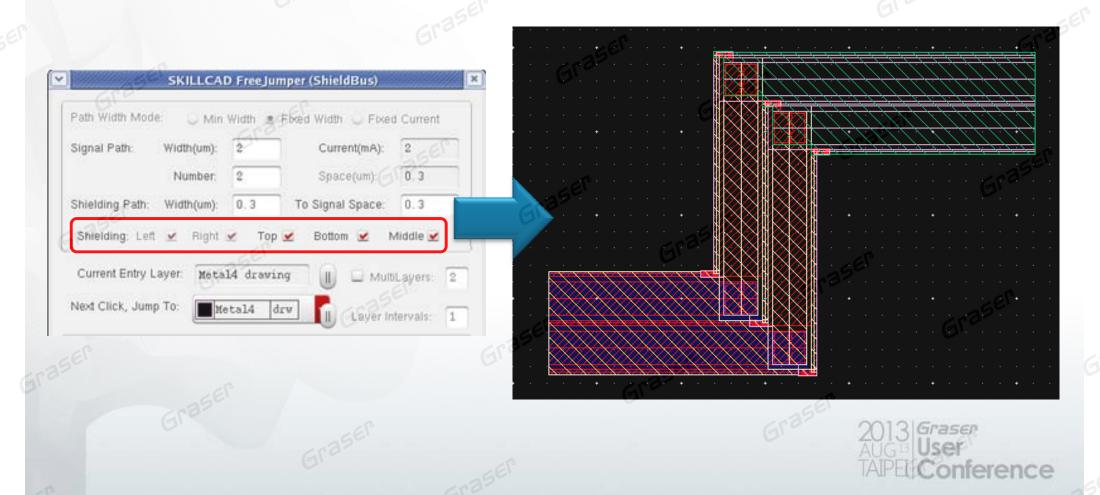

#### **Shield Bus**

- User-defined width / spacing of shielding path

- Number key to change connecting layers

- Auto-Via

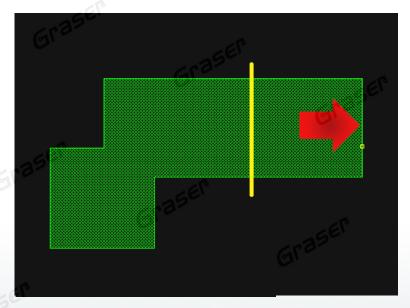

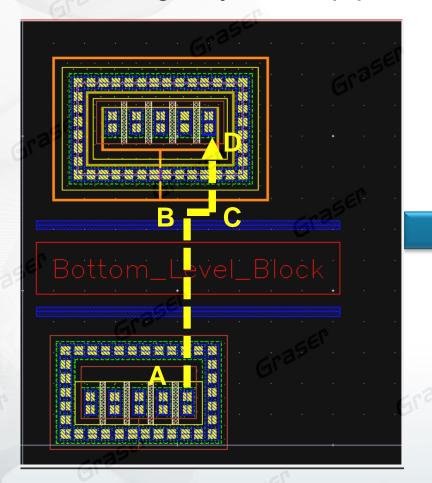

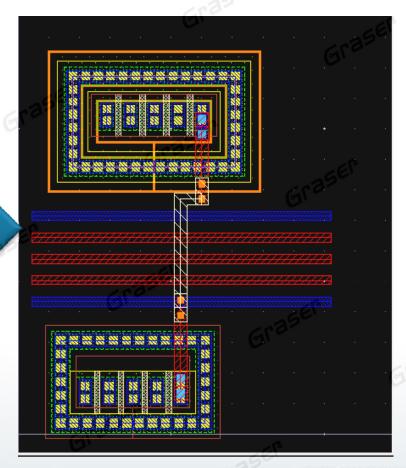

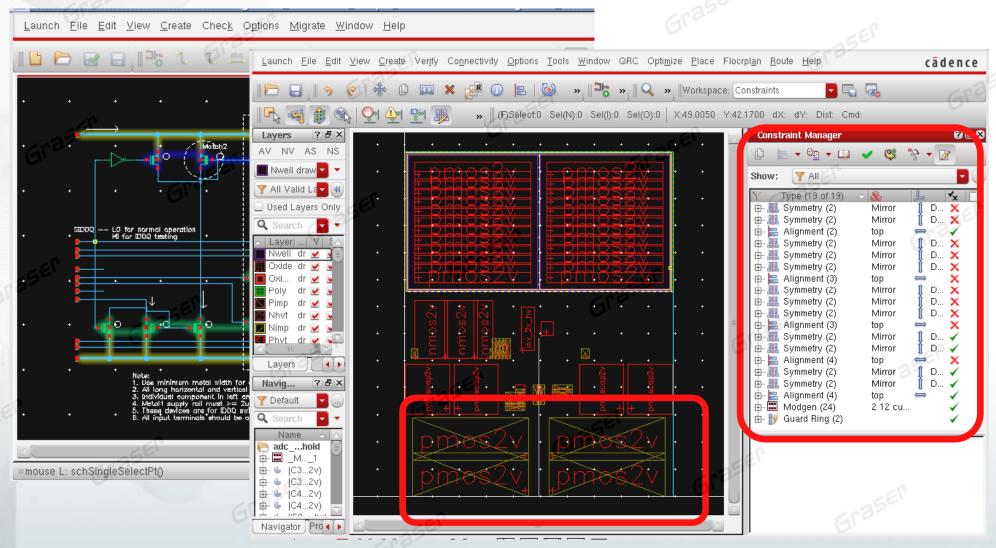

### **Constraint Driven & Generate From Source**

### **Layout Driven**

- Constraint Driven

- Make Circuit Designers closer to Layout Engineers

- Common constraint environment to ensure correct-by-construction layout

- Higher productivity, and fewer physical verification iterations

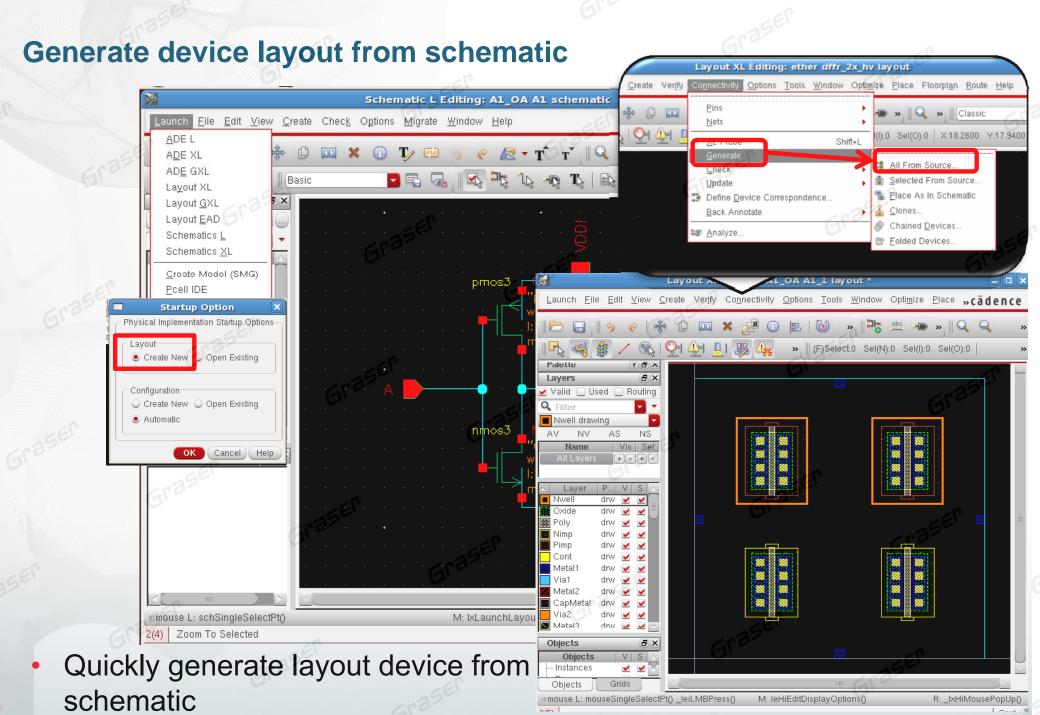

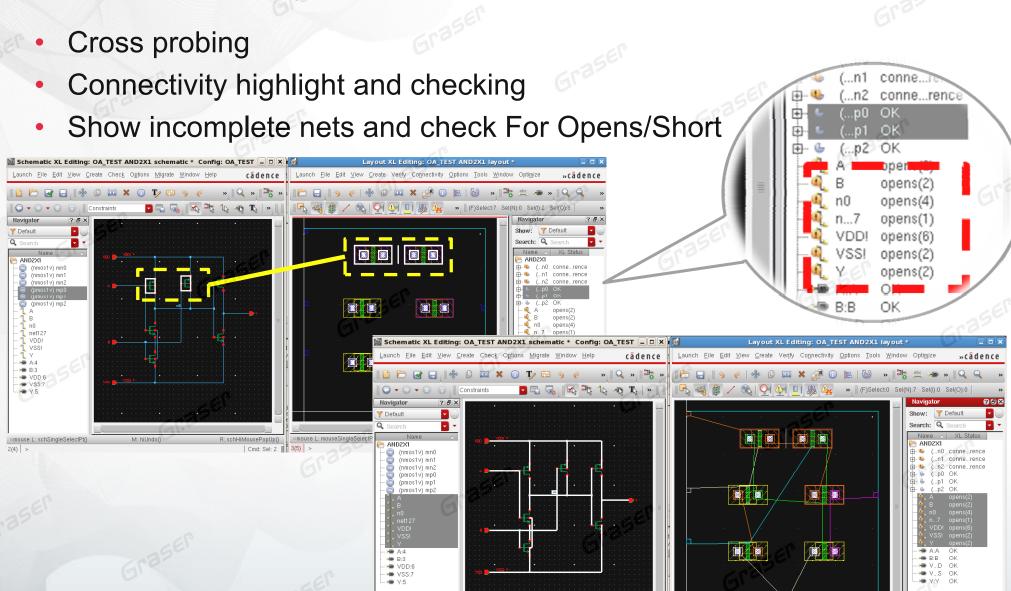

- Generate From Source (GFS)

- Quickly generate layout device from schematic

- Directly get Device type \ Parameter from schematic

- Connectivity Highlight and Checking

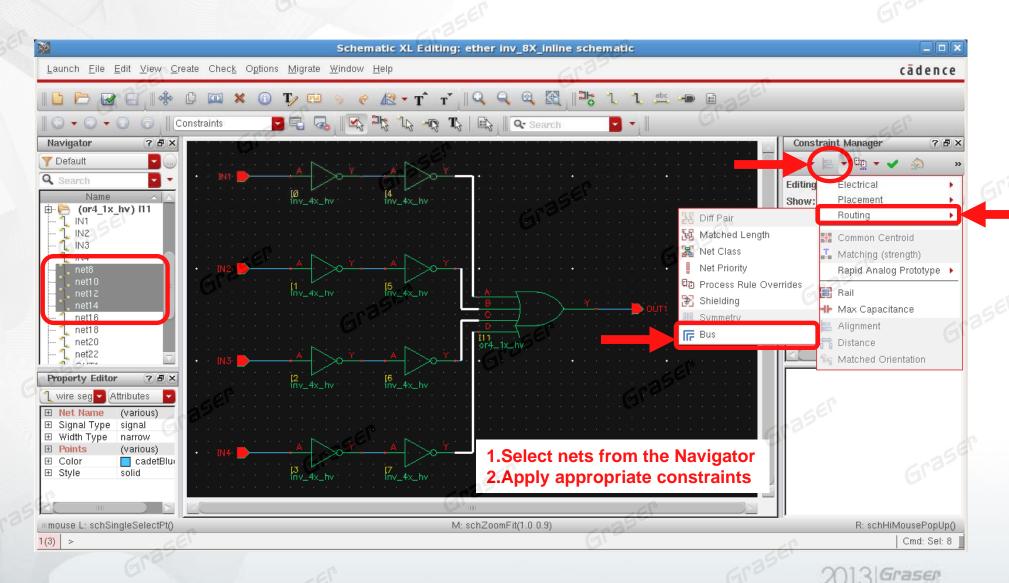

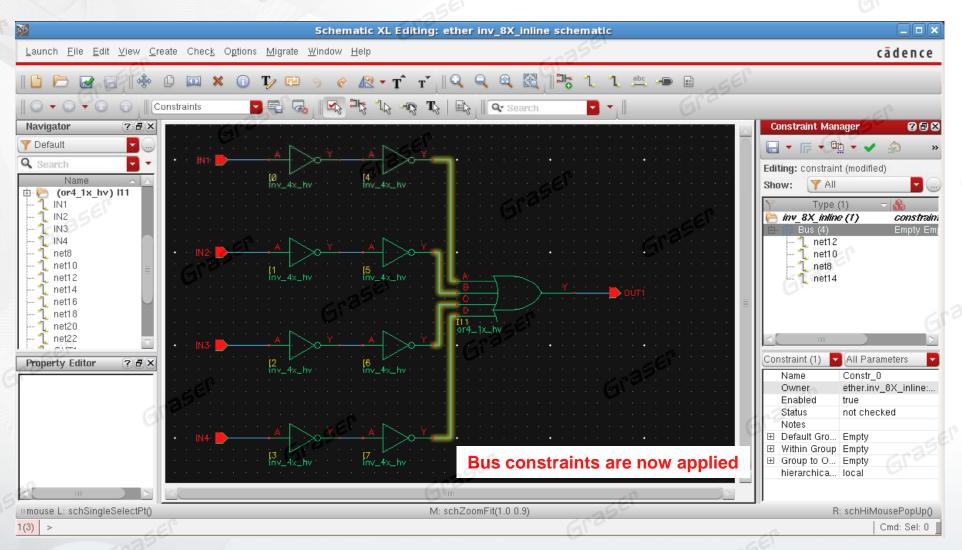

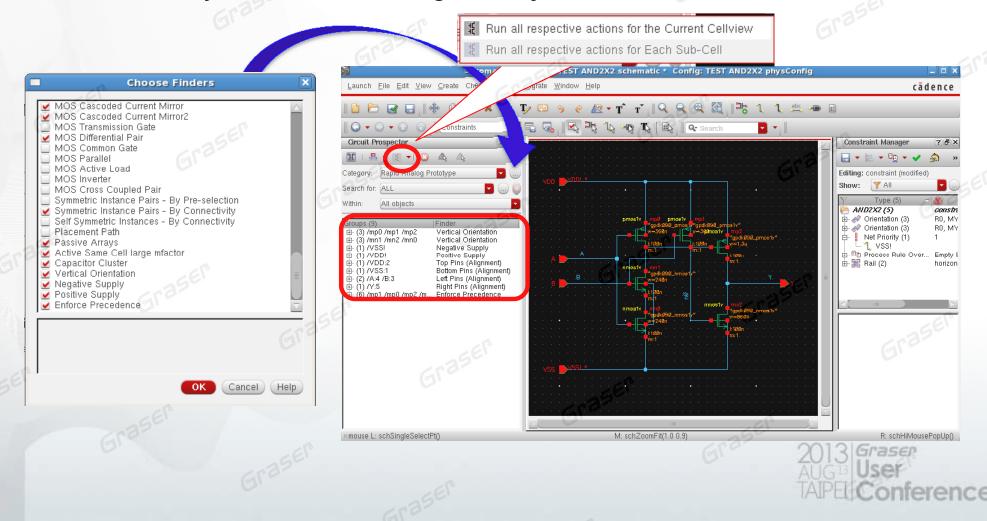

### **Constraints Setting in the Schematic**

### **Setting Constraints in the Schematic**

#### **Automatic Constraint Generators**

Single Rapid Analog Prototype(RAP) Category in the Circuit Prospector containing all the finders/generators required to automatically constrain a design with just a few mouse clicks

### **Constraint Manager**

Common constraint environment to ensure correct-by-construction layout

### **Generate From Source**

### **Generate From Source**

### **Generate device layout from schematic**

### Summary

- Integration with Virtuoso front-to-back custom & analog solution

- Virtuoso is New, fast, easy-to-learn, easy-to-use for design

- Virtuoso Schematic Editor speeds up the largest and most complex custom designs

- Virtuoso ADE is the direct access to MMSIM to realize your silicon

- Virtuoso Layout Suite speeds custom designs to the market

- Quick placement, routing and editing

- Reduce DRC and LVS errors

- Enhance the productivity and efficiency of layout

- Reduces a risk by maintaining design intent between design specification and implementation with unified common constraint environment