一篇發佈於 SemiWiki.com 的文章分享 Sigrity PowerTree 特性如何幫助設計人員在設計週期中儘早快速評估供電決定,加速 PCB 電源及訊號完整性簽核。

在複雜 SOC 片上系統管理電源網路十分複雜,這促進了電源格式 檔描述的發展,從而為功能分析和電氣分析存儲資料(如CPF、UPF等)。然而,對於複雜的印刷電路板,情況是怎樣的呢?電源網路的資訊如何得到有效體現(一塊或多塊板)、並存儲下來用作後續的分析?電氣分析如何有效融入 PCB 設計、減少 PCB 優化的時間?PCB 電源格式資訊如何能被自動提取、並傳遞到模擬?

具體來說,對於複雜的電源分配網路 (PDN),加速電源完整性分析過程中的主要問題有:

PDN 連接關係難以視覺化,因為它被嵌入在電路圖的細節中 |

|

在設計階段,需要對 PDN 和元件模型庫進行有效的管理,使得在不同版本的 PDN 設計中,可以很快進行對比、高亮出差異 |

|

需要支援佈局前的類比,來說明識別佈局前的錯誤 |

|

模擬的設置很麻煩 |

Cisco 近期分享了一個關於電源網路拓撲的實例,來自於他們的最新產品——包括約 20 組電源,約 250 個元件,以及近 500 個電源網路(包括濾波器件周圍的網路)。具體來說,系統級電路板的設計包括使用多樣的元器件類型,來滿足 I*R (DC直流) 電源壓降和電源阻抗特性需求(基於頻域的交流 AC 阻抗需要考慮最優去耦電容的大小和位置)。

我最近有機會跟 Brad Griffin 進行了交談,他是 Cadence Custom IC & PCB Group 的產品總監。Brad 描述了Cadence 是如何幫助客戶,實現將 PI 分析引入設計流程中。

「 在 Cisco 等客戶的幫助下,我們開發了新的功能用於 Sigrity 電源完整性和 OptimizePI。PowerTree 的存儲是一個獨特的方法,可用于生成並圖形化地顯示複雜電路板設計資訊及相關元器件模型及約束。 」

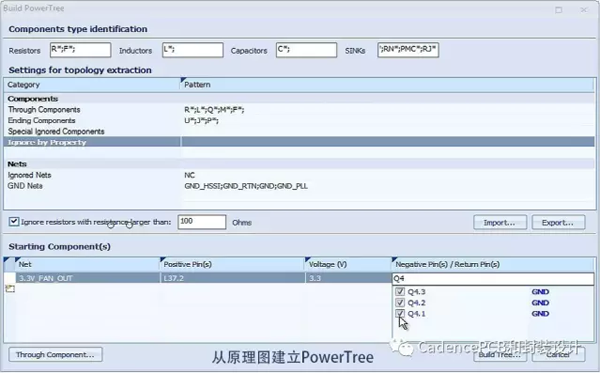

PowerTree 的配置很直觀——如下為「 建立 PowerTree 」對話方塊的截圖。

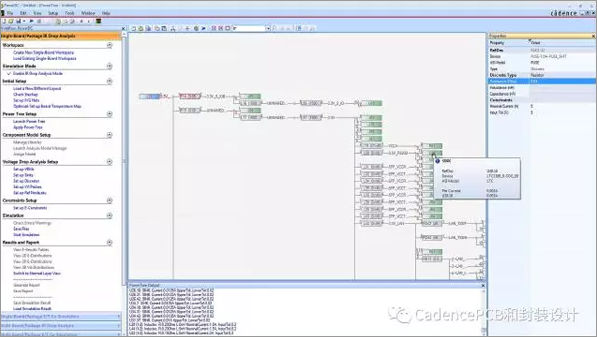

如下為一個複雜 PDN 的 PowerTree 應用的截圖。

元器件清單和連接網表都來自 Cadence Allegro。一個簡單的 PowerTree 視圖就可以包括大量電路圖頁面的電源網路資訊。元器件模型提供了電氣行為和驗證檢查約束。設計工程師可以在 PowerTree 中加入額外的設計約束和元器件模型資料。Brad 強調:

「 通過 PowerTree 環境,在 Sigrity PowerDC 中 PCB 設計工程師可以快速在電路圖和 PCB 佈局佈線過程中生成和運行 DC 分析模擬,優化 DC 之後,將設計提供給電源完整性專家,進行去耦電容選擇和放置,來優化頻域電源阻抗。PI 專家收到了更高品質的設計,可以使用 Sigrity OptimizePI 來展開工作。 」

Brad 和我都知道電源完整性專家是非常寶貴的資源,他們經常工作負擔過重。PCB 設計工程師可以使用 Sigrity PowerTree 的特性,快速提取電源拓撲結構以及元器件資料,進行模擬來保證提供 PCB 的 DC 需求,這將大大提高PI分析工作效率。

文章出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」